Элементы и узлы ЭВМ. Ч. 1 (120

.pdfМосковский государственный технический университет имени Н.Э. Баумана

В.И. Виноградов, С.Б. Спиридонов, А.В. Шигин

ЭЛЕМЕНТЫ И УЗЛЫ ЭВМ

Методические указания к лабораторному практикуму по курсу

«Элементы и узлы ЭВМ»

Часть 1

Москва

Издательство МГТУ им. Н.Э. Баумана

2009

УДК 621.3.038 ББК 32.973

В49

Р е ц е н з е н т М.В. Мурашов

Виноградов В.И.

В49 Элементы и узлы ЭВМ : метод. указания к лабораторному практикуму по курсу «Элементы и узлы ЭВМ». — Ч. 1 / В.И. Виноградов, С.Б. Спиридонов, А.В. Шигин. — М.: Изд-во МГТУ им. Н.Э. Баумана, 2009. — 12 с. : ил.

Приведены задания для выполнения двух лабораторных работ по курсу «Элементы и узлы ЭВМ». Даны краткие пояснения по применению программного комплекса Electronics Workbench.

Для студентов 2-го курса специальности «Системы обработки информации и управления» факультета «Информатика и системы управления».

УДК 621.3.038 ББК 32.973

Учебное издание

Виноградов Валерий Иванович Спиридонов Сергей Борисович Шигин Анатолий Васильевич

ЭЛЕМЕНТЫ И УЗЛЫ ЭВМ Часть 1

Редактор С.А. Серебрякова Корректор Е.К. Кошелева

Компьютерная верстка С.А. Серебряковой

Подписано в печать 17.11.2009. Формат 60×84/16. |

|

Усл. печ. л. 0,70. Тираж 100 экз. Изд. № 162. Заказ |

. |

Издательство МГТУ им. Н.Э. Баумана. |

|

Типография МГТУ им. Н.Э. Баумана. |

|

105005, Москва, 2-я Бауманская ул., 5. |

|

© МГТУ им. Н.Э. Баумана, 2009

Работа № 1. МОДЕЛИРОВАНИЕ РАБОТЫ СУММАТОРОВ С ПОМОЩЬЮ ПРОГРАММНОГО КОМПЛЕКСА ELECTRONICS WORKBENCH

Цель работы — ознакомление c возможностями моделирования работы схем сумматоров, исследование сумматоров, универсального сумматора-вычитателя, инкременторов и декременторов.

Продолжительность работы — 4 часа.

1. Теоретическая часть

Сумматор — это электронное устройство, выполняющее арифметическое сложение кодов двух чисел. Сумматоры применяют и для выполнения операции вычитания, но для этого необходимо осуществлять дополнительные преобразования кодов чисел.

В зависимости от системы счисления различают следующие сумматоры:

–двоичные;

–двоично-десятичные;

–десятичные;

–другие.

По количеству одновременно обрабатываемых разрядов складываемых чисел сумматоры бывают:

–одноразрядные;

–многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров различают:

– четвертьсумматоры (элементы «сумма по модулю 2», т. е. «исключающее ИЛИ»), имеющие два входа для двух одноразрядных чисел и один выход, на котором осуществляется их арифметическое суммирование;

3

–полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноименные разряды двух чисел, и двух выходов: на одном реализуется арифметическое суммирование в данном разряде, а на другом — перенос в следующий (более старший) разряд;

–полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и сигнал переноса из предыдущего (более младшего) разряда, и двух выходов: на одном реализуется арифметическое суммирование в данном разряде, а на другом — перенос в следующий (более старший) разряд.

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяют следующим образом:

–последовательные, в которых обработка чисел ведется поочередно, разряд за разрядом, на одном и том же оборудовании;

–параллельные, в которых слагаемые складываются одновременно по всем разрядам и для каждого разряда имеется свое оборудование.

Параллельный сумматор в простейшем случае представляет собой n одноразрядных сумматоров, последовательно соединенных цепями переноса.

По способу выполнения операции сложения выделяют два типа сумматоров:

– комбинационный сумматор, выполняющий микрооперацию s = a + b, в котором результат выдается по мере его образования;

– накапливающий сумматор, на вход которого операнды подаются последовательно с некоторой задержкой.

2. Элементы программного комплекса Electronics Workbench, используемые в работе

При проведении лабораторной работы используются следующие элементы комплекса:

–Voltage Source — источник постоянного напряжения +5 В.

Спомощью этого источника на вход триггеров и логических элементов подается логическая единица;

–переключатель (Basic →Switch). Переключение осуществляется нажатием на клавишу, указанную в скобках над этим элементом;

4

–логический элемент «И» (Logic gates → 2-Input AND gate);

–логический элемент «исключающее ИЛИ» (Logic gates → 2-Input NOR gate);

–световой индикатор (Indicators → red Prob). При подаче на этот элемент логической единицы светодиод загорается красным цветом;

–семисегментный цифровой индикатор;

–одноразрядный полусумматор (Half-Adder);

–одноразрядный полный сумматор (Full-adder).

3.Задание на выполнение лабораторной работы

1.Исследовать работу одноразрядного полусумматора по таблице истинности (табл. 1), в которой введены следующие обозначения: a — первое одноразрядное слагаемое; b — второе одноразрядное слагаемое; p — сигнал переноса; s — сумма.

|

|

|

Таблица 1 |

|

|

|

|

a |

b |

p |

s |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

Собрать одноразрядный полусумматор на элементах «исключающее ИЛИ» и «И».

Повторить исследование, используя библиотечный полусумматор (рис. 1). Подробное описание такого сумматора приведено в методических указаниях к выполнению лабораторной работы «Ознакомление с программным комплексом Electronics Workbench» (текст размещен на сайте кафедры).

Для одновременной подачи двух чисел нужно предусмотреть управление двумя группами выключателей: для установки кодов данного разряда и для последовательной подачи разрядов на вход полусумматора.

5

Рис. 1. Библиотечный полусумматор

2. Исследовать работу полного одноразрядного сумматора по таблице истинности (табл. 2), в которой введены следующие обозначения: a — первое одноразрядное слагаемое; b — второе одноразрядное слагаемое; p — сигнал входного переноса; P — сигнал выходного переноса; s — сумма.

|

|

|

|

Таблица 2 |

|

|

|

|

|

a |

b |

p |

P |

s |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

1 |

1 |

0 |

1 |

0 |

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

Собрать схему полного сумматора из двух полусумматоров. Повторить исследование с библиотечным полным сумматором. 3. Собрать четырехразрядный параллельный сумматор и ис-

следовать его работу.

Для одновременной подачи кодов двух слагаемых использовать группы выключателей установки кода первого слагаемого и группы выключателей установки кода второго слагаемого.

6

4.Собрать четырехразрядный параллельный сумматор и исследовать его работу для вычитания чисел.

Для этого подать разряды слагаемого в обратном коде и построить цепь кругового переноса с выхода сумматора старшего разряда на вход младшего разряда.

5.Проверить работу сумматора при сложении и вычитании нескольких пар четырехразрядных чисел.

6.Собрать трехразрядные схемы инкрементора и декрементора. Продемонстрировать работу собранных схем.

Число, подаваемое на вход инкрементора, на его выходе должно увеличиться на единицу.

4.Задание для самостоятельной работы

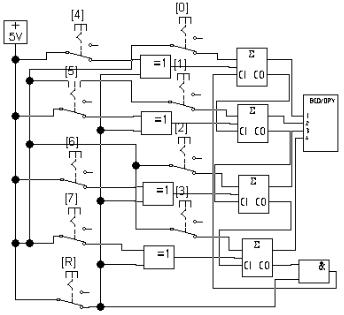

1.Собрать схему универсального сумматора-вычитателя и исследовать его работу в режимах сложения и вычитания (рис. 2, также см. методические указания к выполнению лабораторной работы «Ознакомление с программным комплексом Electronics Workbench», размещенные на сайте кафедры).

2.Объяснить назначение логических элементов «исключающее ИЛИ» в схеме универсального сумматора-вычитателя.

5. Содержание отчета

Отчет о работе должен содержать схемы сумматоров, собранные в ходе лабораторной работы, пояснения, касающиеся режимов работы универсального сумматора-вычитателя.

6.Контрольные вопросы

1.Каково назначение входа и выхода переноса в полных сумматорах?

2.Как выполняется операция вычитания с использованием сумматоров?

3.Поясните на примерах принцип работы сумматоров дополнительного и обратного кодов.

4.Какие технические решения позволяют ускорить работу комбинационных сумматоров?

7

Рис. 2. Универсальный сумматор-вычитатель

Работа № 2. МОДЕЛИРОВАНИЕ РАБОТЫ АРИФМЕТИКО-ЛОГИЧЕСКОГО УСТРОЙСТВА С ПОМОЩЬЮ ПРОГРАММНОГО КОМПЛЕКСА ELECTRONICS WORKBENCH

Цель работы — ознакомление c возможностями моделирования работы арифметико-логического устройства (АЛУ); исследование работы АЛУ на примере выполнения арифметических и логических операций.

Продолжительность работы — 4 часа.

1. Основные понятия

Арифметико-логическое устройство предназначено для выполнения арифметических и логических операций над многоразряд-

8

ными операндами в зависимости от кодов, подаваемых на управляющие входы.

Ввычислительных устройствах АЛУ является базовым узлом и работает в сочетании с оперативным запоминающим устройством, регистрами сдвига, регистрами общего назначения и др. Микросхемы АЛУ, принадлежащие к разным видам логик, функционально во многом совпадают.

Аналогом микросхемы К155ИП3 в программном комплексе Electronics Workbench служит микросхема 74181. Она представляет собой четырехразрядное АЛУ, которое работает в режиме выполнения логических операций при значении управляющего сигнала М = 1 и в режиме выполнения арифметических операций при значении управляющего сигнала М = 0.

Втабл. 3 приведен перечень логических и арифметических операций, выполняемых в зависимости от кодовой комбинации на управляющих входах S0, S1, S2, S3.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Логическая |

|

|

|

|

Арифметико-логическая |

|||||||||||||||||||||||||

S3 |

S2 |

S1 |

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

функция М = 0, C = 1 |

||||||||||||||||||||||||||||||

функция М = 1 |

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

(входной перенос отсутствует) |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

A или А – 1 (при входном переносе) |

|||||||||||||||||||

|

A |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

AB или AB – 1 |

|||||||||||||||||||

|

AB |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A + B |

AB или AB −1 |

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

–1 или 0 (при входном переносе) |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

|

A + B |

A + ( A + B) или A + ( A + B) +1 |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

AB + ( A + B) или AB + ( A + B) +1 |

|||||||||||||||||||

|

B |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

A – B – 1 или A – B |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

( A + B) |

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

A + B или ( A + B) +1 |

|||||||||||||||||||

|

A + B |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

A + A + B или A + (A + B) + 1 |

|||||||||||||||||||

|

AB |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

A + B или A + B + 1 |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

( A + B) |

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

1 |

0 |

1 |

0 |

AB + ( A + B) или AB + ( A + B) +1 |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||

1 |

0 |

1 |

1 |

A + B |

A + B или A + B + 1 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

A + A или A + A + 1 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Окончание табл. 3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Логическая |

|

|

Арифметико-логическая |

||||||

S3 |

S2 |

S1 |

S0 |

|

|

|

|

|

|

|

|||

|

|

функция М = 0, C = 1 |

|||||||||||

функция М = 1 |

|

|

|||||||||||

|

|

|

|

|

(входной перенос отсутствует) |

||||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||

1 |

1 |

0 |

1 |

|

|

|

AB + A или AB + A + 1 |

||||||

AB |

|||||||||||||

|

|

|

|

|

|

|

|

||||||

1 |

1 |

1 |

0 |

AB |

|

|

|

|

|

|

|

||

AB + A или AB + A +1 |

|||||||||||||

|

|

|

|

|

|

||||||||

1 |

1 |

1 |

1 |

A |

A или A + 1 |

||||||||

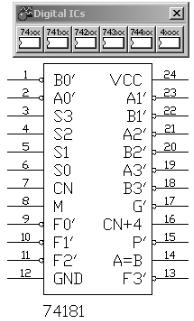

2. Элементы программного комплекса Electronics Workbench, используемые в работе

При проведении лабораторной работы используется четырехразрядное АЛУ, которое выбирается из множества схем 741хх на панели Digital ICs под номером 74181 (рис. 3). Описание схемы АЛУ приведено в методических указаниях к выполнению лабораторной работы «Ознакомление с программным комплексом Electronics Workbench» (размещены на

сайте кафедры).

3. Задание на выполнение |

||||

лабораторной работы |

||||

1. Подготовить |

микросхему |

|||

АЛУ на рабочем столе. |

|

|||

Подготовить четыре переклю- |

||||

чателя |

для |

задания |

режимов |

|

управления. Сигналы S подаются |

||||

на входы S0, …, S3 АЛУ. Пятый |

||||

переключатель |

используется для |

|||

задания |

режима М. Логическая |

|||

единица |

подается |

на |

все пере- |

|

ключатели от источника постоянного напряжения 5 В, логический

Рис. 3. Микросхема АЛУ |

нуль — от элемента заземления. |

|

10