- •Электроника

- •Содержание

- •Раздел 1. Элементы электронной техники

- •Раздел 2.Истчники электропитания

- •Раздел3. Аналоговые интегральные микросхемы

- •Раздел 4. Цифровые интегральные микросхемы

- •Раздел 5. Фотоэлектрические приборы

- •Раздел 6. Аналого-цифровые функциональные устройства

- •Раздел 7. Микроконтроллеры

- •Раздел 1

- •1.Пассивные элементы электрических цепей

- •1.1 Резисторы

- •1.2 Конденсаторы

- •1.3 Индуктивности

- •1.4 Трансформаторы

- •2. Диоды

- •2.1 Принцип работы диода

- •Вольт-амперная характеристика диода

- •4. Стабилитроны и стабисторы.

- •2.2 Выпрямительные диоды

- •2.3 Высокочастотные диоды

- •2.4 Импульсные диоды

- •2.5 Стабилитроны и стабисторы

- •3. Биполярные транзисторы

- •3.1 Общие принципы

- •3.2 Основные параметры транзисторов

- •3.3 Схемы включения транзисторов

- •3.4 Ключевой режим работы транзистора

- •3.5 Усилительный режим работы транзистора

- •3.5 Способы задания рабочей точки по постоянному току в усилительном режиме

- •3.6 Схема включения транзистора с общим коллектором

- •4. Полевые (униполярные) транзисторы

- •4.1 Полевой транзистор с p-n переходом

- •Входные и выходные характеристики полевого транзистора с p-n переходом и каналом n-типа

- •4.2 Полевые транзисторы с встроенным каналом

- •Входные и выходные характеристики моп - транзистора с встроенным каналом n -типа (кп 305)

- •4.3 Полевые транзисторы с индуцированным каналом

- •Крутизна

- •Особенности полевых моп транзисторов

- •4.4 Igbt транзистор

- •Режимы работы каналов и полярности электродных напряжений полевых транзисторов

- •5. Генераторы электрических сигналов

- •5.1 Принципы построения генераторов.

- •5.2 Генераторы гармонических сигналов.

- •5.3 Генераторы импульсов на логических элементах ттл и таймере 555 (кр1006ви).

- •6. Силовые полупроводниковые приборы

- •6.1 Динисторы.

- •6.2 Тиристор.

- •6.3 Симисторы

- •6.4 Igbt транзистор

- •Раздел 2

- •7. Источники питания

- •7.1 Однофазный мостовой выпрямитель

- •7.2Стабилизаторы напряжения

- •7.2.1 Параметрические стабилизаторы напряжения

- •Раздел 4

- •8. Аналоговые микросхемы.

- •8.1 Свойства оу

- •Практическая трактовка свойств оу

- •8.2 Основы схемотехники оу

- •Входной дифференциальный каскад

- •Современный входной дифференциальный каскад

- •8.3 Параметры операционных усилителей

- •8.4 Принцип отрицательной обратной связи

- •8.5 Основные схемы включения оу. Инвертирующее включение

- •Применение инвертирующего усилителя в качестве интегратора

- •Неинвертирующее включение

- •Ограничитель сигнала

- •8.6 Компараторы

- •8.7 Триггер Шмитта

- •8.8 Схема мультивибратора

- •8.9 Активные фильтры

- •Фильтр нч первого порядка

- •Раздел 4 Цифровые интегральные микросхемы

- •9. Цифровые интегральные микросхемы

- •Основные понятия

- •9.2 Обозначение и типы комбинационных логических микросхем

- •9.3 Структура ттл логических микросхем

- •Основные параметры логических ттл элементов

- •9.4 Микросхемы последовательного тип

- •9.4.1 Интегральные триггеры

- •9.4.2 Rs асинхронный триггер

- •9.4.3 Асинхронный d - триггер

- •9.4.4 Синхронный d - триггер со статическим управлением

- •9.4.5 Синхронный d -триггер с динамическим управлением

- •9.4.6 Синхронный jk - триггер

- •9.4. 8. Вспомогательные схемы для триггеров

- •9.4.9 Формирователь импульса

- •Мультиплексоры и демультиплексоры

- •Шифраторы, дешифраторы и преобразователи кодов

- •Счётчики импульсов

- •Регистры

- •Раздел 5 Фотоэлектронные приборы

- •2. Отоэлектрические приборы.

- •10.1 Понятия о оптоэлектронных приборах

- •10.2 Элементы оптоэлектроники.

- •Раздел 6

- •11. Аналого-цифровые преобразователи

- •Основные характеристики интегрирующих ацп

- •12. Цифро-аналоговые преобразователи

- •Характеристики интегральных микросхем цап

- •Раздел 7

- •13. Микропроцессоры

- •13.1 Cisc--процессоры

- •13.2 Risc—процессоры

- •14. Компьютерное моделирование электронных устройств

- •15. Используемая литература

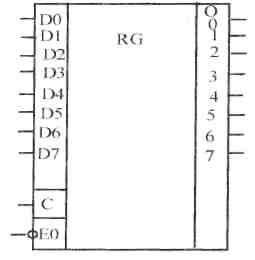

Регистры

Регистрами называют функциональные узлы, предназначенные для приёма, хранения, передачи и преобразования информации. В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно-последовательные регистры. Параллельные регистры. В параллельных регистрах запись двоичного числа (слова) осуществляется параллельным кодом, т. е. во все разряды регистра одновременно. Их функция сводится только к приёму, хранению и передаче информации (двоичного числа).

Считывание кода из регистра может производиться многократно без разрушения информации. Параллельный N-разрядный регистр состоит из N-триггеров, каждый из которых имеет информационный вход, на которые и подаётся входная информация. Установка выходов регистра в состояния, соответствующие состояниям информационных входов, производится при воздействии импульса синхронизации (тактирующего) на соответствующий управляющий вход. Регистры могут иметь отдельный управляющий вход переустановки выходных состояний в нулевое значение («R», переустановка, обнуление).

При построении параллельных регистров наибольшее применение получили D‑триггеры (триггер-«защёлка»), позволяющие выполнять параллельные регистры на малом количестве элементов. Полупроводниковая элементная база, выпускаемая электронной промышленностью, имеет в своём составе многоразрядные параллельные регистры (рисунок 15.1) или позволяет изготавливать их на интегральных схемах малой степени интеграции.

Входы |

Выходы |

||

|

С |

D |

O |

0 |

1 |

1 |

1 |

0 |

I |

0 |

0 |

0 |

0 |

X |

Q0 |

1 |

X |

X |

Z |

1533ИРЗЗ 8-разрядный параллельный регистр на D-триггерах

Таблица состояний

Рис.108 - Многоразрядный параллельный регистр с Z-состоянием

Такие регистры (например, ИС 1533ИР22, ИРЗЗ, ИР34) могут использоваться в качестве:

регистра памяти;

буферного регистра, способного работать на низкоомные нагрузки (20-100 Ом) и большие ёмкости нагрузки (до 50 пФ и более);

- регистра ввода-вывода и магистрального передатчика, что обеспечено наличием в них режима большого выходного сопротивления («третье состояние», «Z-состояние»), за счёт чего они физически всегда подключены к линиям шин магистрали микропроцессорной системы через сопротивления порядка не скольких мегаом. А передача информации происходит только во время действия управляющего импульса (вход ЕО на рисунке 15.1), когда управляющее устройство выводит регистр из Z-состояния.

Параллельные регистры имеются и в составе серий современных скоростных микромощных ИС (серии 1554, 1594, 5514 и 5554). Параметры таких регистров определяются параметрами D-триггеров, входящих в их состав. Это параметры, которые важно знать и при самостоятельном применении D-триггеров:

время предустановки tПРУСТ показывает, насколько ранее должен быть подан сигнал на D-вход относительно момента поступления сигнала на на вход С;

время удержания tУД отражает время удержания сигнала на D-входе после момента прихода сигнала на С-вход.

Последовательные регистры (регистры сдвига). Характеризуются записью числа последовательным кодом и, кроме операции хранения, осуществляют преобразование последовательного кода в параллельный, служат в качестве элементов временной задержки, выполняют арифметические и логические операции. Регистр состоит из последовательно соединенных ячеек памяти, состояния которых передаются (сдвигаются) на последующие ячейки под действием тактовых импульсов. Однотактные регистры сдвига выполняют по функциональной схеме (рис.109), показанной для четырех разрядов.

Рис.109 - Последовательный 4-разрядный однотактный регистр

Тактовые импульсы управляют работой

регистра. Регистры сдвига могут

управляться одной последовательностью

тактовых импульсов. В этом случае

регистры называют однотактными.

Частота следования тактовых импульсов

обычно неизменна. В многотактных

регистрах последовательности тактовых

импульсов следуют с взаимным фазовым

сдвигом

![]() ,

где т - количество последовательностей

тактовых импульсов. Наиболее простая

реализация регистра сдвига использует

последовательное соединение

D-триггеров таким образом,

чтобы для некоторого n-го

разряда выполнялось условие:

,

где т - количество последовательностей

тактовых импульсов. Наиболее простая

реализация регистра сдвига использует

последовательное соединение

D-триггеров таким образом,

чтобы для некоторого n-го

разряда выполнялось условие:

![]() ;

;

![]() .

.

Первая ячейка регистра относится к его младшему разряду, а четвертая - к старшему. При таком расположении разрядов запись числа в регистр производится начиная со старшего разряда числа. При обратном расположении разрядов в регистре запись числа должна начинаться с его младшего разряда. Тактовые импульсы подаются на все триггеры ячеек одновременно. Их воздействие направлено на переключение триггеров из состояния «1» в состояние «0» с записью единицы в триггер следующей ячейки.

Операция считывания информации из последовательного регистра может быть проведена в параллельном или последовательном коде. Для передачи информации в параллельном коде используют выходы разрядов регистра. Таким образом, последовательный регистр позволяет осуществить операцию преобразования последовательного кода в параллельный. Считывание информации в последовательном коде реализуется подачей серии тактовых импульсов.

В последовательном регистре записанное

число может быть сдвинуто тактовыми

импульсами на один или несколько (k)

разрядов. Операции сдвига соответствуют

умножению числа на

![]() .

Например, сдвиг кода 0010 числа 2 на

один разряд дает код 0100 (число 4), на

два разряда - код 1000 (число 8).

.

Например, сдвиг кода 0010 числа 2 на

один разряд дает код 0100 (число 4), на

два разряда - код 1000 (число 8).

При построении модулей памяти на

однотактных регистрах сдвига необходимо

учитывать, что тактовые импульсы

воздействуют на перевод в состояние

«0» триггеров всех разрядов одновременно.

Поэтому в однотактных регистрах должна

быть решена задача разделения во времени

(по меньшей мере на длительность тактовых

импульсов

![]() )

операций считывания единицы с триггера

каждого разряда и ее переписи в

триггер следующего разряда. В противном

случае перепись единицы в следующий

разряд не будет произведена.

)

операций считывания единицы с триггера

каждого разряда и ее переписи в

триггер следующего разряда. В противном

случае перепись единицы в следующий

разряд не будет произведена.

Эта задача может быть решена включением

в цепь передачи сигнала от одной ячейки

к другой элемента задержки. Элемент

задержки будет задерживать импульс

записи единицы в последующую ячейку на

время действия тактового импульса.

Однако наличие элементов задержки

обусловливает критичность работы схемы

в отношении длительности тактовых

импульсов. Кроме того, для элементов

задержки, состоящих из реактивных

элементов L и С, затруднено

интегральное исполнение. В связи с

указанным, разнесение во времени операций

считывания и переписи единицы

осуществляют схемными средствами,

например выполнением ячеек на триггерах

с внутренней задержкой (![]() ,

, ![]() ,

,

![]() -триггерах).

-триггерах).

Параллельно-последовательные и реверсивные регистры. В параллельно-последовательных регистрах сочетаются свойства регистров параллельного и последовательного действия. Они записывают информацию как в последовательном, так и параллельном коде, в связи с чем могут быть использованы для преобразования кодов из последовательного в параллельный и обратно. Эти регистры допускают однотактный (рис.110) и многотактный принципы построения.

Рис.110 - Параллельно-последовательный регистр

Для преобразования последовательного кода в параллельный серией тактовых импульсов в регистр записывается информация (число) последовательного кода. Выходы разрядов регистра при этом представляют ту же информацию в параллельном коде. Для обратного преобразования информация в регистр вводится по входам параллельного кода. Посредством серии тактовых импульсов с выхода последнего разряда регистра информация считывается в последовательном коде.

Реверсивные регистры предназначены для осуществления сдвига кода числа в сторону как старшего, так и младшего разрядов. Регистр содержит связи последовательной передачи информации в направлении от младших разрядов к старшим, а также от старших разрядов к младшим.

Прямой или обратный сдвиг кода осуществляют управляющим сигналом, вводящим в действие либо прямую, либо обратную связи между разрядами.