Организация базовой ЭВМ - СФ

.pdfМинистерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

Томский государственный университет систем управления и радиоэлектроники (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем

(КИБЭВС)

Организация базовой учебной ЭВМ Отчет по лабораторной работе по дисциплине “ Организация ЭВМ и вычислительных

систем”

Студент гр. ххххххх

__________ хххххххххххххх

__________

Преподаватель КИБЭВС

__________ __________ хххххххххх

__________

Томск 2021

2

1 Введение

Целью данной лабораторной работы является изучение структурной и функциональной

организации процессора на примере базовой учебной ЭВМ.

3

2 Ход работы

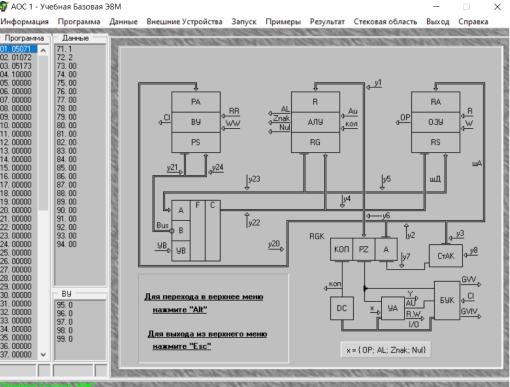

Для того чтобы выбрать вариант для начала нужно включить симулятор БУ ЭВМ

(рисунок 2.1). В качестве варианта был выбран пример 1, он также изображен на рисунке 2.1.

Рисунок 2.1 - AOC 1, пример 1

Цель данного алгоритма сложение нынешнего значения ячейки с предыдущим и запись результата в следующую ячейку.

1) 05071 - обмен между АЛУ и памятью системы (ОЗУ), АЛУ присваивается значение

“1”;

2)01072 – происходит сложение значений ОЗУ и АЛУ, к АЛУ присваивается значение ячейки 72 - “2”, т.е. АЛУ := 3;

3)05173 – происходит обмен значениями между ОЗУ и АЛУ, и ОЗУ (память системы)

присваивается значение АЛУ, и ячейке данных с индексом 73 присваивается значение 3; 4) 10000 – останов, прекращение работы.

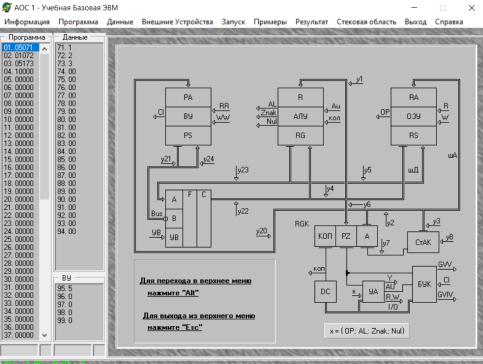

Результат работы программы показан на рисунке 2.2.

4

Рисунок 2.2 - Результат работы программы

3Заключение

Входе данной лабораторной работы были изучены структурные и функциональные организации процессора на примере базовой учебной ЭВМ.