еще лабы / LR5_Guseynov_A_Tkachev

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра ВТ

ОТЧЕТ

по лабораторной работе №5

по дисциплине «Узлы и устройства средств вычислительной техники»

Тема: Исследование регистров

Вариант №4

Студенты гр. 8307 |

|

Гусейнов А.Э. |

|

|

Ткачев И.Г. |

Преподаватель |

|

Буренева О.И. |

Санкт-Петербург

2021

Цель работы

Исследовать особенности проектирование регистров разного типа, закрепить навыки синтеза и экспериментального исследование узлов в среде Quartus II.

Основные теоретические положения

Регистры – это узлы последовательного типа, выполняющие операции приема, выдачи, хранения, сдвига, поразрядные логические операции.

По способу приема и выдачи данных регистры разделяют на

параллельные (статические): прием и выдача производятся по всем разрядам одновременно;

последовательные (сдвигающие): прием и выдача производятся по разрядно, перемещение слов по разрядной сетке происходит по тактовому сигналу;

параллельно-последовательные: имеют входы-выходы параллельного и последовательного типа.

В сдвигающих регистрах, не имеющих логических элементов межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры за время действия разрешающего уровня синхросигнала могут переключиться неоднократно, что недопустимо для последовательного соединения. Появление межразрядных связях логических элементов упрощает выполнение условий работоспособности регистров, при этом иногда становится возможным и применение простейших триггеров.

Синтез логической схемы

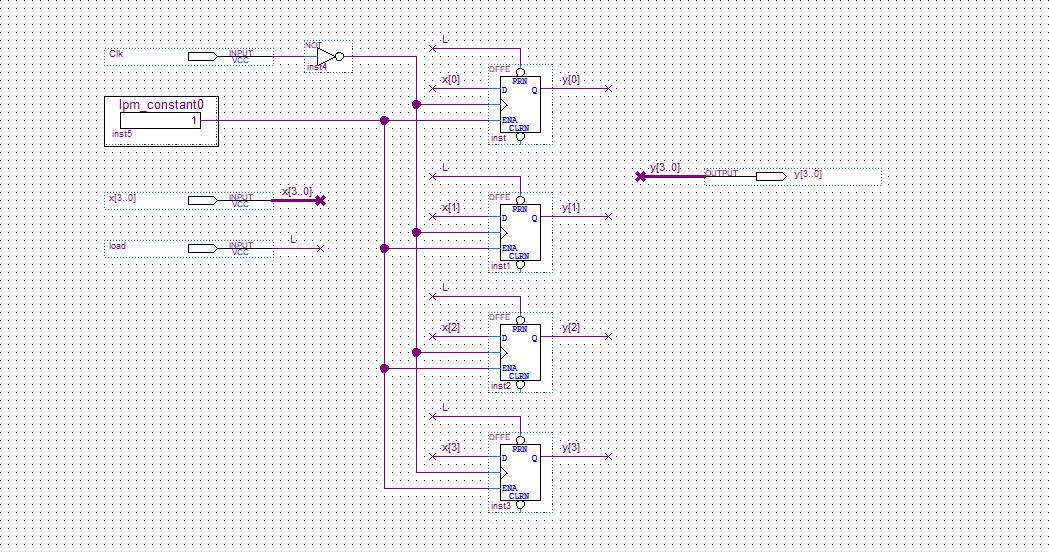

В первой части задания было разработана схема 4-разярдного параллельного регистра с использованием D-триггеров, срабатывающего по убывающему фронту тактового сигнала и поддерживающего асинхронную установку. Схема представлена на риc 1.

Рис 1. Функциональная схема 4-разрядного регистра

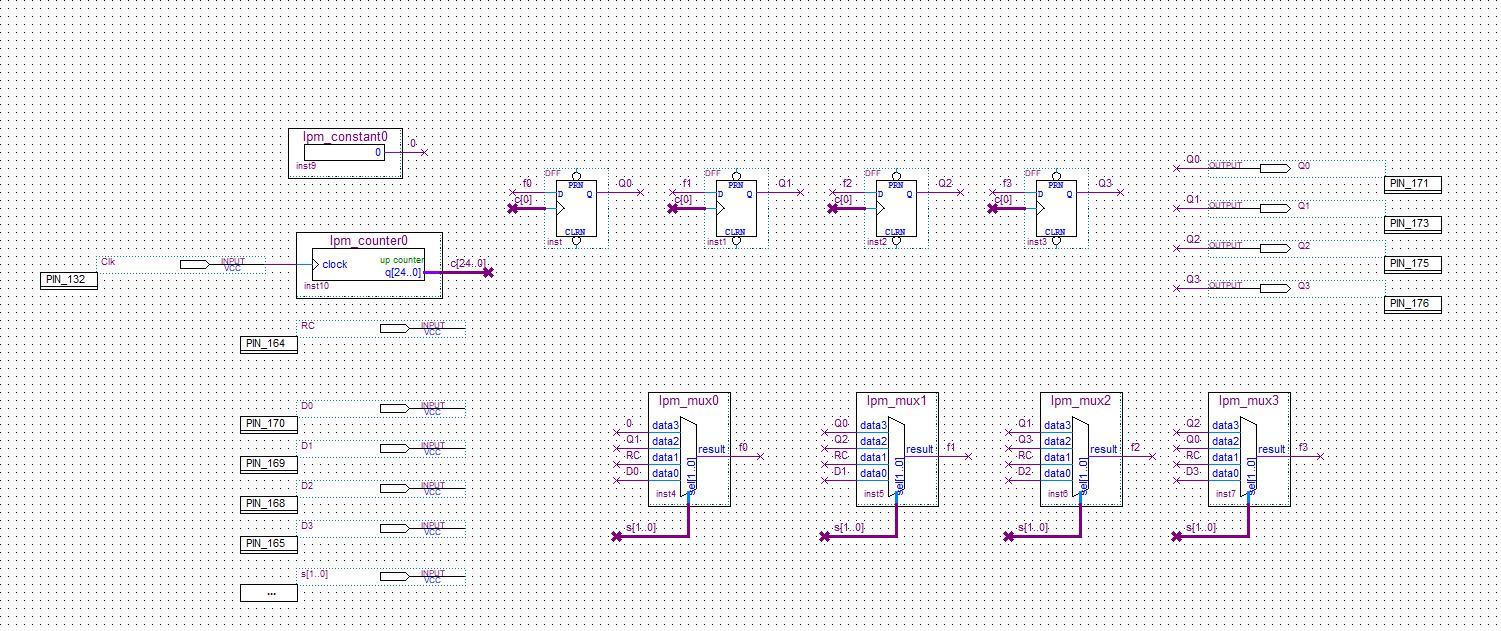

Во второй части задания была разработана схема многофункционального регистра на базе D-триггеров. Для регистра предусмотрены следующие входы:

D0-D3 – разряды входного параллельного кода;

Q0-Q3 – разряды выходного параллельного кода;

C – синхросигнал приема параллельного кода;

RC – синхронный вход сброса регистра;

S0, S1 – входы задания микроопераций.

Регистр поддерживает следующие операции: параллельная загрузка, синхронный сброс, циклический сдвиг влево и сдвиг вправо с заполнением - 0.

Схема регистра представлена на рис 2.

Код микрооперации, S1S0 |

Расшифровка |

00 |

Параллельная загрузка |

01 |

Синхронный сброс |

10 |

Циклический сдвиг влево |

11 |

Сдвиг вправо с заполнением - 0 |

Рис 2. Функциональная схема многофункционального регистра

Функциональное и временное моделирование

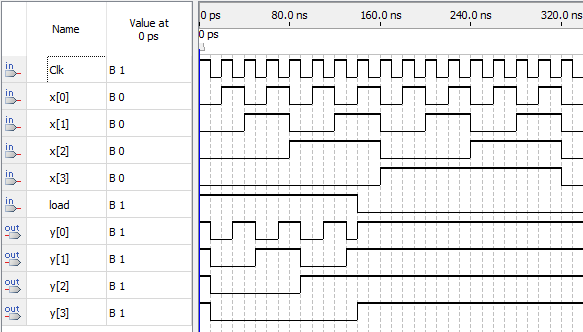

Рис. 3 – Функциональное моделирование 4-разрядного регистра

Рис. 4 – Временное моделирование 4-разрядного регистра

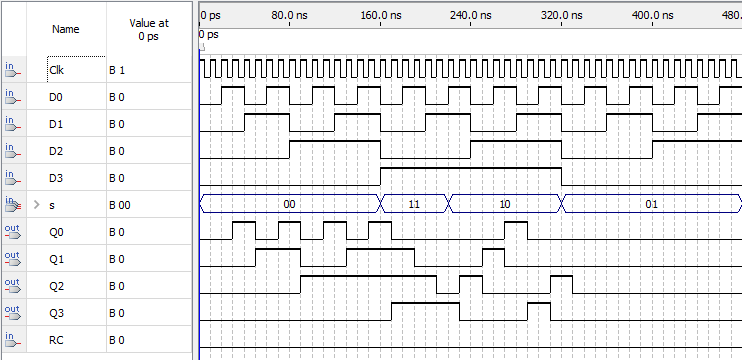

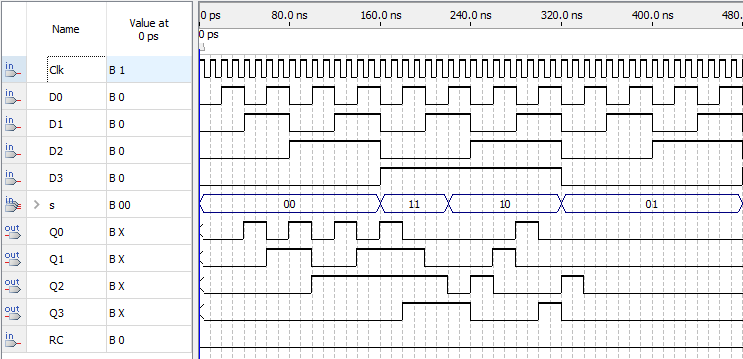

Рис 5. Функциональное моделирование многофункционального регистра

На диаграмме можно наблюдать следующее: сначала происходит параллельная загрузка (00), затем - сдвиг вправо с заполнением-0 (11), после чего происходит циклический сдвиг влево (10) 1 бита и синхронный сброс регистра (01).

Рис 6.Временное моделирование многофункционального регистра

Результаты функционального и временного моделирования продемонстрировали корректную работу обеих схем. При временном моделировании наблюдается незначительное смещение выходных сигналов из-за различных внутренних задержек, которое не влияет на работоспособность.

Макетирование

Макетирование производилось с помощью ПЛИС Cyclone II (EP2C5Q208C8). Соответствие входом/выходов схемы с контактами платы приведено в таб. 1.

Таблица 1

Название |

Контакт |

Описание |

Clk |

132 |

Исходный тактовый сигнал |

D0 |

170 |

Входной сигнал 0 |

D1 |

169 |

Входной сигнал 1 |

D2 |

168 |

Входной сигнал 2 |

D3 |

165 |

Входной сигнал 3 |

Q0 |

171 |

Выходной сигнал 0 |

Q1 |

173 |

Выходной сигнал 1 |

Q2 |

175 |

Выходной сигнал 2 |

Q3 |

176 |

Выходной сигнал 3 |

RC |

164 |

Сигнал синхронного сброса |

S[0] |

162 |

Сигнал выбора операции 0 |

S[1] |

161 |

Сигнал выбора операции 1 |

После описания распиновки проект был загружен в ПЛИС.

Проверка показала корректную работу регистра.

Вывод

В ходе выполнения лабораторной работы были получены теоретические знания и практические навыки в проектировании многофункциональных последовательных регистров на базе D-триггеров.