еще лабы / лаб1

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №1

по дисциплине «Узлы и устройства СВТ»

Тема: Знакомство с системой проектирования Quartus II,

реализация комбинационной схемы

Вариант - 15

Студенты гр. 8308 |

|

Семенёнок В.А. Абдуллин Р.А. Смирнов М.О. |

Преподаватель |

|

Бондаренко П.Н. |

Санкт-Петербург

2021

Цель работы

Освоение процесса проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающего в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента. В процессе работы выполняется проектирование простой комбинационной схемы.

Синтез логической схемы

![]()

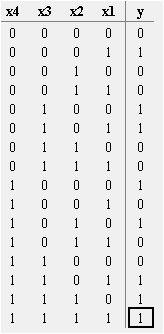

Таблица истинности:

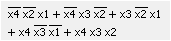

~x4 ~x2 x1 + ~x4 x3 ~x2 + x3 ~x2 x1 + x4 ~x3 ~x1 + x4 x3 x2

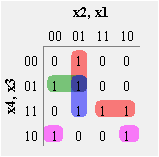

Минимизируем картами Карно :

В итоге получаем следующее:

Приведем к базису 3И-НЕ:

A=~(~(x4x4x4)~(x2x2x2)x1)

B=~(~(x4x4x4)~(x2x2x2)x3)

C=~(~(x2x2x2)x3x1)

D=~(~(x3x3x3)~(x1x1x1)x4)

E=~(x4x3x2)

Y=~(~(ABC)DE)

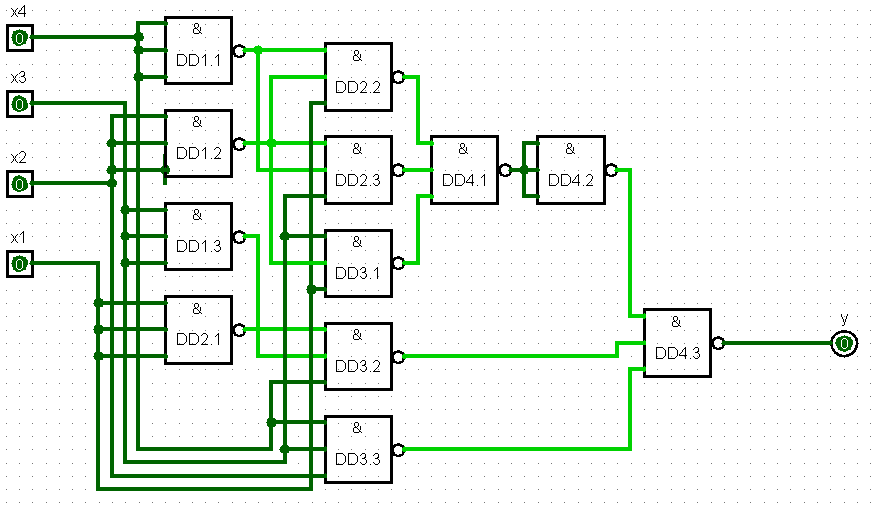

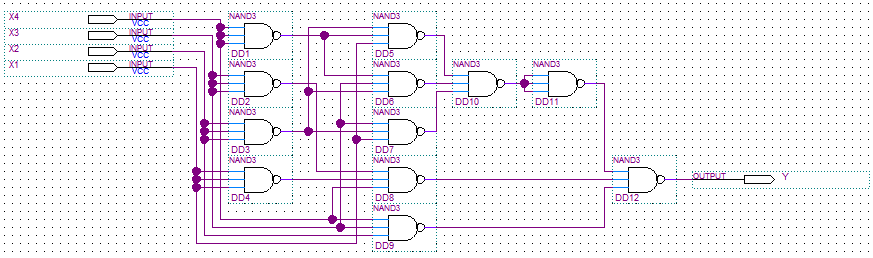

В Logisim построим схему, по формуле выше. Будем использовать только 3И-НЕ элементы. Данная схема протестирована и работает верно.

Рис. 1 Логическая схема.

Функциональная схема

Рис.2. Функциональная схема, выполненная в Quartus II

Результаты функционального и временного моделирования

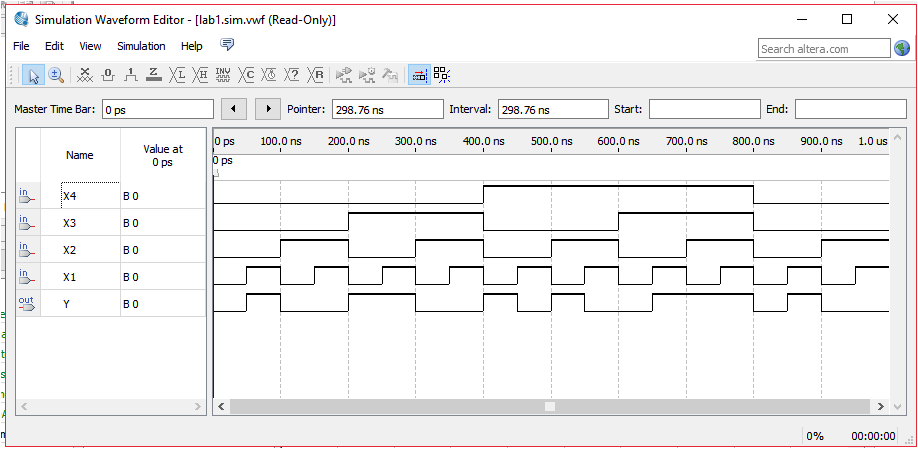

Результаты функционального моделирования:

Рисунок 1. Результаты функционального моделирования

Функциональное моделирование позволяет проверить выход функции перебором всех возможных значений функции.

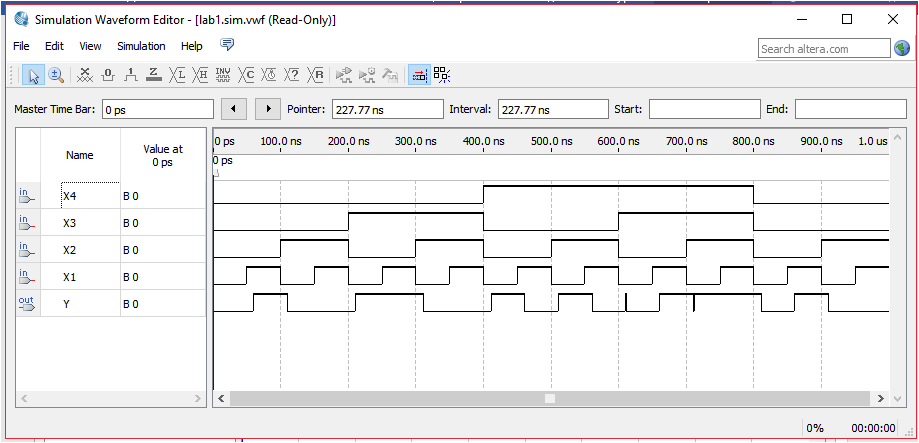

Результаты временного моделирования:

Рисунок 2. Результаты временного моделирования

Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Макетный эксперимент

Для проведения макетного эксперимента схему, построенную в Quartus II, необходимо загрузить на учебную плату. Было осуществлено подключение виртуальных входов и выходов к реальным входам и выходам на учебной плате с использованием возможностей программирования платы программы Quartus II. Впоследствии с помощью движковых переключателей на плате изменялись входные значения, а так как выход функции был подключен к светодиодной линейке, при значении функции равной единице нужный светодиод загорался.

Таким образом, путем перебора всех значений входов была осуществлена проверка правильности работы заданной функции.

Вывод

В ходе выполнения работы был освоен процесс проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающий в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента.