5 лаб - код в архиве / Lab_2_SPI_DAC

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ВТ

Отчет по лабораторной работе № 2

По дисциплине «Интерфейсы периферийных устройств»

Тема: «Управление ЦАП через интерфейс SPI»

Студенты гр. 6307 |

|

Кичерова А. Д. Васин А. М. |

Преподаватель |

|

Молодцов В. О. |

Санкт-Петербург

2019

Цель работы

С помощью САПР Quartus II на основе узла, разработанного в первой лабораторной работе, реализовать узел, осуществляющий управление лабораторным ЦАП через интерфейс SPI.

Задание на работу

Разработать узел, осуществляющий управление передачей данных с ПЛИС на ЦАП AD5313, имеющий 2 канала разрядностями по 10 бит, работающий на частоте не выше 30 МГц, через интерфейс SPI.

Теоретические сведения

ЦАП AD5313 представляет из себя два 10-разрядных ЦАП в одном корпусе с усилителями на выходе. В него встроен 3-проводный последовательный интерфейс, который работает на частоте до 30МГц и совместим со стандартными интерфейсами SPI™, QSPI™, MICROWIRE™ и DSP. Характеристики данной модели ЦАП:

Поставка в 16-выводном TSSOP корпусе

Малое энергопотребление: 300 мкА при 5 В (включая ток потребления источника опорного напряжения)

Режим пониженного потребления: 200 нА при 5 В, 50 нА при 3В

Питание от источника напряжением от +2.5В до +5.5В

Двойная буферизация входной логики

Гарантируется равномерность дифференциальной нелинейности для любых значений входного кода

Настройка входа опорного источника с буферизацией и без буферизации

Диапазоны изменения выходного напряжения: 0–VREF, 0–2VREF

Сброс в ноль выходного напряжения при подаче питания

Опциональный режим шлейфного подключения нескольких микросхем, используя выход SDO

Одновременное обновление обоих выходов ЦАП воздействием на вход LDAC

Вход CLR асинхронного сброса выходов

Экономичный последовательный интерфейс с триггерами Шмитта на входах

Встроенный усилитель-повторитель выходного напряжения

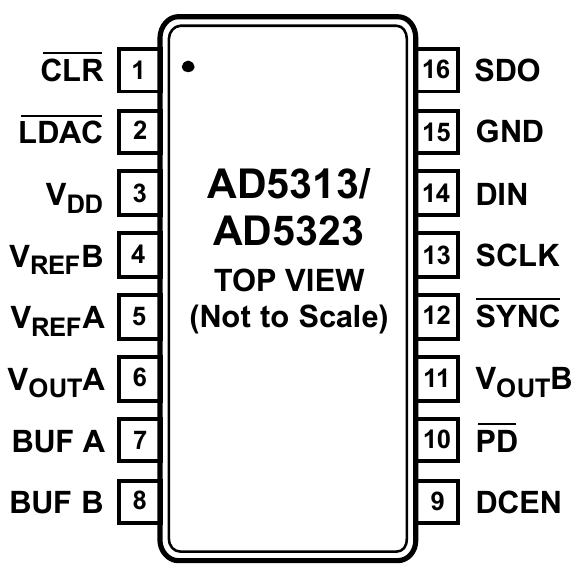

Расположение выводов:

Описание выводов:

CLR |

Вход с активным низким уровнем, сбрасывающий в нулевое состояние оба входных регистров и регистров ЦАП |

LDAC |

Управляющий вход с активным низким уровнем для синхронизации записи в регистры обоих ЦАП из входных регистров |

VDD |

Вход питания |

VREFА |

Вход от источника опорного напряжения для ЦАП А |

VREFB |

Вход от источника опорного напряжения для ЦАП В |

BUF A |

Вход управления буферизацией входа источника опорного напряжения ЦАП А (1-вкл./0-выкл.) |

BUF В |

Вход управления буферизацией входа источника опорного напряжения ЦАП В (1-вкл./0-выкл.) |

VOUTA |

Выход усилителя напряжения ЦАП A |

VOUTB |

Выход усилителя напряжения ЦАП В |

DCEN |

Вход активизации режима шлейфного подключения (1- активный уровень) |

PD |

Вход аппаратной активизации режима пониженного энергопотребления (0- активный уровень) |

SYNC |

Управляющий вход с активным низким уровнем (выбор микросхемы) |

SCLK |

Вход синхронизации последовательной связи |

DIN |

Ввод последовательных данных |

GND |

Общий для всех частей микросхемы |

SDO |

Выход последовательных данных в режиме шлейфного подключения |

Опорное напряжение для каждого ЦАП поступает со специально предусмотренных входов. Входы опорного напряжения могут настраиваться на режимы с буферизацией и без буферизации. Используя вход LDAC, можно обеспечить одновременность обновления выходных напряжений обоих ЦАП. В состав данных микросхем входит также схема сброса при подаче питания, которая обеспечивает установку нулевого выходного напряжения с момента подачи питания до выполнения первой действительной операции записи в регистр ЦАП. Имеется также вход асинхронного сброса выходного напряжения обоих ЦАП в ноль с активным низким уровнем. Для этих устройств реализован механизм перевода в режим пониженного энергопотребления, в котором ток потребления снижается вплоть до 200 нА при 5В питания (50 нА при 3В), при этом имеется возможность программировать подключение к выходу резистора и его номинал. Используя выход SDO, можно организовать режим шлейфного подключения нескольких микросхем.

Ход работы

С помощью САПР Quartus II на языке VHDL разработан генератор, понижающий частоту работы лабораторного макета 40 МГц до 20 МГц.

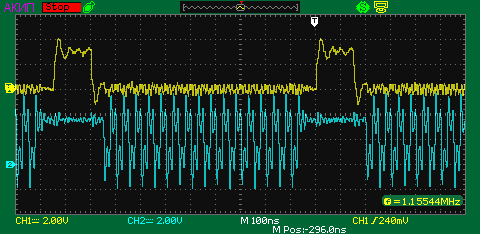

Следом, в соответствии со спецификацией AD5313, разработан узел, управляющий передачей данных на ЦАП. После распиновки контактов ПЛИС, проект был загружен на плату, к ней был подключен ЦАП, и работа была проверена с помощью осциллографа.

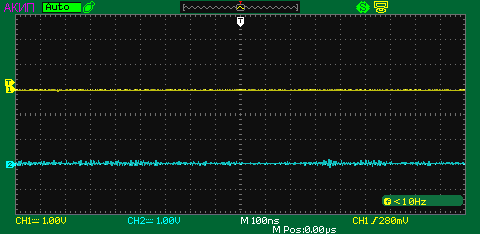

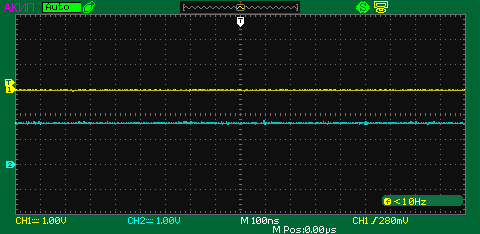

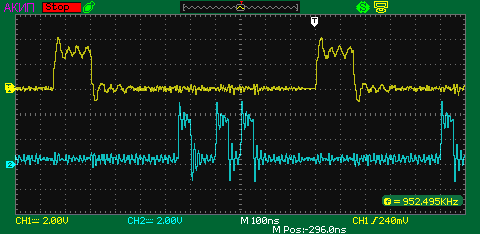

Наблюдение работы узла на осциллографе показало, что интерфейс спроектирован корректно, ниже представлены результаты с осциллографа.

Рисунок 1 Все нули

Рисунок 2 Все единицы

SS

DATA

SS

SCK

SS

LDAC

Вывод: в результате работы был спроектирован узел, осуществляющий управление передачей данных через интерфейс SPI на ЦАП AD5313. Функционирование узла было проверено на учебной плате с помощью осциллографа.