5 лаб - код в архиве / Lab_1_SPI

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ВТ

Отчет по лабораторной работе № 1

По дисциплине «Интерфейсы периферийных устройств»

Тема: «Интерфейс SPI»

Студенты гр. 6307 |

|

Васин А. М. Кичерова А. Д. |

Преподаватель |

|

Молодцов В. О. |

Санкт-Петербург

2019

Цель работы

С помощью САПР Quartus II реализовать интерфейс SPI, произвести макетирование и проверить работу разработанного узла на осциллографе.

Задание на работу

Разработать интерфейс SPI, работающий в режиме 0 на частоте 1 МГц.

Теоретические сведения

SPI – это последовательный синхронный стандарт передачи данных в режиме полного дуплекса.

В SPI используются четыре цифровых сигнала:

MOSI — выход ведущего, вход ведомого (англ. Master Output, Slave Input). Служит для передачи данных от ведущего устройства ведомому.

MISO — вход ведущего, выход ведомого (англ. Master Input, Slave Output). Служит для передачи данных от ведомого устройства ведущему.

SCK — последовательный тактовый сигнал (англ. Serial Clock). Служит для передачи тактового сигнала для ведомых устройств.

CS или SS — выбор микросхемы, выбор ведомого (англ. Chip Select, Slave Select).

Уровень напряжения не оговорен, но у контроллера и ведомого устройства он должен быть одинаковым.

Так как ведущее и ведомое устройства тактируются одним и тем же сигналом SCK, согласование не требуется.

За одну передачу можно передать пакет данных заданного объема (обычно 1-2 байта).

Обычно частота ограничивается только сверху (не более 50 МГц), может быть непостоянна.

Выше представлены временные диаграммы работы интерфейса в разных режимах. По заданию наш интерфейс должен работать в режиме 0. В этом режиме данные должны быть стабильны по положительному фронту. Этот режим принято обозначать комбинацией CPOL = 0 (Clock Polarity) и CPHA = 0 (Clock Phase). Все режимы интерфейса:

режим 0 (CPOL = 0, CPHA = 0);

режим 1 (CPOL = 0, CPHA = 1);

режим 2 (CPOL = 1, CPHA = 0);

режим 3 (CPOL = 1, CPHA = 1).

Ход работы

С помощью САПР Quartus II на языке VHDL разработан генератор, понижающий частоту работы лабораторного макета 40 МГц в сорок раз до нужных по заданию 1 МГц.

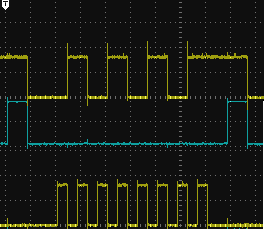

Следом, имея генератор нужной нам частоты, разработан сам интерфейс, работающий в режиме 0. После распиновки контактов ПЛИС, проект был загружен на плату, и его работа была проверена с помощью осциллографа.

DATA

SS

SCK

Передача байта данных 11010011:

DATA

SS

SCK

Передача байта данных 01010101:

DATA

SS

SCK

Наблюдение работы узла на осциллографе показало, что интерфейс спроектирован корректно и соответствует поставленному заданию.

Вывод: в результате работы был спроектирован интерфейс SPI, работающий в режиме 0 на частоте 1 МГц. Функционирование узла было проверено на учебной плате с помощью осциллографа.