Лабы / 5

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной Техники

отчет

по лабораторной работе №5

по дисциплине «Узлы и устройства средств вычислительной техники»

Тема: Исследование регистров

(вариант 1)

Студентки гр.6305 |

|

Кинзябаева Г.И. Тарасова А.А. |

Преподаватель |

|

Буренёва О.И. |

Санкт-Петербург

2019

Оглавление

ЦЕЛЬ РАБОТЫ 4

ЗАДАНИЕ НА РАБОТУ 4

ХОД РАБОТЫ 5

1.ПАРАЛЛЕЛЬНЫЙ РЕГИСТР 5

2.МНОГОФУНКЦИОНАЛЬНЫЙ РЕГИСТР 6

ВЫВОД 8

ЦЕЛЬ РАБОТЫ

Исследовать особенности проектирования регистров различного типа, закрепить навыки синтеза и экспериментального исследования узлов в среде Quartus II.

ЗАДАНИЕ НА РАБОТУ

Разработать четырехразрядный параллельный регистр с использованием D-триггеров с асинхронным сбросом и разрешением выдачи L. Срабатывание происходит по подъему тактового сигнала. В качестве базовых элементов использовать соответствующие примитивы библиотеки САПР Quartus II. Выполнить временное и функциональное моделирование, обеспечив полный перебор возможных значений входных сигналов.

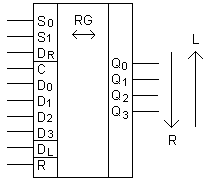

Разработать многофункциональный регистр на базе D-триггеров. Условное графическое обозначение приведено на рисунке 1.

Рисунок 1

В регистре предусмотрены следующие входы:

D0 – D3 – разряды входного параллельного кода;

Q0 – Q3 – разряды выхода;

C – синхросигнал приема параллельного кода;

R – асинхронный вход сброса регистра;

S0, S1 – входы задания микроопераций;

DR, DL – последовательные входы при сдвиге вправо и влево соответственно.

Выполняемые микрооперации: (1) параллельная загрузка, (2) синхронный сброс, (5) сдвиг вправо циклический, (11) сдвиг влево, заполнение DL.

Подготовить временную диаграмму проверки работоспособности и проверить работу схемы на макетной плате.

ХОД РАБОТЫ

1.ПАРАЛЛЕЛЬНЫЙ РЕГИСТР

Спроектированная функциональная схема регистра представлена на рис. 2.

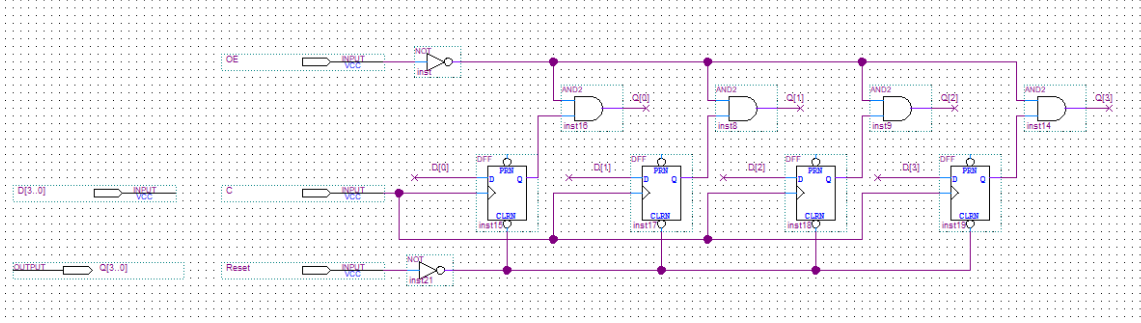

Реализация схемы параллельного регистра в системе Quartus II представлена на рисунке 3.

Рисунок 3

На данной схеме триггеры формируют 4-разрядный регистр, в который осуществляется параллельный ввод данных с входов D0-D3. По сигналу Reset осуществляется асинхронный сброс всех разрядов сформированного регистра. Конъюнкторы управляют разрешением выдачи сигналов с регистра (разрешением выдачи L).

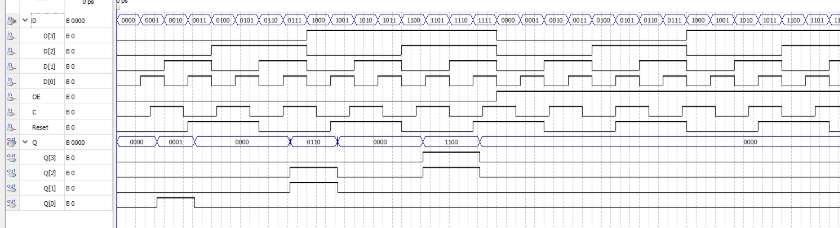

Результат функционального моделирования приведен на рисунке 4.

Рисунок 4

Результат временного моделирования представлен на рисунке 5.

Рисунок 5

Видим, что задержки на выходах минимальны, риски не добавляют изменений в работе ВД.

2.МНОГОФУНКЦИОНАЛЬНЫЙ РЕГИСТР

В данной лабораторной работе нам были даны входы s1и s0, а определяющие режимы работы регистра показаны в таблице 1:

Таблица 1

Режим работы |

S1 |

S0 |

Синхронный сброс |

0 |

0 |

Циклический сдвиг вправо |

0 |

1 |

Сдвиг влево, заполнение DL |

1 |

0 |

Параллельная загрузка |

1 |

1 |

Спроектированная функциональная схема регистра представлена на рисунке 6.

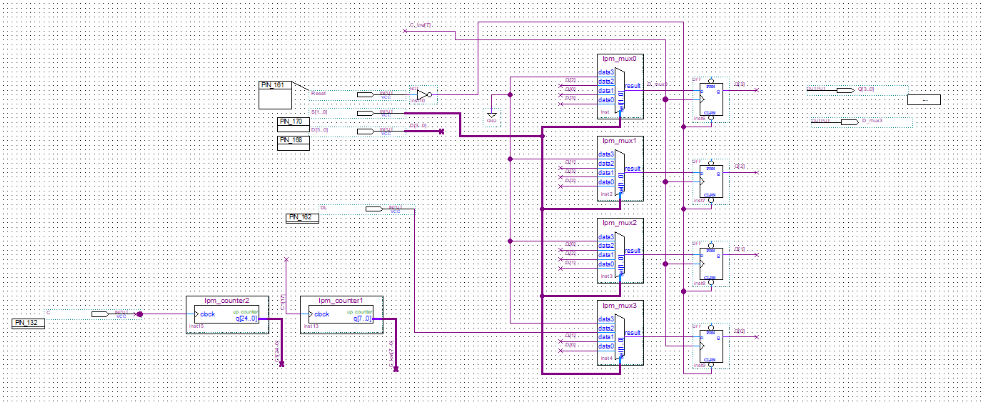

Реализация схемы параллельного регистра в системе Quartus II представлена на рисунке 7.

Рисунок 7

В схему добавлены два последовательных счётчика, для понижения частоты входного тактового сигнала

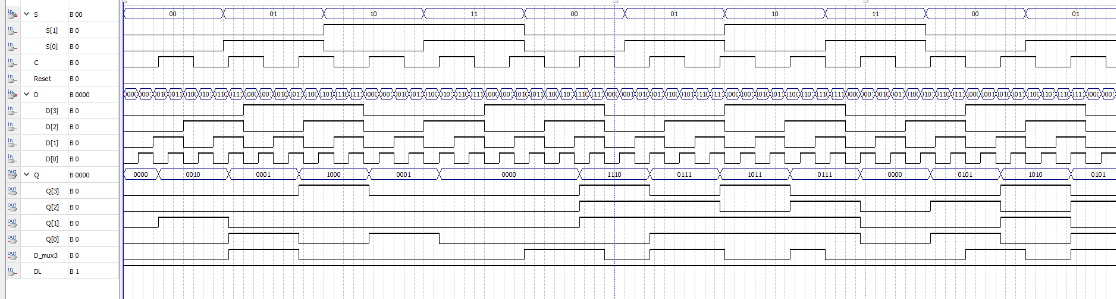

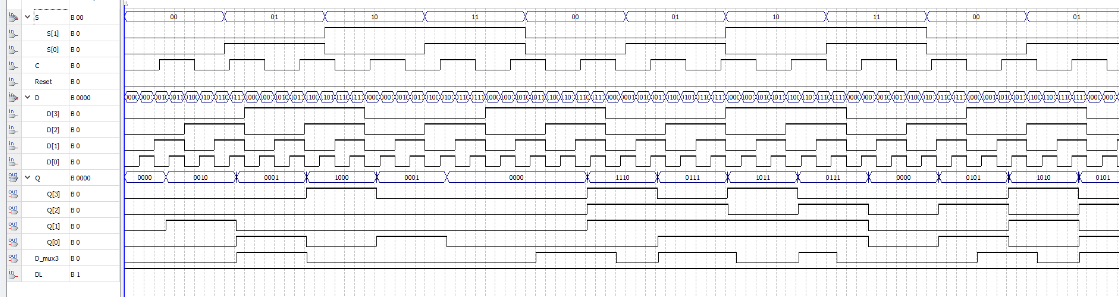

Результат функционального моделирования приведен на рисунке 8.

Рисунок 8

Результат временного моделирования представлен на рисунке 9.

Рисунок 9

Возникающие риски не меняют выходные данные.

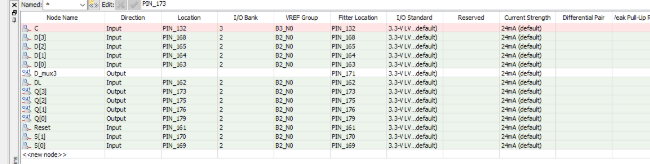

Проверили работу многофункционального регистра на макетной плате с помощью светодиодной линейки и блока переключателей. Результаты соответствуют заявленным. Назначение контактов рисунок 10.

Рисунок 10

ВЫВОД

В процессе работы был закреплен навык работы с триггерами в среде проектирования Quartus II. Научились самостоятельно разрабатывать параллельный и многофункциональный регистр.