Лабы / laba6

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №6

по дисциплине «Узлы и устройства СВТ»

Вариант - 3

Студенты гр. 8308 |

|

Шубинов Р.В. Треско М.Ю. |

Преподаватель |

|

Бондаренко П.Н. |

Санкт-Петербург

2021

Цель работы

Освоение процесса проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающего в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента. В процессе работы выполняется проектирование простой комбинационной схемы.

Задание

Часть 1. Синтезировать на основе имеющихся в библиотеке САПР Quartus II примитивов распределитель тактовых сигналов на основе сдвигающего регистра.

Часть 2. Используя примитивы САПР Quartus II, синтезировать РТС на основе счетчика Джонсона.

Уточнение задания для варианта 3

Количество выходных каналов – 7

Циркуляция единицы

В части 2 необходимо синтезировать РТС с самовосстановлением, реализованным дополнительным триггером

Часть 1

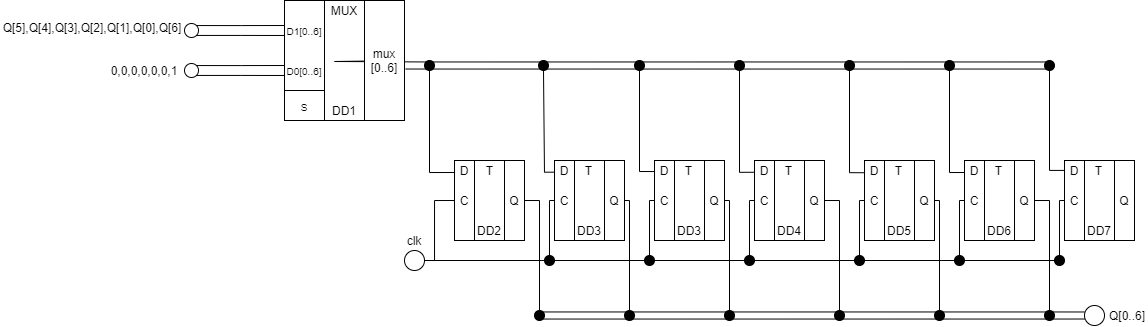

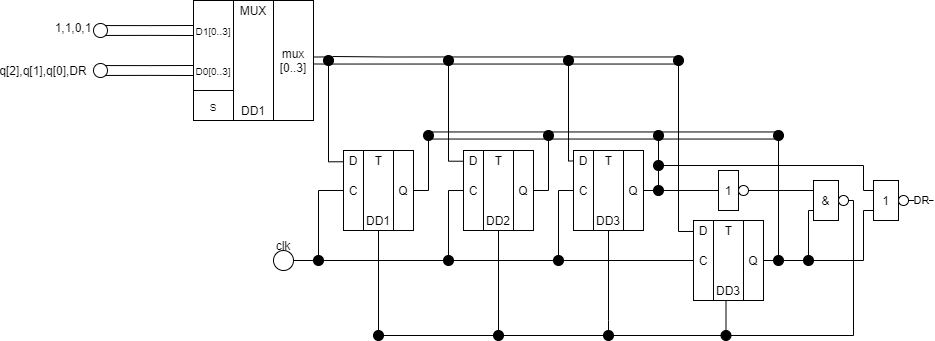

Схема ГОСТ представлена на рис.1.

Рис.1. Схема ГОСТ.

Функциональная схема

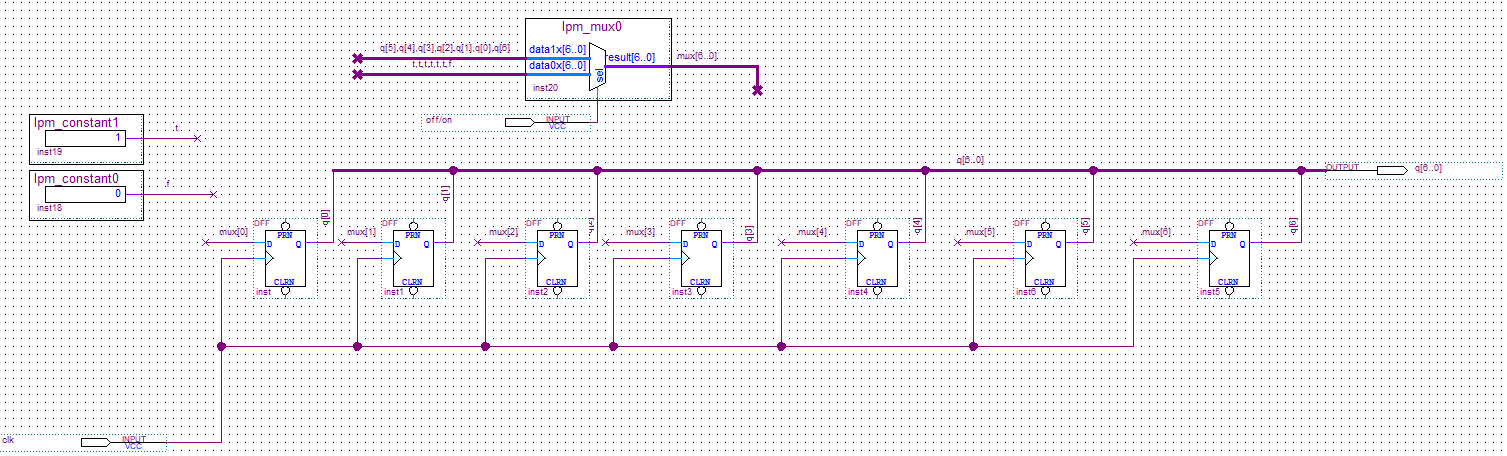

Функциональная схема представлена на рис. 2.

Рис.2. Функциональная схема, выполненная в Quartus II

Результаты функционального и временного моделирования

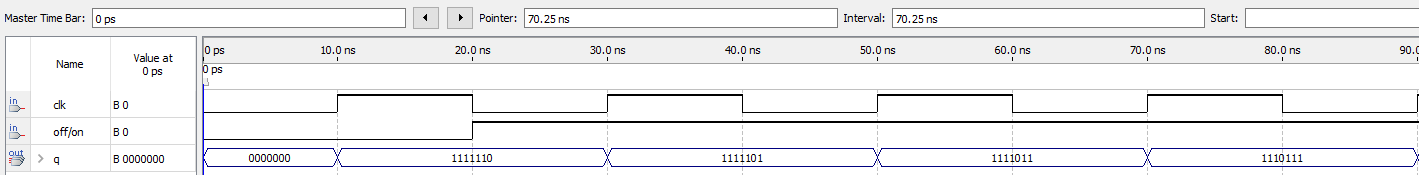

Результат моделирования представлен на рис.3. По результатам функционального моделирования можно сделать вывод, что схема работает верно.

Рис.3. Результаты функционального моделирования

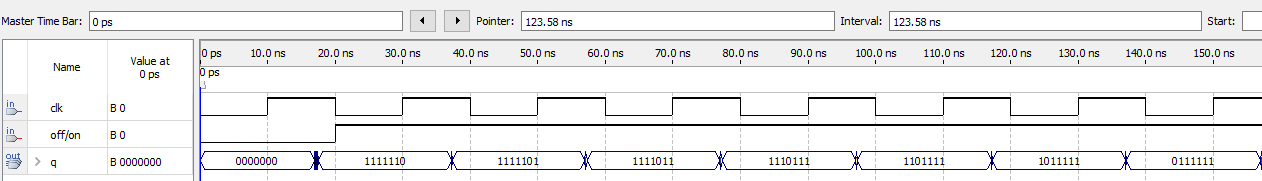

Проведено временное моделирование. Результаты временного моделирования представлены на рис.4. Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Рис.4. Результаты временного моделирования

Часть 2.

Схема ГОСТ представлена на рис.5.

Рис.5. Схема ГОСТ.

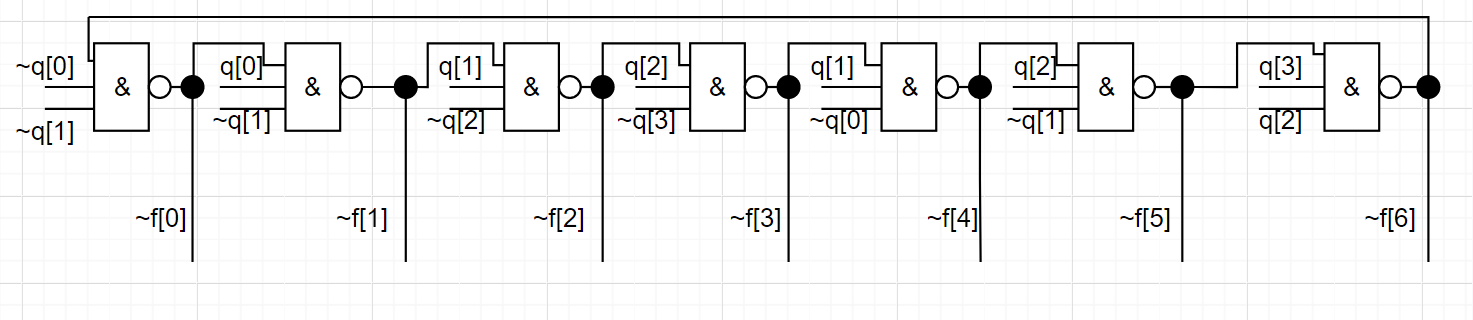

Также нам необходимо преобразовать код Джонсона в код «1 из N». Для этого был спроектирован дешифратор Джонсона. Схема ГОСТ дешифратора представлена на рис. 6.

Рис. 6. Схема ГОСТ дешифратора

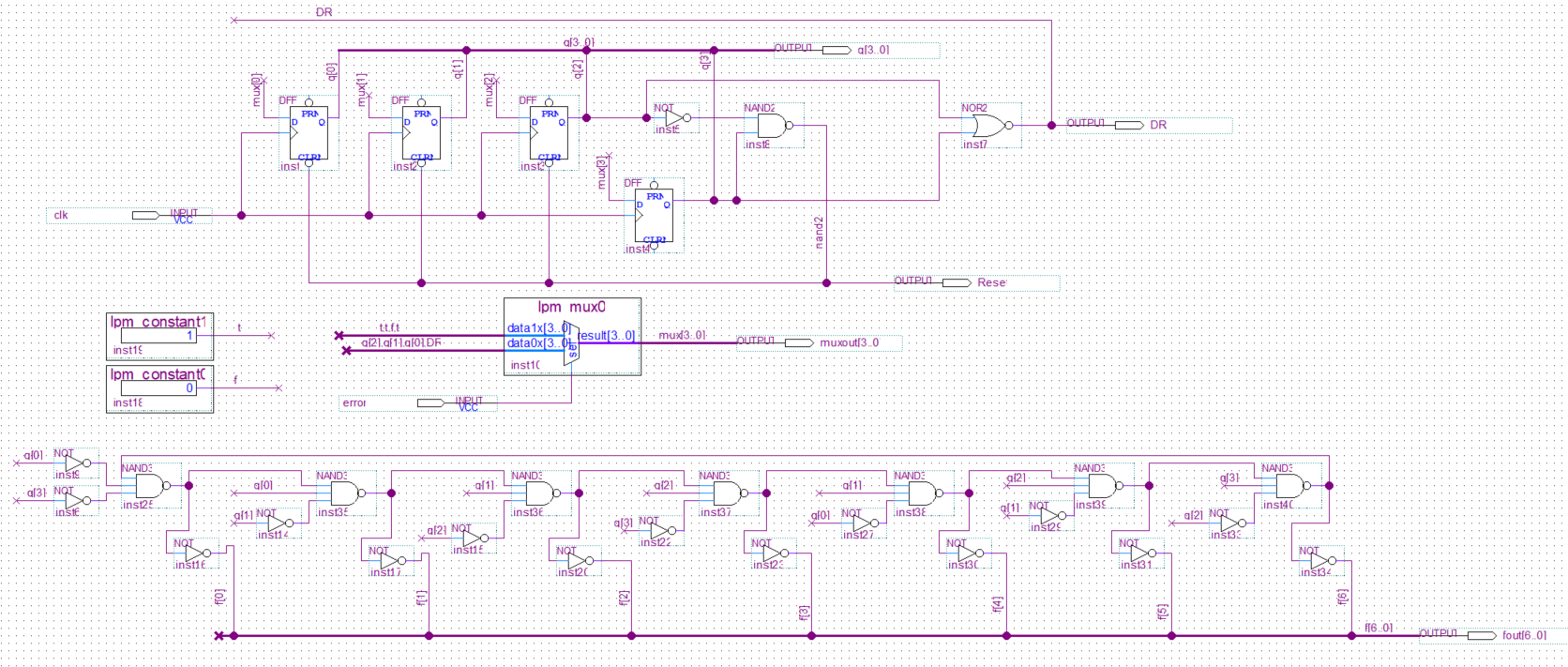

Функциональная схема

Функциональная схема представлена на рис. 7

Рис. 7. Функциональная схема

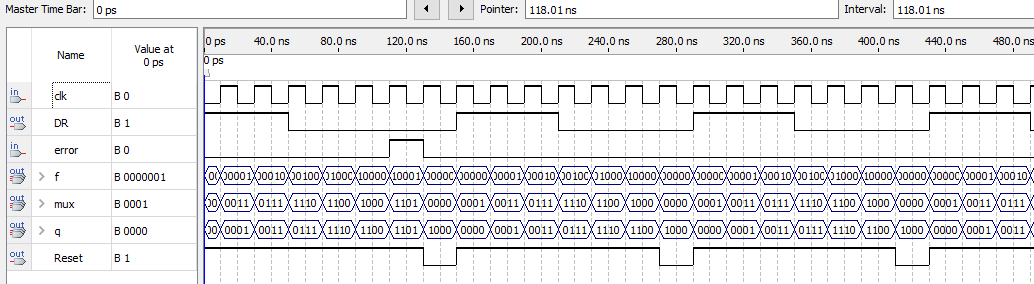

Результаты функционального и временного моделирования

Результат моделирования представлен на рис.8. По результатам функционального моделирования можно сделать вывод, что схема работает верно.

Рис.8. Результаты функционального моделирования

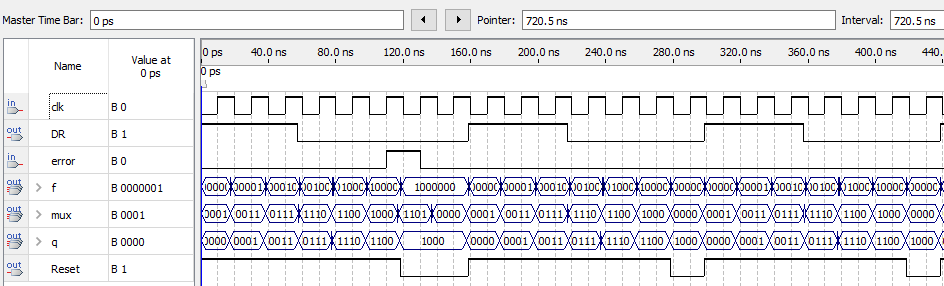

Проведено временное моделирование. Результаты временного моделирования представлены на рис.9. Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Рис.9. Результаты временного моделирования

Макетный эксперимент

Для проведения макетного эксперимента схему, построенную в Quartus II, необходимо загрузить на учебную плату. Было осуществлено подключение виртуальных входов и выходов к реальным входам и выходам на учебной плате с использованием возможностей программирования платы программы Quartus II. Впоследствии с помощью движковых переключателей на плате изменялись входные значения, а так как выход функции был подключен к светодиодной линейке, при значении функции равной единице нужный светодиод загорался. Таким образом, путем перебора всех значений входов была осуществлена проверка правильности работы заданной функции.

Вывод

В ходе выполнения работы был освоен процесс проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающий в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента.