Лабы / lab7

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №7

по дисциплине «Узлы и устройства СВТ»

Тема: Реализация комбинационной схемы

Вариант 3

Студенты гр. 8308 |

|

Треско М.Ю |

|

|

Шубинов Р.В. |

Преподаватель |

|

Бондаренко П.Н. |

Санкт-Петербург

2021

Цель работы

Исследовать особенности функционирования двоичных счетчиков с вырожденными переходами (принудительной установкой в состояния) и различными способами организации переноса.

Задание

Часть 1. Синтезировать на основе имеющейся в библиотеке САПР Quartus II мегафункции счетчика LPM_COUNTER (находящейся в разделе megafunction / arithmetic) счетчик с вырожденными состояниями. При необходимости в процессе настройки мегафункции установить в счетчике входы Clear и / или Load. Варианты заданий приведены в табл. 1. В столбце «способ реализации 1» приведены задания, реализуемые с помощью выделения конечного состояния с помощью дешифратора, в столбце «способ реализации 2» – с помощью дополнительной логики. В ячейках таблицы указаны разрешенные состояния счетчика.

Таблица 1.

Номер бригады |

Способ реализации 1. |

Способ реализации 2. |

3 |

0-12 |

0-2; 5-13 |

Часть 2. Синтезировать на основе имеющихся в библиотеке САПР Quartus II примитивов триггеров счетчик с вырожденными состояниями с модифицированными межразрядными связями. Варианты заданий приведены в табл. 2.

Таблица 2.

Номер бригады |

Порядок счета |

Тип триггера |

3 |

0-11 |

D |

Задание 1.

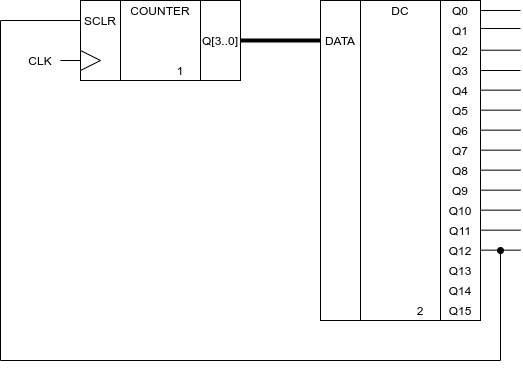

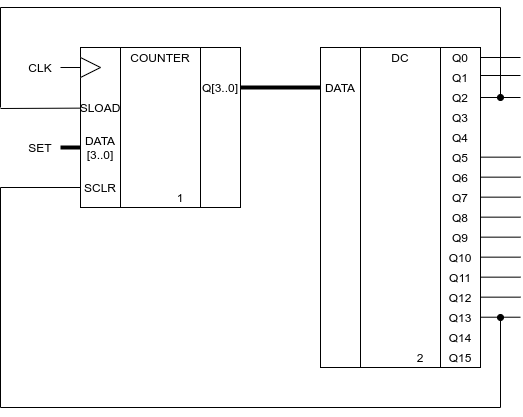

Принципиальная схема представлена на рис.1.

Рис.1. Принципиальная схема.

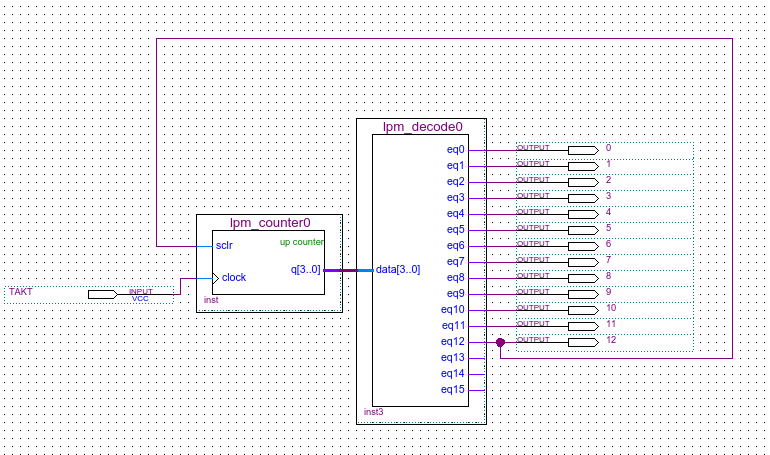

Функциональная схема

Функциональная схема представлена на рис. 2.

Рис.2. Функциональная схема, выполненная в Quartus II

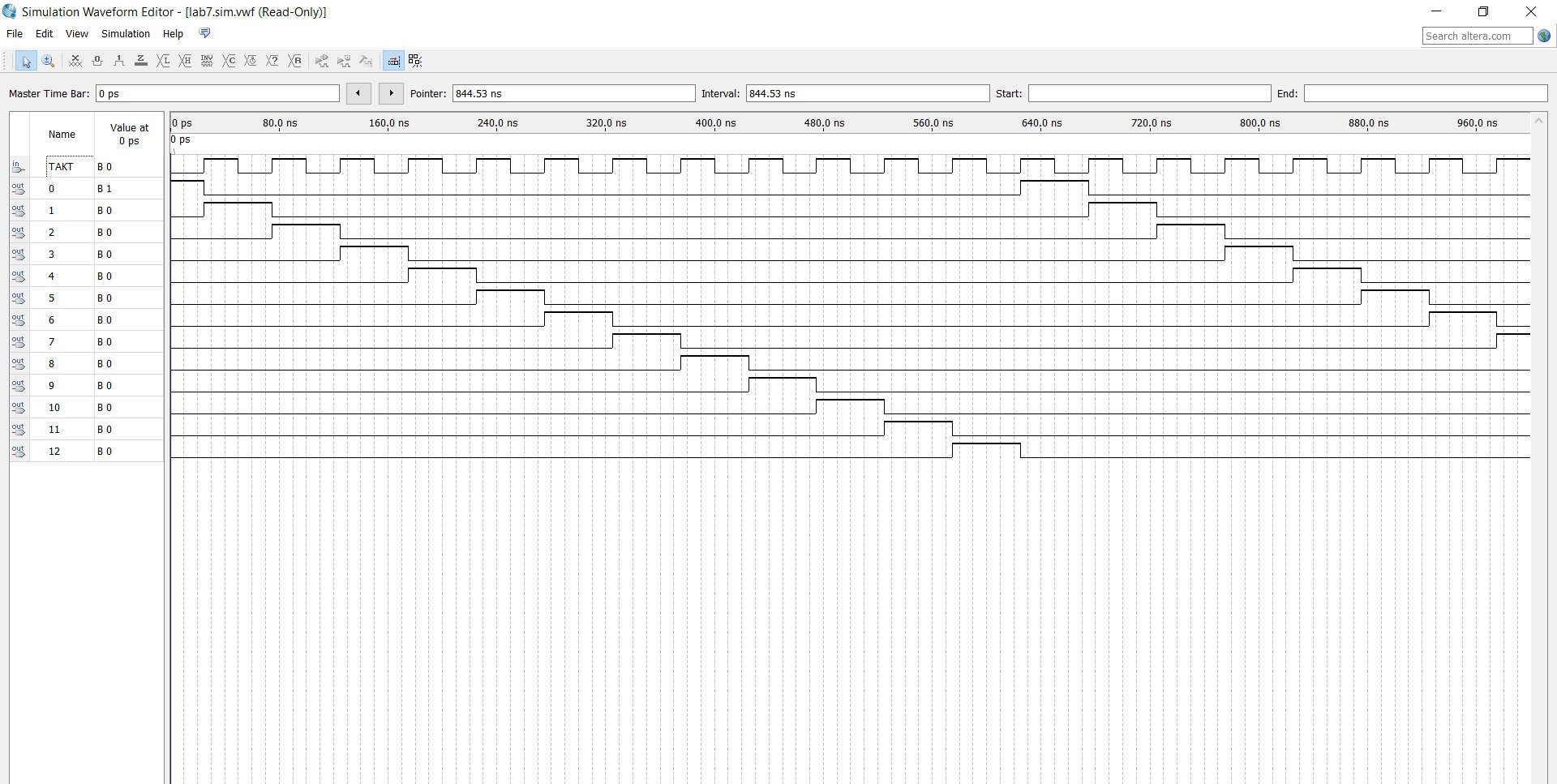

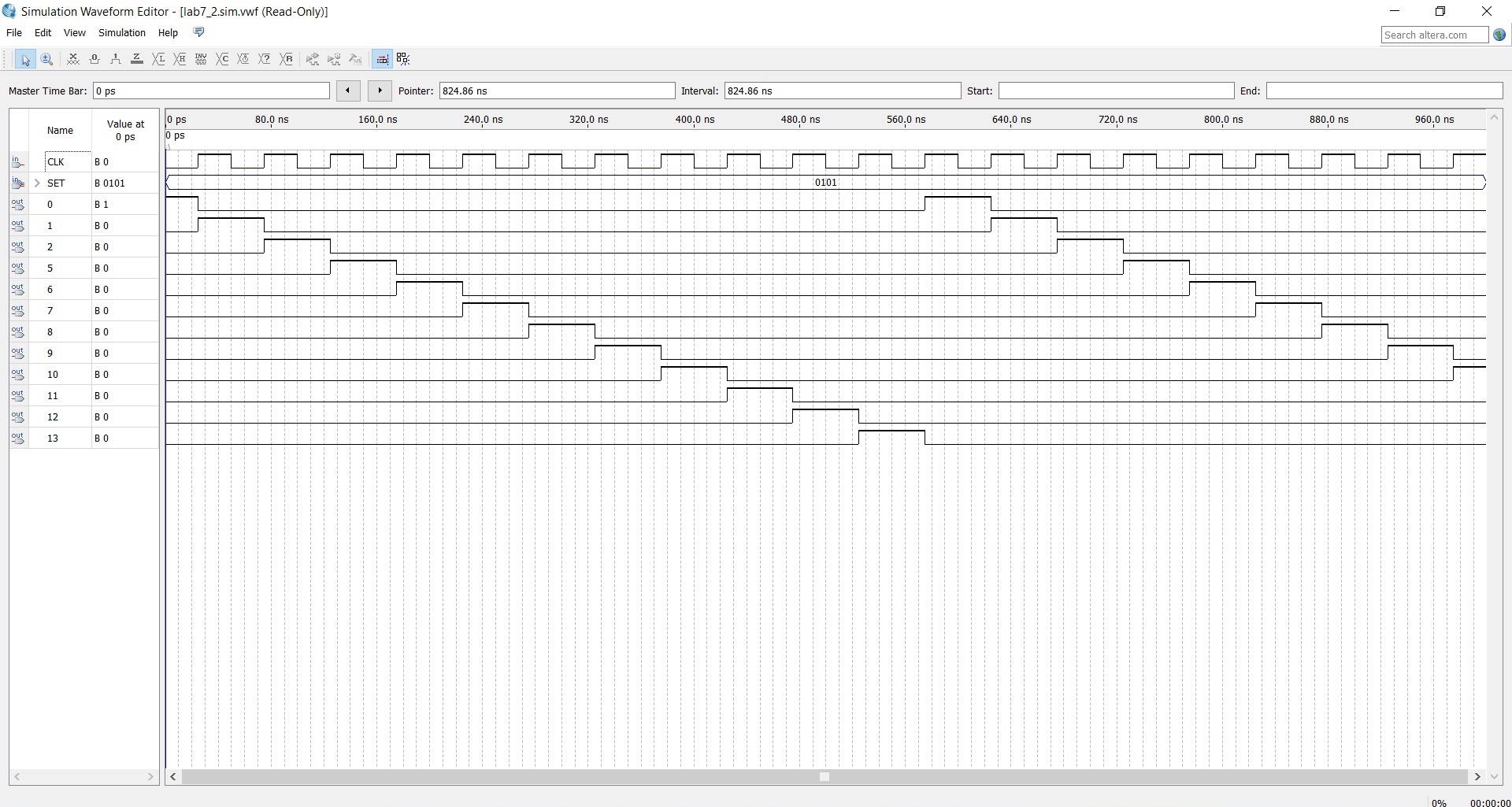

Результаты функционального и временного моделирования

Результат моделирования представлен на рис.3. По результатам функционального моделирования можно сделать вывод, что схема работает верно.

Р ис.3.

Результаты функционального моделирования

ис.3.

Результаты функционального моделирования

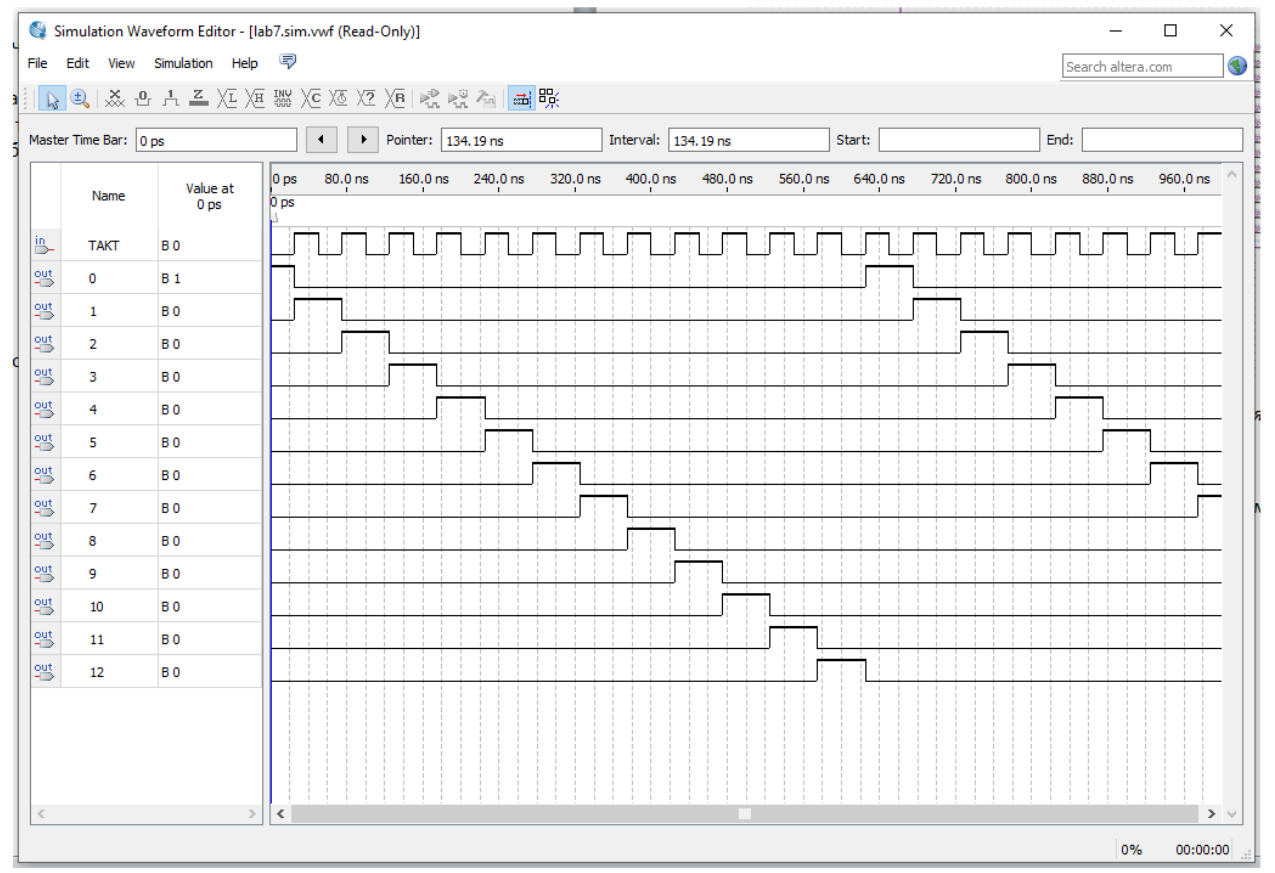

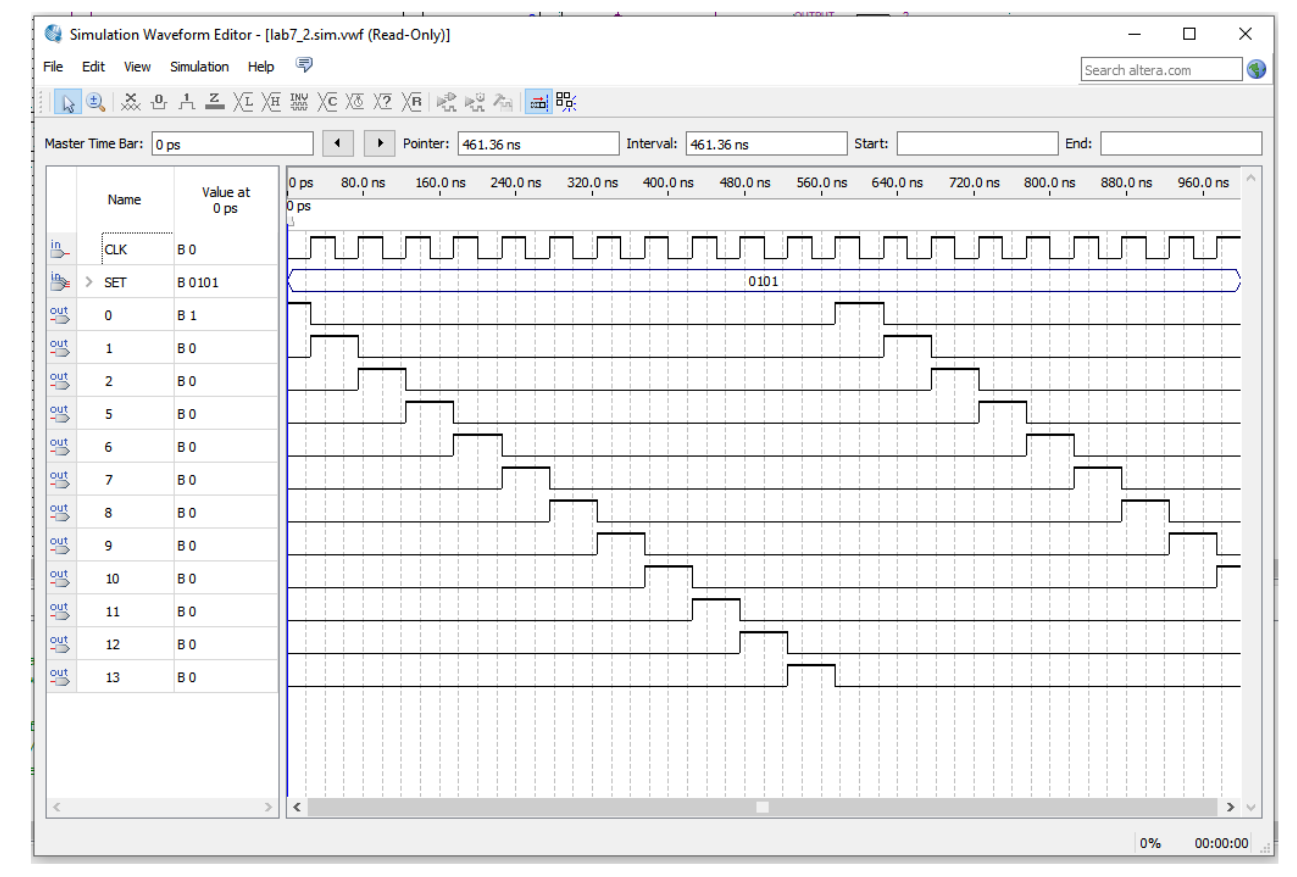

Проведено временное моделирование. Результаты временного моделирования представлены на рис.4. Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Р ис.4.

Результаты временного моделирования

ис.4.

Результаты временного моделирования

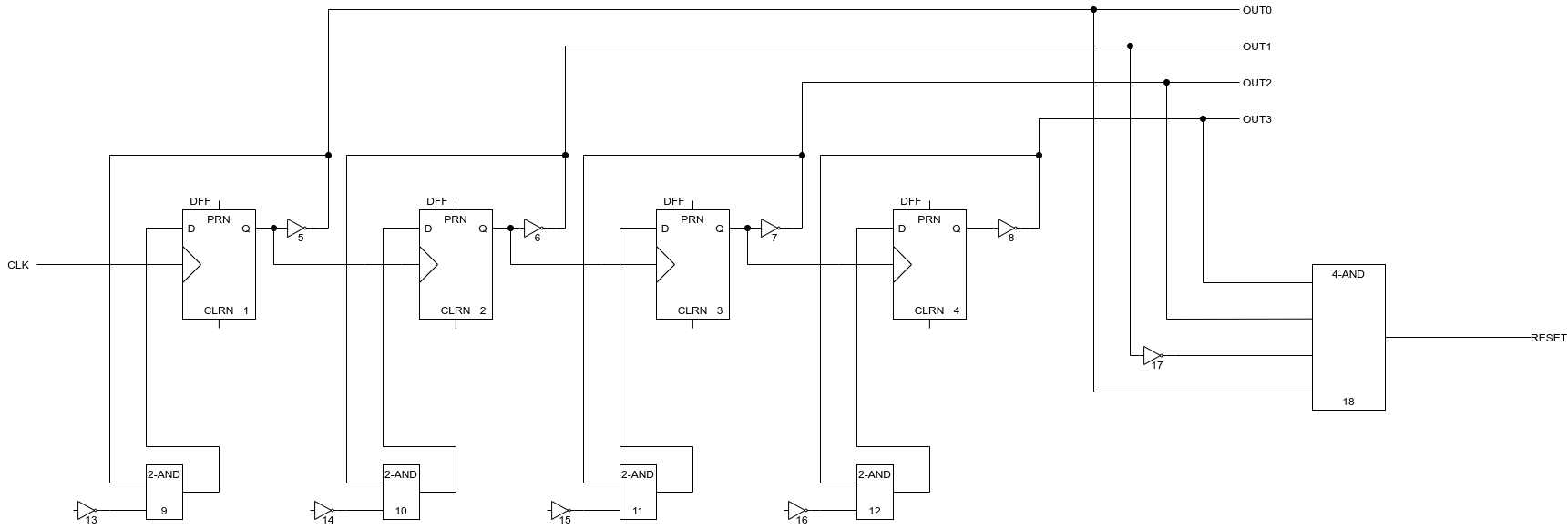

Задание 2.

Принципиальная схема представлена на рис.5.

Рис.5. Принципиальная схема

Функциональная схема

Функциональная схема представлена на рис. 6.

Рис.6. Функциональная схема, выполненная в Quartus II

Результаты функционального и временного моделирования

Результат моделирования представлен на рис.7. По результатам функционального моделирования можно сделать вывод, что схема работает верно.

Р ис.7.

Результаты функционального моделирования

ис.7.

Результаты функционального моделирования

Проведено временное моделирование. Результаты временного моделирования представлены на рис.8. Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Р ис.8.

Результаты временного моделирования

ис.8.

Результаты временного моделирования

Задание 3.

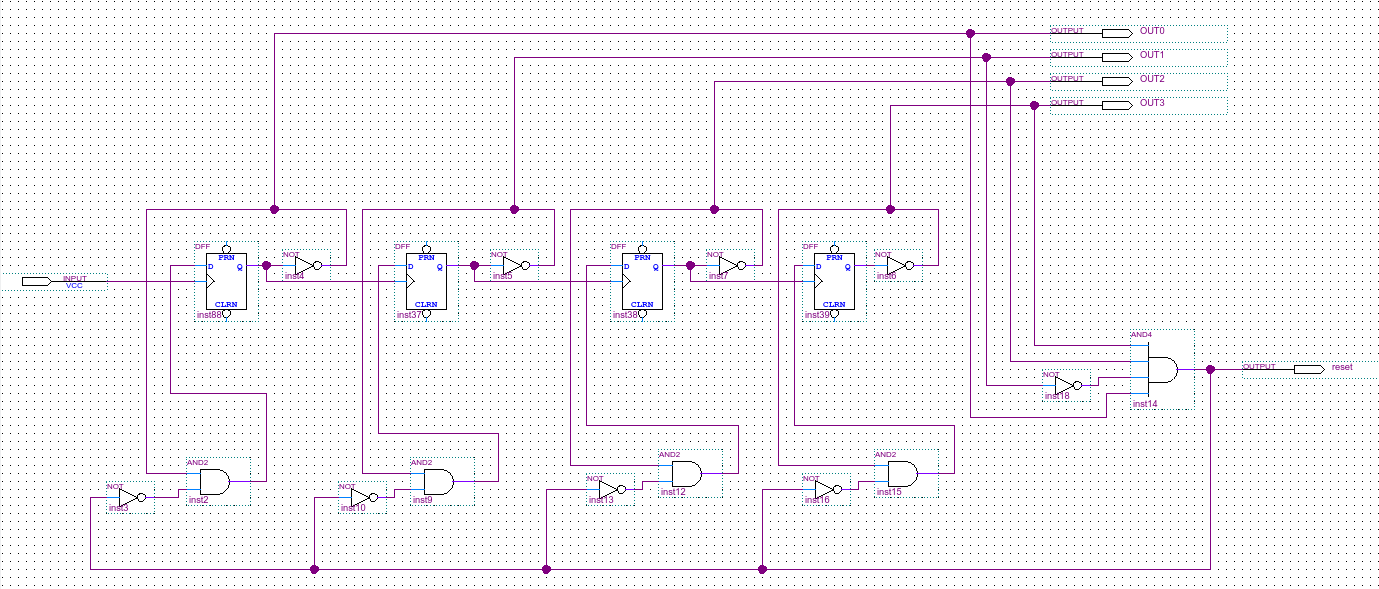

Принципиальная схема представлена на рис.9.

Р ис.9.

Принципиальная

схема

ис.9.

Принципиальная

схема

Функциональная схема

Функциональная схема представлена на рис. 10

Р ис.

10. Функциональная схема

ис.

10. Функциональная схема

Результаты функционального и временного моделирования

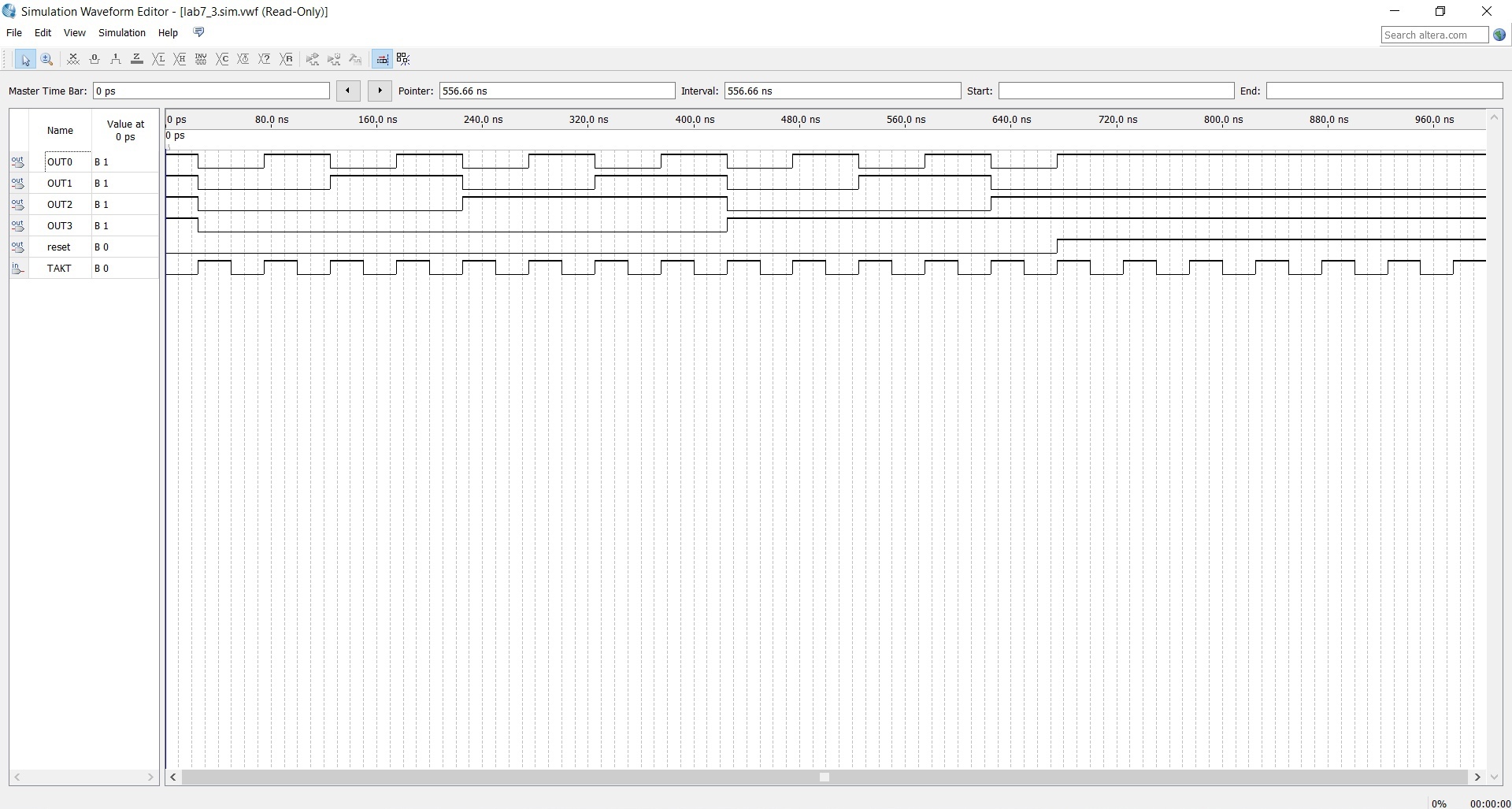

Результат моделирования представлен на рис.11. По результатам функционального моделирования можно сделать вывод, что схема работает верно.

Р ис.11.

Результаты функционального моделирования

ис.11.

Результаты функционального моделирования

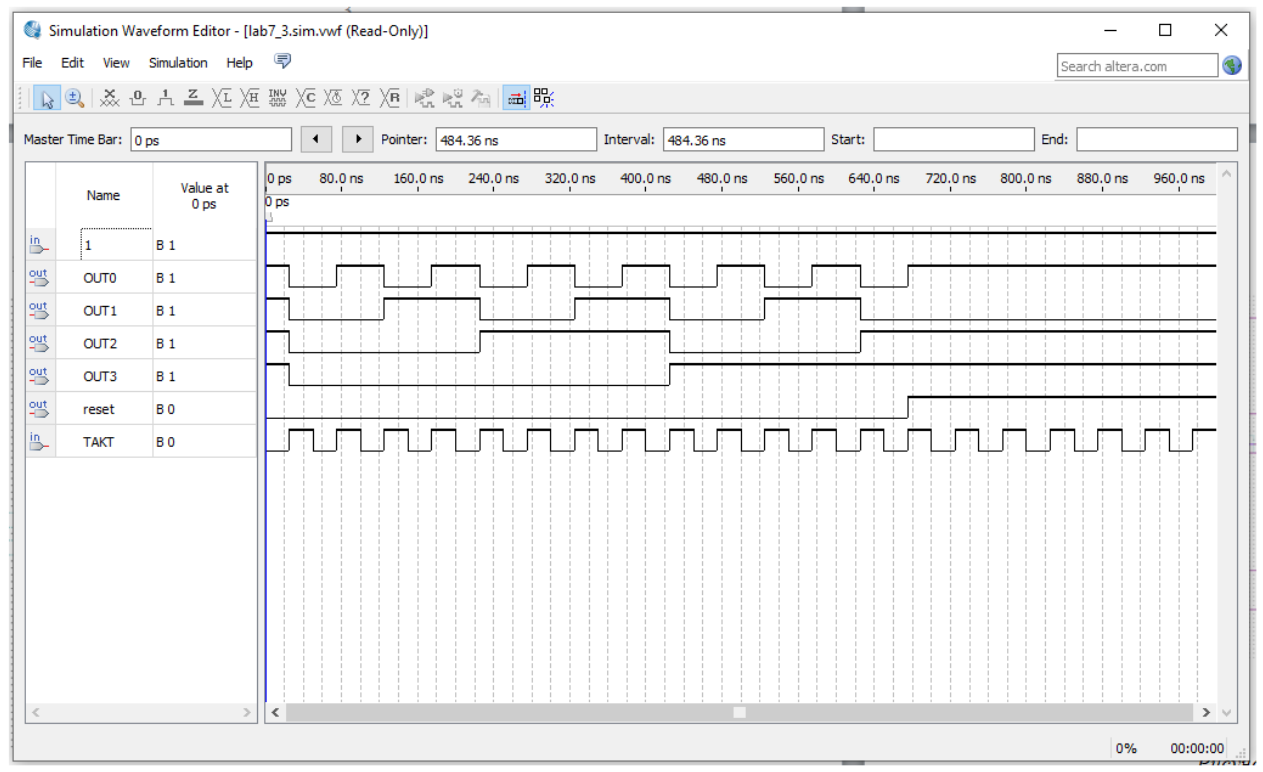

Проведено временное моделирование. Результаты временного моделирования представлены на рис.12. Временное моделирование учитывает временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа), поэтому наблюдается задержка сигнала на выходе и непродолжительное искажение сигнала, связанное с задержкой сигнала на одной из веток элементов.

Р ис.12.

Результаты временного моделирования

ис.12.

Результаты временного моделирования

Макетный эксперимент

Для проведения макетного эксперимента схему, построенную в Quartus II, необходимо загрузить на учебную плату. Было осуществлено подключение виртуальных входов и выходов к реальным входам и выходам на учебной плате с использованием возможностей программирования платы программы Quartus II. Впоследствии с помощью движковых переключателей на плате изменялись входные значения, а так как выход функции был подключен к светодиодной линейке, при значении функции равной единице нужный светодиод загорался. Таким образом, путем перебора всех значений входов была осуществлена проверка правильности работы заданной функции.

Вывод

В ходе выполнения работы был освоен процесс проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающий в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента.