Лабы / lab5

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №5

по дисциплине «Узлы и устройства СВТ»

Тема: Исследование регистров

Студенты гр. 8308 |

|

Треско М.Ю. |

|

|

Шубинов Р.В. |

Преподаватель |

|

Бондаренко П.Н. |

Санкт-Петербург

2021

Цель работы

Цель работы – исследовать особенности проектирования регистров различного типа, закрепить навыки синтеза и экспериментального исследования узлов в среде Quartus II.

Часть 1

Задание

Предполагает разработку 4-разрядного параллельного регистра с использованием триггеров заданного типа. Дополнительно указывается фронт тактового сигнала, по которому происходит срабатывание (↑ – подъем тактового сигнала, ↓ – спад тактового сигнала). Вариант задания представлен в таблице 1.

Табл.1.

Тип триггера |

Такт |

Асинхронный сброс/установка |

Разрешение выдачи |

JK |

↑ |

Установка |

L |

Принципиальная схема

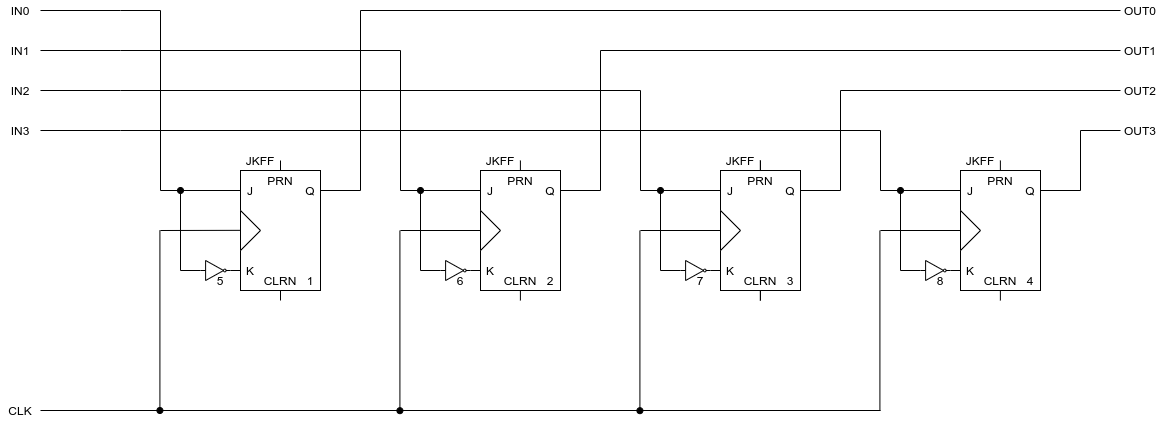

На рисунке 1 представлена схема комбинационного узла, который представляет собой 4-разрядный параллельный регистр.

Рисунок

1 - Принципиальная схема

Рисунок

1 - Принципиальная схема

Функциональная схема

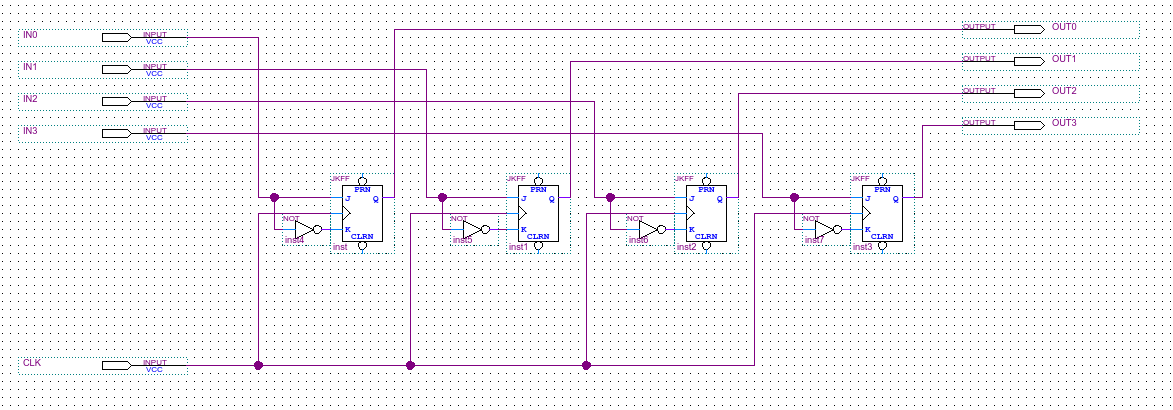

Схема 4-разрядного параллельного регистра представлена на рисунке 2.

Рисунок

2 - Функциональная схема

Рисунок

2 - Функциональная схема

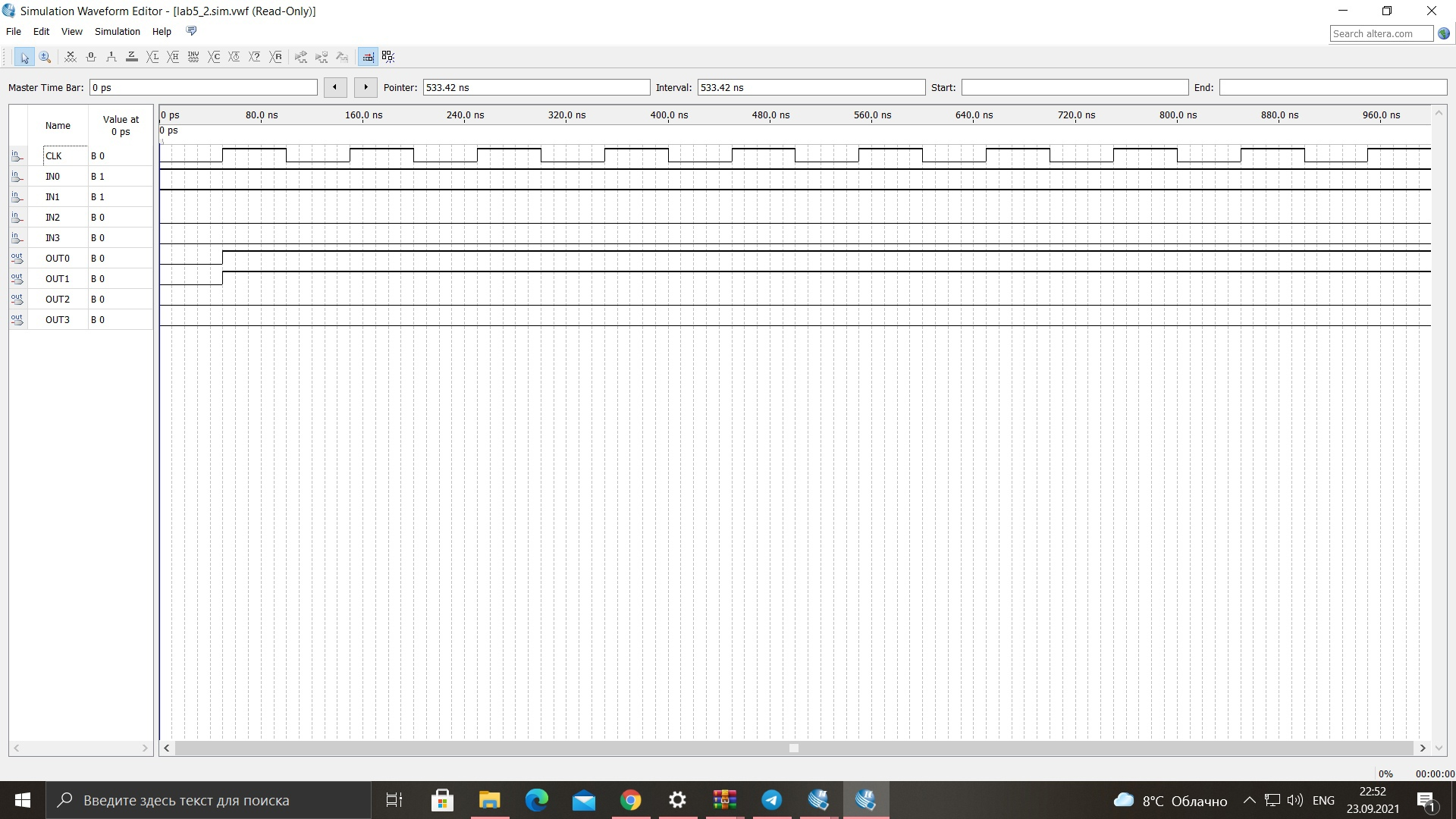

Результаты функционального и временного моделирования

На рисунке 3 представлена функциональное моделирование 4-разрядного параллельного регистра.

Рисунок

3 - Результаты функционального

моделирования

Рисунок

3 - Результаты функционального

моделирования

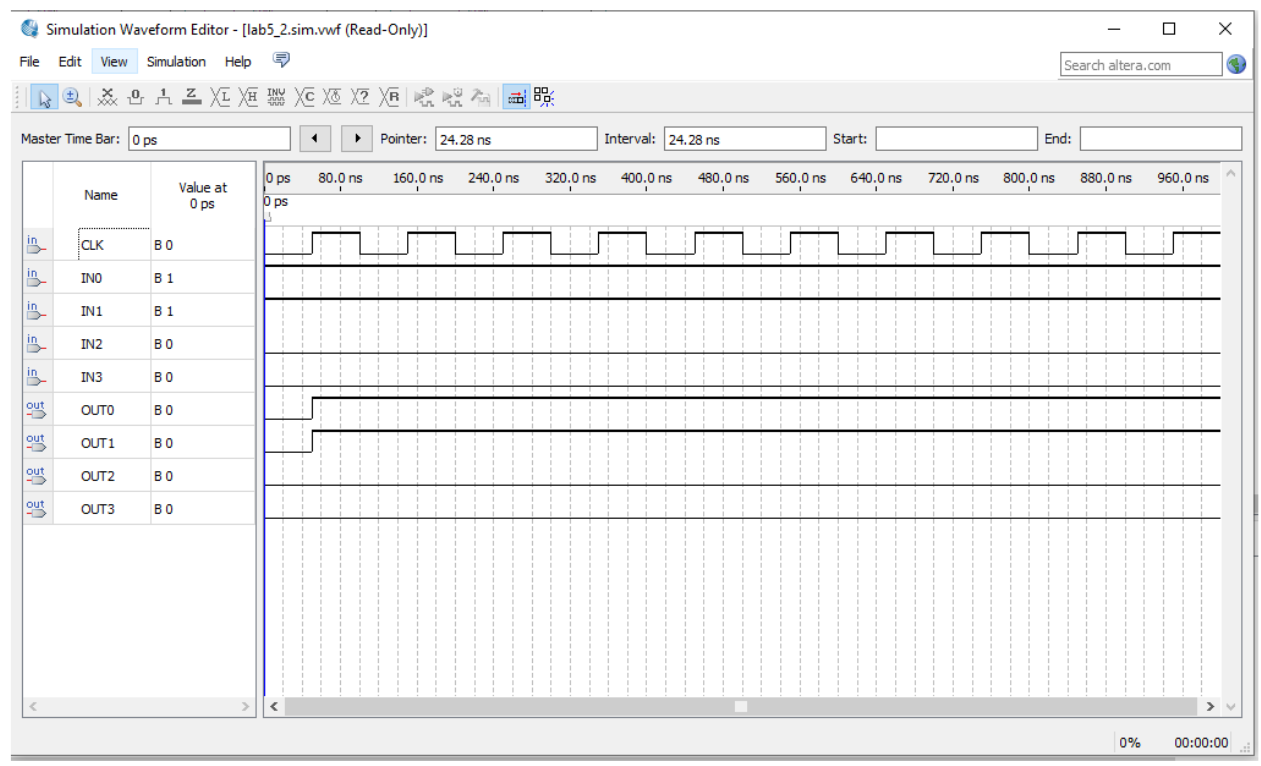

На рисунке 4 представлена функциональное моделирование 4-разрядного параллельного регистра.

Рисунок

4 - Результаты временного моделирования

Рисунок

4 - Результаты временного моделирования

Часть 2

Задание

Предлагается разработать многофункциональный регистр на базе D-триггеров. Закодируем операции, которые необходимо реализовать.

Табл 2.

S0 |

0 |

0 |

1 |

1 |

S1 |

0 |

1 |

0 |

1 |

Обозначение |

I |

S |

R |

L |

Функция |

Параллельная загрузка |

Установка в 1 всех разрядов |

Сдвиг вправо циклический |

Сдвиг влево, заполнение 1 |

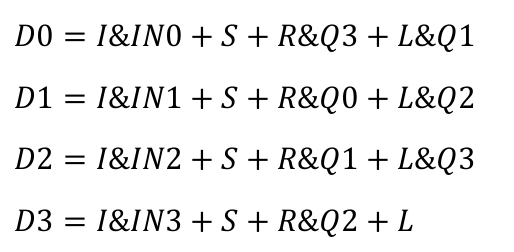

Пусть входные сигналы обозначаются как IN0-IN3, входы триггеров как D0-D3, а выходы триггеров как Q0-Q3. Тогда зададим входы триггеров с помощью формул.

Рисунок

5: Входные функции триггеров

Рисунок

5: Входные функции триггеров

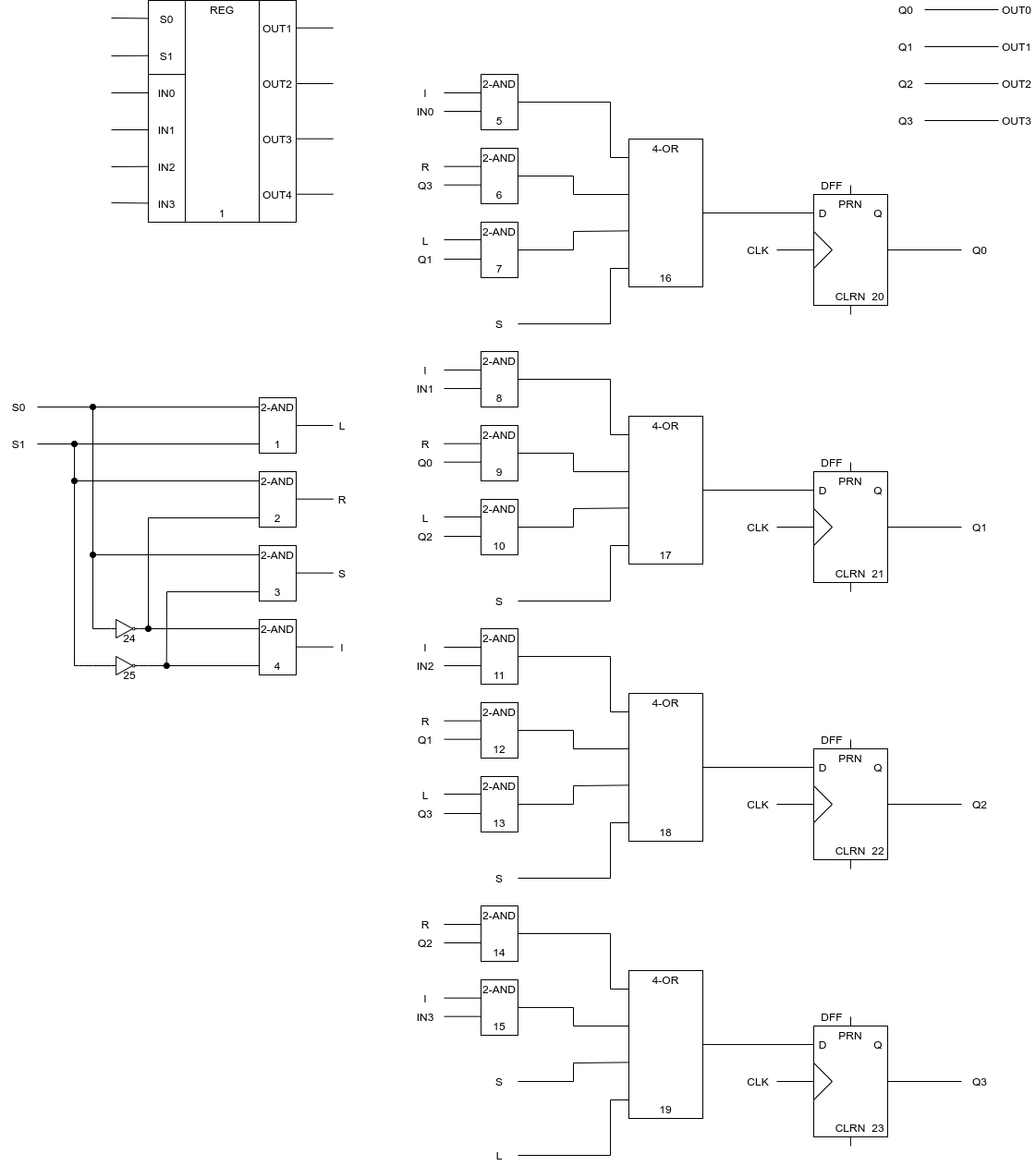

Принципиальная схема

Принципиальная схема многофункционального регистра на базе D-триггеров представлена на рисунке 6.

Рисунок

6 - Принципиальная схема

Рисунок

6 - Принципиальная схема

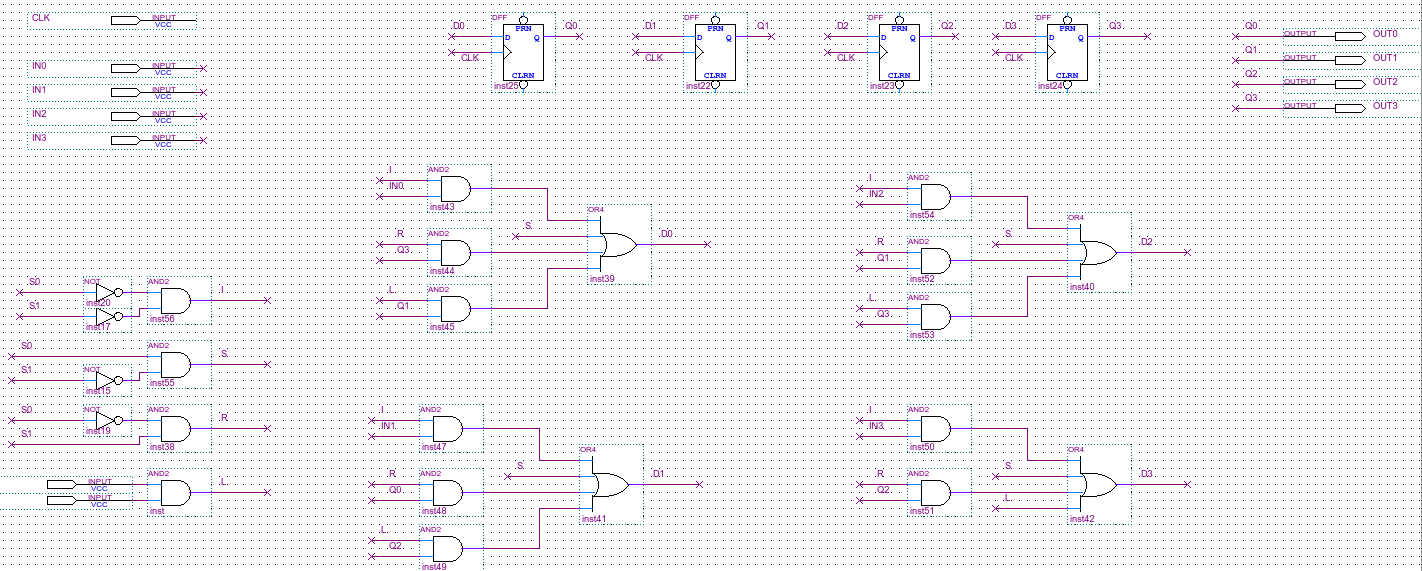

Функциональная узла

Схема многофункционального регистра на базе D-триггеров представлена на рисунке 7.

Рисунок

7 - Функциональная схема

Рисунок

7 - Функциональная схема

Результаты функционального и временного моделирования

Функциональное моделирование многофункционального регистра на базе D-триггеров представлено на рисунке 8.

Рисунок

8 - Результаты функционального

моделирования

Рисунок

8 - Результаты функционального

моделирования

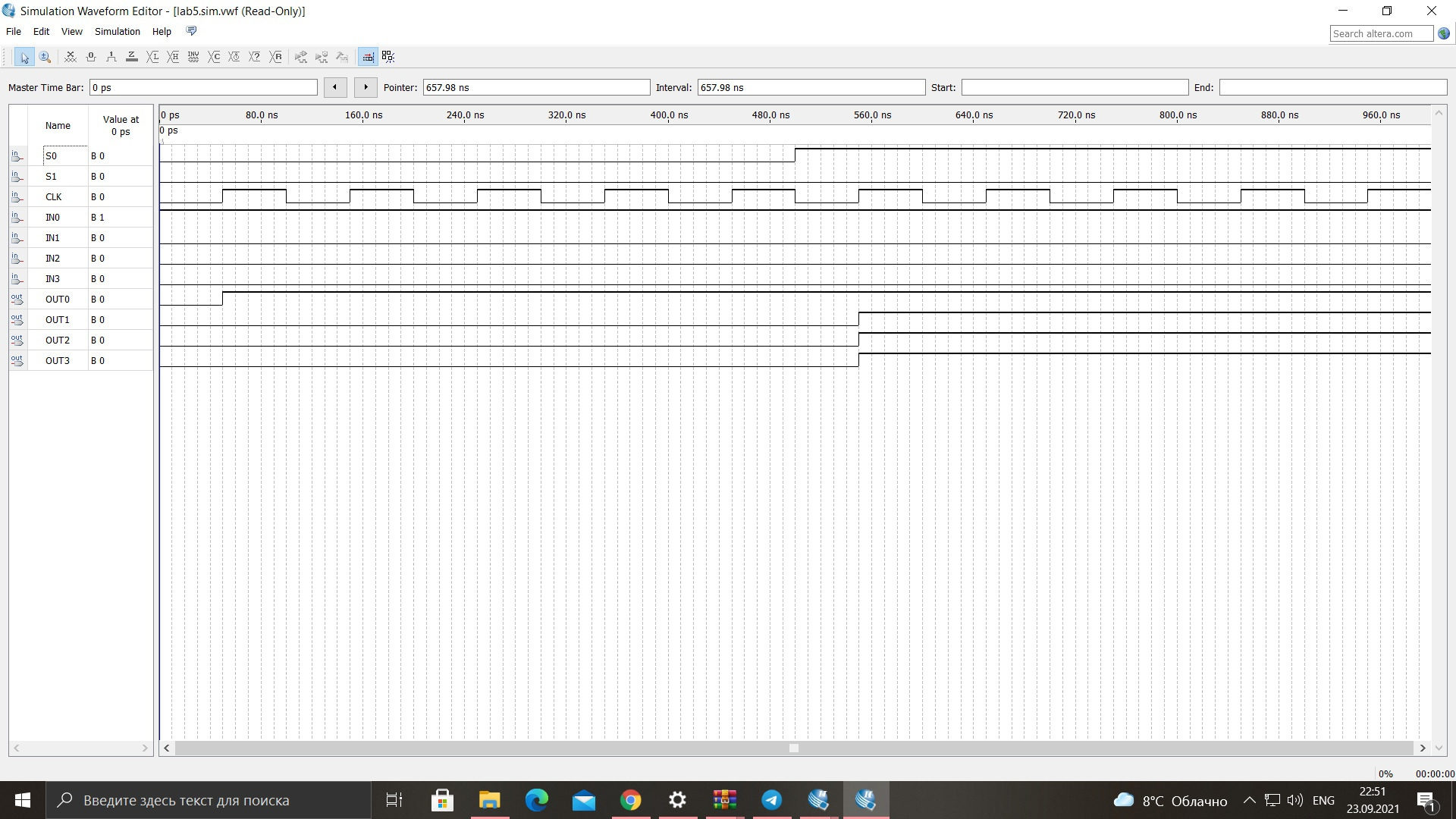

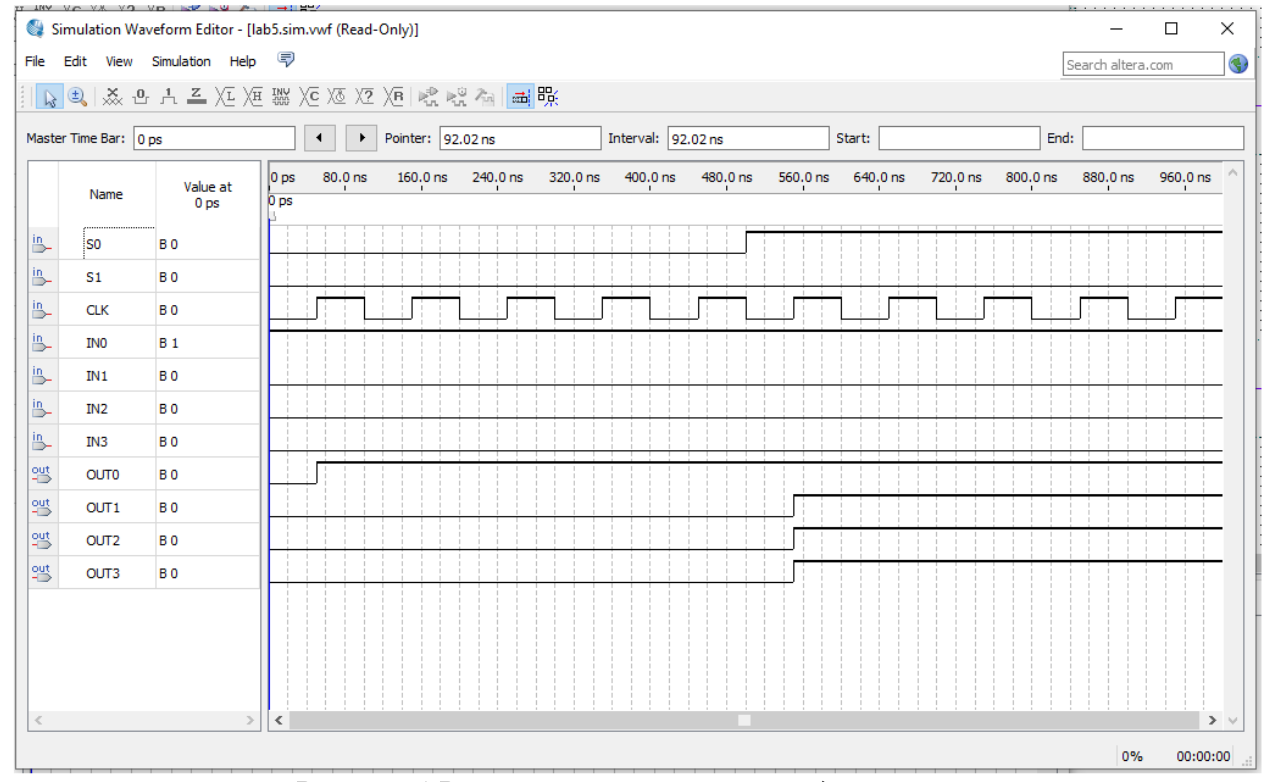

Временное моделирование многофункционального регистра на базе D-триггеров представлено на рисунке 9.

Рисунок

9 - Результаты временного моделирования

Рисунок

9 - Результаты временного моделирования

Описание процесса макетирования

Схема проекта была дополнена таким образом, чтобы обеспечить понижение частоты входного тактового сигнала с помощью специально добавленного счетчика для того, чтобы можно было комфортно наблюдать работу регистра при выполнении сдвигов. Загрузили проект в учебную плату. Данные, загружаемые в регистр, и код микрооперации формировали на движковых переключателях. Результаты работы проекта наблюдали на светодиодной линейке. Перебрали на переключателях входные значения и проверили работу многофункционального регистра. Схема работала корректно.

Выводы

В данной лабораторной работе мы исследовать особенности проектирования регистров различного типа, закрепить навыки синтеза и экспериментального исследования узлов в среде Quartus II.