Лабы / лаба 1 узлы

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №1

по дисциплине «Узлы и устройства СВТ»

Тема: Знакомство с системой проектирования Quartus II,

реализация комбинационной схемы

Вариант - 3

Студенты гр. 8308 |

|

Шубинов Р. В. Треско М.Ю. |

Преподаватель |

|

Бондаренко П.Н. |

Санкт-Петербург

2021

Цель работы

Освоение процесса проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающего в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента. В процессе работы выполняется проектирование простой комбинационной схемы.

Выполнение работы

Таблица истинности заданной функции:

X4 |

X3 |

X2 |

X1 |

f |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

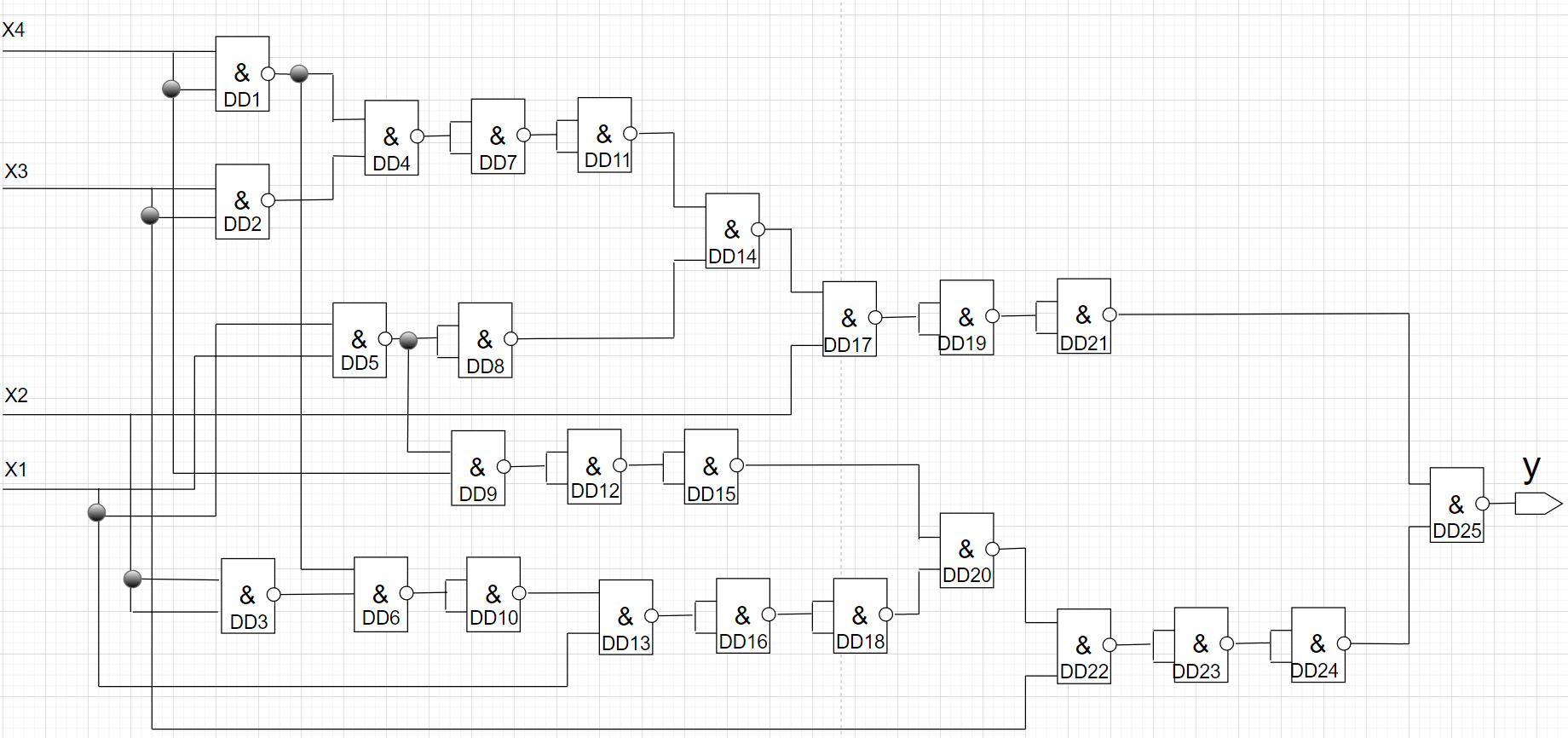

Функциональная схема

Рисунок 1. Функциональная схема, выполненная в Quartus II

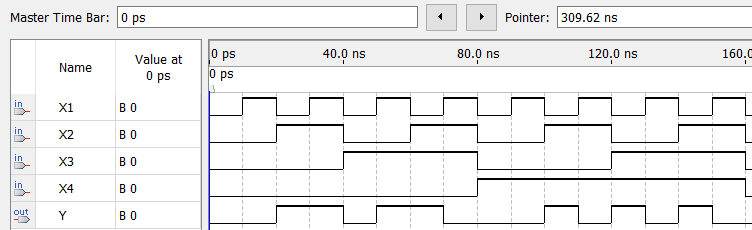

Результаты функционального и временного моделирования

Результаты функционального моделирования (без учёта задержек):

Рисунок 2. Результаты функционального моделирования

Результаты временного моделирования:

Рисунок 3. Результаты временного моделирования

Функциональное моделирование позволяет проверить выход функции перебором всех возможных значений функции, а временное моделирование при этом учитывает ещё и временные задержки по срабатыванию элементов (фронты выхода смещены относительно входа).

Выводы

Мы освоили процесс проектирования цифровой схемы в системе автоматизированного проектирования Quartus II, включающего в себя этапы создания цифровой схемы в графическом редакторе, моделирования работы схемы, загрузки результатов проектирования в программируемую логическую интегральную схему и проведение макетного эксперимента.