Реализация алгоритмов цифровой обработки сигналов в базисе программируемых логических интегральных схем. Строгонов А.В

.pdf

Рис. 1.17. Принцип умножения методом правого сдвига и сложения. Умножение десятичного числа 10 на десятичное число 11

Рис. 1.18. Структурная схема умножителя методом правого сдвига и сложения

31

32

Рис. 1.19. Структурная схема метода умножения с использованием управляющего автомата

32

1.4.2. Умножение целых чисел со знаком методом правого сдвига и сложения

Рассмотрим пример последовательностного универсального умножителя целых чисел, представленных в дополнительном коде, методом правого сдвига и сложения (MAC-блок) в базисе ПЛИС.

Рассмотрим умножение чисел со знаком в “столбик” (рис. 1.20). Дополнение до двух можно получить, если прибавить 1 к результату обращения. Обращение логически эквивалентно инверсии каждого бита в числе. Вентили Исключающее ИЛИ можно применить для избирательной инверсии в зависимости от значения управляющего сигнала. Прибавление 1 к результату обращения можно реализовать, задавая 1 на входе переноса сумматора.

На рис. 1.20 показан принцип умножения чисел представленных дополнительным кодом, на примере умножения -5x-3. Представление процесса умножения в точечной нотации, в которой под каждой точкой подразумевается логическая 1 или логический 0, позволяет получить рекуррентную формулу (рис. 1.21).

Ниже показаны примеры умножения, рассматриваемые при разработке схемы универсального умножителя.

Случай 1. |

|

|

Случай 2. |

Множимое |

- |

отрицательное |

Множимое и множитель - |

число |

|

|

отрицательные числа |

Множитель |

- |

положительное |

-10x-11 |

число |

|

|

|

-10x11 |

|

|

|

Случай 3. |

Случай 4. |

|

|

Множимое и множитель |

- Множимое |

- |

положительное |

четные отрицательные числа |

число |

|

|

-4x-4 |

Множитель |

- |

отрицательное |

|

число |

|

|

|

5x-3 |

|

|

|

33 |

|

|

34

Рис. 1.20. Умножение в столбик (а); умножение методом сдвига множимого и последующего сложения с частичным произведением (умножение чисел -5x-3, представленных в дополнительном коде) (б)

34

Рис. 1.21. Представление процесса умножения методом правого сдвига и сложения в точечной нотации

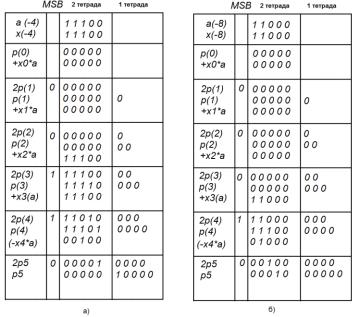

На рис. 1.22 показан принцип умножения методом правого сдвига и сложения для двух случаев. В первом случае осуществляется умножение числа со знаком -10 на число 11, а во втором - умножение -10 на -11. В первом случае множимое (-10) переводится в дополнительный код (дополнение до двух).

Множитель (11) – целое положительное число, расширенное знаковым разрядом 0, представлено в прямом коде. Для удвоенных частичных произведений 2p(1), 2p(2), 2p(3), 2p(4) и 2p(5) в поле MSB (название полей произвольное) необходимо добавить логическую 1. При формировании частичных произведений методом правого сдвига p(1), p(2), p(3), p(4) и p(5) логическая 1 из поля MSB попадает в старший разряд второй тетрады (название “тетрады” в данном случае не корректно, т.к. это поле уже 5-разрядное, но сохранено для приемлемости с принципом умножения без знаковых чисел).

При сложении p(3) c x3*a единица переноса в старший разряд, т.е. в поле MSB, игнорируется. Данная схема

35

вычислений справедлива только для случая, когда в младшем разряде множителя находится 1.

Рис. 1.22. Принцип умножения методом правого сдвига и сложения:

а) умножение -10x11; б) умножение -10x-11

При умножении двух отрицательных чисел, представленных дополнительным кодом (например, -10x-11), необходимо произвести два действия. Первое, необходимо учесть знак при представлении числа в дополнительном коде, что достигается обращением произведения старшего разряда множителя на множимое с последующим прибавлением 1 к младшему разряду. Дополнительный код произведения (–x4*a) при x4=1 есть число 10. Перевод в дополнительный код произведения (–x4*a) должен быть осуществлен до операции

36

сложения, т.е. до получения удвоенного частичного произведения 2p(5).

Второе, при формировании удвоенного частичного произведения 2p(5) необходимо произвести коррекцию, т.е. в поле MSB поставить логический ноль.

Рассмотрим умножение четных чисел со знаком (рис. 1.23). При умножении -4x-4 в поле MSB для удвоенных значений частичных произведений 2p(1) и 2p(2) должны стоять нули. А при умножении -8x-8 нуль в поле MSB должен быть еще 0 и для частичного произведения 2p(3). Далее, принцип умножения не отличается от умножения чисел, представленных дополнительным кодом (например, -10x-11).

Рис. 1.23. Принцип умножения методом правого сдвига и сложения: а) умножение -4x-4; б) умножение -8x-8

37

На рис. 1.24 показан принцип умножения методом правого сдвига и сложения в случае, когда множимое – положительное, а множитель - отрицательное числа.

Рис. 1.24. Принцип умножения методом правого сдвига и сложения: а) умножение 5x-3; б) умножение 2x-2

На рис. 1.25 показан принцип умножения чисел без знака. Единица переноса при сложении в поле “2 тетрада” уже не игнорируется, а переносится в поле Cout (сигнал Cout является выходом переноса многоразрядного сумматора масштабирующего аккумулятора).

38

Рис. 1.25. Принцип умножения методом правого сдвига и сложения. Умножение 15x15

1.5. Программные умножители в базисе ПЛИС

В ПЛИС для повышения их функциональных возможностей встраивают, например, для серии Cyclone III фирмы Altera аппаратные умножители, которые могут быть сконфигурированы в виде одного умножителя 18x18 либо в виде двух умножителей 9x9. Так, ПЛИС EP3CLS200 содержит 396 аппаратных умножителей 18x18, а на оставшихся ресурсах может быть реализован 891 программный умножитель 16x16. В итоге суммарное число умножителей составляет 1287 без какого-либо значительного использования логических ресурсов.

Для устройств цифровой обработки сигналов себя хорошо зарекомендовали софт-умножители (программные умножители), которые не требуют ресурсов аппаратных

39

умножителей, встроенных в базис ПЛИС. Повысить производительность устройств цифровой обработки сигналов позволяет также использование параллельного векторного умножителя и “безумножительных” схем умножения с использованием основ распределенной арифметики.

Рассмотрим параллельные программные умножители, способные вычислять произведение за один такт синхроимпульса, обеспечивая наивысшую производительность устройств цифровой обработки сигналов. Программные умножители БИС программируемой логики (БИС ПЛ) фирмы

Actel серий Fusion, IGLOO и ProASIC3 реализуются на блочной памяти меньшей размерности, чем у ПЛИС фирмы Altera и их можно рассматривать как 8-входовые LUT или таблицы произведений. Таблица произведений множимого, записанная во фрагмент блочной памяти, и называется LUT. Табл. 1.4 показывает умножитель размерностью 3x3, реализованный с помощью 6-входовой LUT.

Таблица 1.4 Умножитель размерностью 3x3, реализованный с

помощью 6-входовой LUT

Например, у ПЛИС фирмы Actel используется ОЗУ емкостью 256 слов x 8 бит (256 8-разрядных слов), а у ПЛИС фирмы Altera может использоваться память M4K, которая может быть сконфигурирована, как 128 слов x 36 бит или 256

40