Учебное пособие 800578

.pdf

рассматриваемого графа, но уже с использованием двух макроблоков. В первом случае 4 уровня вложенности требуют большее время вычислений, во втором 2 уровня требуют меньшее время, но большее число ЛЭ.

Рис.2.29.

Граф

связанности LUT-таблиц для реализации булевой функции в одном макроблоке. Первый уровень упаковки логики

Рис.2.30.

Второй

уровень

упаковки

логики

111

Рис.2.31. S1-маршрутизатор межсоединений L-1 с длиной сегментации в 1 ЛЭ; S2маршрутизатор межсоединений L-4 с длиной сегментации в 4 ЛЭ; Switch matrix – локальная матрица коммутации межсоединений, подключает входы/выходы Супермакроблока к трассировочным каналам

112

В основе ПЛИС NATURE (hybrid CMOS/NanoTUbe REconfigurable architecture, NATURE) типа ППВМ лежит одноуровневая структура межсоединений (рис.2.31). Для достижения компромисса задержка распространения сигнала/площадь кристалла используются L-1, L-4 и длинные линии, пересекающие весь кристалл. Предполагается, что используется 100 нм КМОП-технологический процесс, поэтому длина нанотрубок будет составлять 100 нм. Время реконфигурации одной LUT-таблицы составляет 160 пс, величина, значительно меньше времени задержки распространения сигнала в трассировочных ресурсах обычных ПЛИС.

Логический блок содержит локальную матрицу межсоединений и супермакроблок (рис.2.32). Соседние супермакроблоки связаны между собой прямыми межсоединениями (Direct link). Используется двухуровневая архитектура кластера (Супермакроблока). Кластер состоит из четырех макроблоков. Каждый макроблок состоит из 4 логических элементов (ЛЭ, LE). ЛЭ: 4-x входовая LUTтаблица и программируемый триггер. Для конфигурации ЛЭ требуется 17 бит конфигурационной NRAM-памяти, которые считываются последовательно. NRAM-память входящая в состав ЛЭ приблизительно занимает 21 % от площади макроблока при использовании 100 нм КМОП-технологии. До начала работы ПЛИС, конфигурационные данные в NRAM перезагружаются из внешней памяти.

Программируемый коммутатор 12x4 (соединительный блок) подключает собственные входы/выходы и выходы (комбинационный и регистерный) от трех соседних ЛЭ к своим собственным входам. Для программирования коммутатора требуются 48 бит памяти СОЗУ, которые перезагружаются из энергонезависимой NRAM-памяти, которая играет роль реконфигурируемой памяти. Емкость блока NRAM-памяти макроблока 65 бит.

113

а)

б)

Рис.2.32. а) Макроблок (MB) и б) Супермакроблок (SMB)

ПЛИС с NRAM

114

Кластер состоит из 16 ЛЭ. Входами каждого из макроблоков являются 16 сигналов из локальной матрицы коммутаций и 32 выхода четырех макроблоков в кластере, которые объединяются во внутрикластерную локальную шину и подключаются к локальной матрице. В кластере используются коммутаторы 48x16.

В качестве альтернативы можно рассмотреть серию

Tabula (www.tabula.com) компании Abax - псевдо-3D ПЛИС,

работающие как 8 стекированных кристаллов. По оценкам разработчиков Tabula, еѐ кристаллы более чем в три раза меньше по плоскости, чем эквивалентные ПЛИС, что делает их в 5 раз дешевле при производстве, предоставляя при этом удвоенную плотность логики и почти в 4 раза более высокую производительность. Как и в случае с ПЛИС типа ППВМ, ПЛИС компании Tabula содержат множество идентичных базовых логических блоков, которые могут быть запрограммированы на выполнение любой нужной логической функции. Встроенная память ПЛИС хранит конфигурацию слоѐв, на которые он переключается. Однако энергопотребление таких ПЛИС будет относительно высоким.

3D мемристорные (CMOL FPGA, mrFPGA) ПЛИС.

Рассмотрим один из вариантов реализации ПЛИС типа ППВМ с использованием энергонезависимой резистивной памяти

(http://ru.wikipedia.org/wiki/Мемристор). Мемристор (англ. memristor, от memory - ―память‖, и resistor - ―электрическое сопротивление‖) - пассивный элемент в микроэлектронике, способный изменять свое сопротивление. Может быть описан как двухполюсник с нелинейной вольт-амперной характеристикой, обладающий гистерезисом.

Теория мемристора была создана в 1971 году профессором Леоном Чуа. Устанавливает отношения между интегралами по времени силы тока, протекающего через элемент, и напряжения на нем. Долгое время мемристор считался теоретическим объектом, который нельзя построить.

115

Однако лабораторный образец мемристора был создан в 2008 году коллективом ученых во главе с Р.С. Уильямсом в исследовательской лаборатории фирмы Hewlett-Packard.

В отличие от теоретической модели, устройство не накапливает заряд, подобно конденсатору, и не поддерживает магнитный поток, как катушка индуктивности. Работа устройства обеспечивается за счет химических превращений в тонкой (5 нм) двухслойной пленке двуокиси титана. Один из слоев пленки слегка обеднен кислородом, и кислородные дырки мигрируют между слоями под действием приложенного

кустройству электрического напряжения. Данную реализацию мемристора следует отнести к классу наноионных устройств. Сопротивление мемристора можно существенно (на три порядка) изменять, пропуская через него ток. Изменение сопротивления эквивалентно переключению между единичным и нулевым состоянием, что и наделяет новый элемент свойством памяти. Энергия затрачивается только в момент переключения.

Наблюдающееся в мемристоре явление гистерезиса позволяет использовать его в качестве ячейки памяти. Блоки СОЗУ могут быть более емкими и быстрыми чем флешпамять. Их умение ―запоминать‖ заряд позволит отказаться от загрузки системы. В памяти компьютера отключенного от питания будет храниться его последнее состояние. Его можно будет включить и начать работу с того места, на котором остановился. Это же свойство позволит отказаться от некоторых компонентов современного ПК, что позволит сделать компьютеры меньше и дешевле. HP предполагает, что

к2012 году мемристоры начнут заменять собою флеш-память, в 2014-2016 - оперативную память и жесткие диски. За последние три года фирма HP накопила около 500 патентов по мемристорам, охватывающих резистивные ОЗУ, память с изменением фазы и другие виды двухвыводных приборов памяти.

116

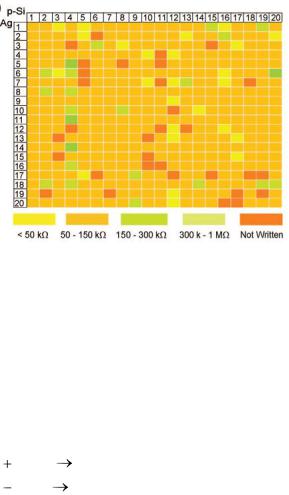

На рис.2.33 показан фрагмент мемристорной коммутационной матрицы емкостью 1К (нанокоммутатор) по совместимому КМОП-технологическому процессу: Ag (верхний) и p-Si (нижний) - наноэлектроды и a-Si (аморфный) в качестве активного переключающего слоя; SiO2 – оксид на подложке; SOG – изоляционное стекло. На рис.2.34 показано тестирование 400 бит информации с использованием специального программного обеспечения. Цвета на карте показывают различные сопротивления точек коммутации в матрице в режиме ON.

Рис.2.33. Фрагмент мемристорной коммутационной матрицы емкостью 1К (нанокоммутатор) по совместимому КМОПтехнологическому процессу: Ag (верхний) и p-Si (нижний) - наноэлектроды и a-Si (аморфный) в качестве активного переключающего слоя; SiO2 – оксид на подложке; SOG – изоляционное стекло

Интеграция нанокоммутатора в ПЛИС позволит обеспечить более эффективную маршрутизацию сигналов и, в конечном счете, к повышению логической емкости и быстродействия. В HP Labs новая технология фигурирует под названием ―программируемые межсоединения на базе нанопроводников‖ (Field Programmable Nanowire Interconnect, FPNI).

117

Рис.2.34.

Тестируется 400 бит информации с использованием специального программного обеспечения. Цвета на карте показывают различные сопротивления точек коммутации в матрице в режиме

ON

Гестеризесный резистивный переключатель, демонстрирующий нелинейную ВАХ, состоит из среды переключения (оксиды переходных металлов), зажатой между двумя электродами (бистабильный резистивный переключатель).

Сопротивление переключателя зависит не только от приложенного напряжения (тока), но и предистории его программирования. Значения сопротивлений мемристора в режимах Включено/Выключено зависит от того, прошло ли напряжение программирования пороговое напряжение записи

Vth ( 0 1, состояние 1) или пороговое напряжение стирания Vth (1 0 , состояние 0) в предыдущем цикле операции.

На рис.2.35 показана концепция создания гибридных КМОП/молекулярных устройств, в том числе и ПЛИС (CMOL FPGA, CMOS + MOLecular electronics) типа ППВМ. CMOL

ПЛИС, как и обычная ПЛИС типа ППВМ с симметричной структурой состоит из плиток. В центре плитки находится триггерная ячейка, окруженная 12 базовыми ячейками. Базовая ячейка состоит из инвертора и двух ключей на проходных транзисторах, которые подключены к строкам и столбцам

118

системы адресации и передачи данных КМОП-структуры и имеют контакты к верхнему (синяя точка) и нижнему нанопроводникам (красная точка). В процессе конфигурации инверторы выключаются, и проходные транзисторы могут быть использованы для установки двоичных состояний каждого молекулярного устройства. Зеленой точкой обозначены молекулярные переключатели (наноприборы).

а)

а)

б) в)

Рис.2.35. Нанокоммутатор (а); б) – приборная структура и ВАХ резистивного ключевого элемента с гистерезисным эффектом (в); г) КМОП-стек с нанокоммутатором; д) гибридная КМОП ПЛИС (CMOL FPGA); д) нескоммутированные элементы гибридной ПЛИС: базовая ячейка и триггерная ячейки; ж) – реализация логического элемента 2 ИЛИ-НЕ и эквивалентные схемы двух наноприборов в состоянии ON, проходного ключа и межсоединения

119

г) |

д) |

е)

Рис.2.35. Продолжение

120