Учебное пособие 800324

.pdf

пряжение. Удельная емкость затвор – канал C0 определяется формулой:

C0 = 0/h, |

(3.3) |

где h – толщина подзатворного диэлектрика.

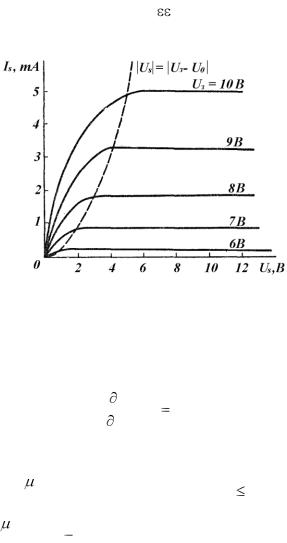

Рис. 3.2. Семейство выходных вольтамперных характеристик МДП транзистора с каналом n-типа

Усилительные свойства полевого транзистора определяются крутизной характеристики S, которая выражает изменение тока от изменения входного напряжения:

S = |

I s |

|

|

s |

const |

(3.4) |

|

|

U |

||||||

U 3 |

|||||||

|

|

|

|

|

|||

В пологой области вольтамперной характеристики крутизна равна

|

S= |

C0b |

Us = S0Us |

при Us Uз – U0, (3.5) |

|

|

|

|

|||

|

|

|

l |

|

|

S= |

C0b |

(U ç U 0 ) = S0(Uз – U0) при Us > Uз – U0, (3.6) |

|||

|

|||||

|

l |

|

|

|

|

Крутизна в этой области может быть увеличена одним из двух способов: либо уменьшением напряжения на затворе, либо изменением геометрии прибора – отношения ширины канала к его длине.

19

Типичные значения величины крутизны для отдельных МДП транзисторов лежат в пределах 0,5 – 2,0 мА/В.

Удельная крутизна характеристики S0 = d2Is/dU2з рассчитывается по формуле

|

S0 = |

|

С0b/l . |

|

(3.7) |

|||||||

Пороговое напряжение находят согласно выражениям: |

||||||||||||

U0 = - ( |

мп |

+ |

Qss |

|

|

Qď |

2 ) |

(3.8а) |

||||

C0 |

|

|

Ń0 |

|||||||||

|

|

|

|

|

|

|

ř |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

для p-канального транзистора и |

|

|

|

|

|

|

||||||

U0 = - |

мп |

- |

|

Qss |

|

|

Qď |

|

2 |

(3.8б) |

||

|

C0 |

|

Ń0 |

|||||||||

|

|

|

|

|

ř |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

для n-канального транзистора. Здесь мп – разность потенциалов, обусловленная разницей работ выхода полупроводника и материала затвора, Qss и Qп – соответственно плотности заряда поверхностных состояний на границе полупроводника и диэлектрика и пространственного заряда в полупроводнике.

Величины Qss и Qп находят по формулам: |

|

|

||||||

|

|

Qss = qNS |

|

|

|

(3.9) |

||

Qп |

= (2 |

0 N0 |

)1/ 2 |

|

|

(3.10) |

||

|

|

|

|

|

ř |

|

|

|

|

ř |

T |

ln N0 / ni |

|

(3.11) |

|||

|

|

|

|

|

|

|

|

|

|

|

T |

kT / q |

|

|

|

(3.12) |

|

|

|

|

|

|

|

|

|

|

Плотность поверхностных состояний для кремния |

|

|||||||

Кристаллографическая |

|

плос- |

|

<111> |

|

<110> |

<100> |

|

кость |

|

|

|

|

|

|

|

|

Qss/q 10-11, cm-2 |

|

|

|

|

5,0 |

|

2,0 |

0.9 |

Пробой в МДП транзисторах

Электрический пробой МДП транзистора может быть обусловлен следующими причинами:

1)пробоем р–n-переходов «сток–подложка», «исток–подложка»;

2)пробоем в канале между истоком и стоком;

3)пробоем окисла под затвором.

20

Пробой р–n-переходов «сток – подложка» и «исток – подложка» обусловлен теми же причинами, что и пробой в диодах.

Пробой в канале между истоком и стоком происходит в области с максимальной напряженностью поля, т. е. в области около стока, и обусловлен лавинным рождением электронно-

дырочных пар. Поскольку эти дырки и электроны ослабляют действие поля в канале, то нарастание тока происходит плавно и в широком диапазоне напряжений. «Мягкая лавина» в канале приводит к уменьшению сопротивления стока в пологой области, что особенно сказывается в приборах с малой длиной канала. Вблизи пробивного напряжения составляющая тока почти незаметно увеличивается с ростов напряжения на затворе. Максимальное напряжение на затворе ограничено пробивным напряжением слоя окисла Vз.пр. Критическое поле в двуокиси

кремния, при котором происходит пробой окисла, равно 106 — 107 В/см.

Когда напряжение на затворе достигает величины Vз.пр, ток резко возрастает, что может привести к разрушению окисла, к потере им изоляционных свойств. Поэтому важно отметить, что из-за высокого сопротивления окисла на затворе может накапливаться заряд статического электричества и вызывать пробой окисла или ухудшение его изоляционных свойств. Наличие заряда в окисле приводит к тому, что величина пробойного напряжения различна для различной полярности.

Контрольные вопросы

1.Поясните устройство и принцип действия полевого транзистора с изолированным затвором и индуцированным каналом.

2.Что такое пороговое напряжение и «инверсия проводимости»?

3.Почему пороговое напряжение n-канального кремневого МДП транзистора меньше, чем р- канального? Влияет ли материал электрода на величину порогового напряжения?

21

4.Поясните выходные ВАХ МДП транзистора, изображенные на рис. 2.1.

5.Что такое крутизна характеристики S и удельная крутизна характеристики S0?

6.На какие параметры транзистора влияет толщина подзатворного диэлектрика? Из каких соображений она выбирается?

7.Можно ли использовать подложку в качестве управляющего электрода транзистора?

8.Назовите основные виды электрического пробоя в МДП транзисторах.

9.Влияет ли напряжение на затворе на напряжение пробоя «сток – подложка»?

10.Перечислите наиболее существенные на ваш взгляд различия между МДП и биполярными транзисторами.

Тема 4. Проблемы изоляция элементов полупроводниковых ИМС

4.1. Изоляция p-n - переходом

4.1.1. Стандартная технология

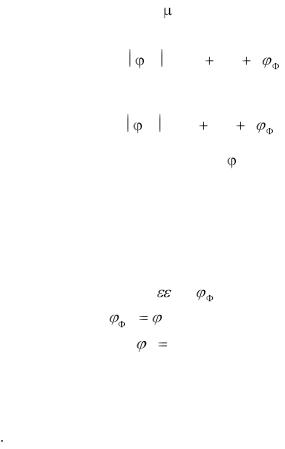

Сущность этой технологии состоит в том, что транзисторные структуры формируют локальной диффузией в эпитаксиальном слое n-типа, нанесенном на пластину р-типа, а изолирующие области создают путем проведения разделительной диффузии на всю глубину эпитаксиального слоя. Последовательность формирования кристалла полупроводниковой ИМС, содержащей транзистор, рассмотрена в разделе 1.

4.1.2. Коллекторная изолирующая диффузия (КИД-технология)

Данная технология основана на использовании тонких эпитаксиальных слоев и коллекторной изолирующей диффузии (вместо разделительной в стандартном процессе).

22

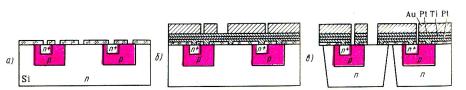

Рис. 4.1. Последовательность формирования полупроводниковой ИМС по КИД-технологии

Сущность КИД-технологии проиилюстрирована на рис. 4.1. По сравнению со стандартной технологией КИДтехнология проще. Технологический цикл изготовления кристаллов сокращается на 1–2 фотолитографические операции, что повышает процент выхода годных ИМС и снижает их стоимость. КИД-технология благодаря простоте изготовления ИМС, большей в 1,5 – 2 раза плотности размещения элементов по сравнению со стандартным процессом, схемной универсальности и высокому быстродействию изготовляемых ИМС получила самое широкое распространение. С ее помощью осуществляют производство большинства типов ИМС.

4.1.3. Базовая изолирующая диффузия (БИД-технология)

В данной технологии формирование изолирующих и базовых областей транзисторов совмещено во времени и осуществляется одновременно. Технологически этот процесс проще КИД-технологии, так как для него требуется только четыре операции фотолитографии.

Процесс изготовлении ИМС по БИД-технологии проиллюстрирован на рис. 4.2.

Несмотря на то, что БИД-технология проще КИДтехнологии, она имеет ограниченное применение, поскольку для функционирования изготовленной по данной технологии ИМС требуется дополнительный источник питания (для обратного смещения изолирующих областей).

23

Рисунок 4.2. Последовательность формирования полупроводниковой ИМС по БИД-технологии

4.2. Изоляция диэлектриком

Диэлектрическая изоляция позволяет создавать ИМС с улучшенными характеристиками по сравнению со схемами, в которых применяется диодная изоляция, а именно: существенно увеличить напряжение пробоя изолирующей области, значительно (примерно на шесть порядков) уменьшить токи утечки, уменьшить (примерно на два порядка) паразитные емкости и в результате увеличить рабочую частоту аналоговых и быстродействие цифровых ИМС, повысить их радиационную стойкость.

4.2.1 ЭПИК-процесс

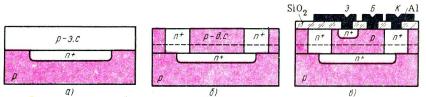

Данная технология основана на получении изолирующих областей из слоев оксида (нитрида) кремния и поликристаллического кремния. В зависимости от последовательности их формирования ЭПИК-технология имеет несколько модификаций. Последовательность формирования простой ИМС на биполярных транзисторах с диэлектрической изоляцией элементов слоем оксида кремния представлена на рис. 4.3.

Вначале составляют партию кремниевых пластин n-типа с удельным сопротивлением 0,2 – 10 Ом·см. Затем в исходных пластинах n-типа диффузией сурьмы или мышьяка на глубину 1 – 2 мкм формируется скрытый n+-слой по всей площади пластины. Путем термического окисления пластин со стороны n+- слоя на поверхности пластины получают маскирующий слой оксида. Методом первой фотолитографии в этом слое создают

24

окна под изоляционные области (рис. 4.3, а), а за счет травления кремния в незащищенных оксидом участках – канавки глубиной 8 – 15 мкм (рис. 4.3, б).

Рис. 4.3. Последовательность формирования полупроводниковой ИМС, изготовляемой по ЭПИК-технологии:1 – исходная пластина кремния n-типа; 2 – диффузионный скрытый

слой n+-типа; 3 – оксид кремния; 4 – поликристаллический кремний (подложка)

Для получения на рельефной поверхности пластины слоя оксида толщиной около 1 мкм используют пиролиз силана или термическое окисление (рис.4.3, в). На поверхности пластин со стороны окисленных канавок наращивается поликристаллический кремний толщиной ~ 200 мкм (рис. 4.3, г), который является основанием (подложкой) будущей ИМС. После этого с противоположной поверхности пластины (со стороны кремния n-типа) сошлифовывают или стравливают слой монокристаллического кремния n-типа до оксидного слоя (рис 4.3, д). Таким образом, получают области кремния n-типа со скрытыми n+-слоями, изолированные друг от друга слоем SiO2. В этих областях методами окисления, фотолитографии и диффузии формируют элементы микросхемы. Дальнейший процесс изготовления, начиная с формирования базовых областей, проводят аналогично планарно-эпитаксиальному.

25

Данный технологический процесс позволяет получить хорошую изоляцию между элементами как по постоянному, так и по переменному току, поскольку емкость, образованная слоем оксида, может быть очень малой (30 пФ/мм2 при слое оксида кремния толщиной 1 мкм). Измеренное сопротивление изоляции превышает 1012 Ом при напряжении 100 В, а пробивное напряжение выше 800 В для слоя толщиной 1 мкм. Кроме того, ЭПИК-технология дает возможность изготовлять на одном кристалле высокочастотные и низкочастотные диоды, используя селективную диффузию золота, а также облегчает получение на одном кристалле транзисторов типов n-p-n и p-n-p. По такой технологии целесообразно изготовлять микромощные и быстродействующие цифровые и высокочастотные аналоговые ИМС. Но стоимость технологического процесса при этом высока по сравнению с процессами изоляции р-n-переходами.

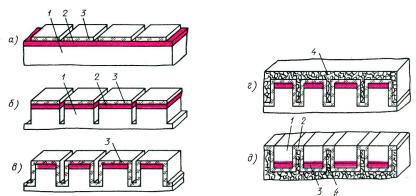

4.2.2. Декаль-метод

Эта технология основана на создании изоляции воздушными зазорами, с помощью которых элементы ИМС отделены друг от друга с боковых сторон. При этом элементы ИМС удерживаются на едином конструктивном основании. По де- каль-технологии изготовляют ИМС с балочными выводами, которые исполняют роль электрических соединений и механической опоры кристалла.

Рис. 4.4. Изготовление биполярных ИМС с изоляцией воздушными зазорами и балочными выводами: а) – формирование элементов; б) – изготовление балочных выводов; в) – ло-

кальное травление

26

По такой технологии (рисунок 13) сначала формируют элементы ИМС (рис. 4.4, а), затем создают систему соединений, используя слои титана, платины и золота (рис. 4.4, б), после чего с обратной стороны пластины локальным травлением удаляют лишние участки между элементами (рис. 4.4, в).

Достоинством технологии является отсутствие механической обработки и высокотемпературных процессов на этапе формирования изолирующих областей.

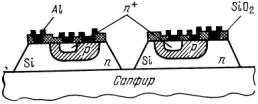

4.2.3. КНС-технология

Весьма перспективная технология кремния на сапфире является разновидностью технологии с воздушной изоляцией. В этой технологии используется техника гетероэпитаксии кремниевых слоев на сапфировых или шпинелевых подложках. Кремниевые слои осаждаются из парогазовой фазы путем термического разложения моносилана SiH4. Затем с помощью фотолитографии проводят локальное травление полученных гетероэпитаксиальных пленок кремния. На подложке остаются «островки» монокристаллического кремния, в которых далее формируют элементы полупроводниковых микросхем (рис. 4.5).

Рис. 4.5. Структура транзисторов на сапфировой подложке

Микросхемы, полученные с использованием технологии КНС, отличаются малыми паразитными емкостями (до 0,1 – 0,2 нФ/мм2) и высокими рабочими частотами (до 4 ГГц). Широкому применению этой технологии препятствуют высокая стоимость подложек и образование в кремниевых гетероэпи-

27

таксиальных пленках большого числа кристаллографических дефектов (107 – 109 см-2).

4.3. Комбинированная изоляция элементов

Комбинированная изоляция сочетает технологичность изоляции p-n-переходом и высокие качества изоляции диэлектриком. Изоляция p-n-переходом заменяется изоляцией диэлектриком в наиболее уязвимом приповерхностном слое и с боковых сторон.

Наибольшее распространение получили такие способы комбинированной изоляции, как локальное окисление (изопланарная технология) и вертикальное анизотропное травление (полипланарная технология). В основе этих технологий лежит локальное сквозное окисление или протравливание тонкого эпитаксиального слоя кремния n-типа, в результате чего этот слой оказывается разделенным на островки. Современные биполярные БИС и СБИС, изготавливаемые способами комбинированной изоляции, обладают достаточно высокими характеристиками изоляции. Преимуществом этой изоляции является возможность достижения высокой степени интеграции ИМС.

4.3.1 Изопланарная технология

Процессы изопланарной технологии основаны на использовании кремниевых пластин с тонким (2 – 3 мкм) эпитаксиальным слоем, селективного термического окисления кремния на всю глубину эпитаксиального слоя вместо разделительной диффузии, проводимой в обычном планарно-эпитаксиальном процессе. Реализация такого процесса достигается использованием при маскировании на первых стадиях формирования структуры ИМС специфических свойств нитрида кремния Si3N4. Нитрид кремния препятствует превращению кремния в SiО2 в местах, где Si3N2 служит в качестве защитного слоя. Кроме того, нитрид кремния легко удаляется травителем на основе фосфорной кислоты, который не воздействует на ок-

28