- •В.В. Болгов, в.И. Енин, а.В. Смольянинов

- •Схемотехника

- •В.В. Болгов, в.И. Енин, а.В. Смольянинов Схемотехника

- •Схемотехника

- •Введение

- •После изучения дисциплины необходимо знать:

- •После изучения дисциплины необходимо уметь:

- •В.1. Роль и место курса “Схемотехника” в учебном процессе

- •В.2. Основные направления развития цифровых устройств

- •В.3. Самостоятельная работа студентов и контроль знаний

- •1 . Основы теории логических функций.

- •1.1. Логические функции

- •1.2. Основные законы и тождества алгебры логики

- •1.3. Формы представления логических функций

- •Совершенная дизъюнктивная нормальная форма

- •Совершенная конъюнктивная нормальная форма

- •Получение логических выражений скнф и сднф

- •1.4. Минимизация логических функций

- •Метод Квайна

- •Метод карт Вейча

- •1.5. Построение и анализ работы логических схем

- •1.6. Построение логических схем с несколькими выходами

- •1.7. Вопросы и задания для самоконтроля

- •2. Интегральные микросхемы

- •2.1. Технологии цифровых интегральных схем

- •2.2. Параметры интегральных микросхем

- •2.3. Логические элементы транзисторно-транзисторной логики

- •2.3.1. Входные каскады ттл микросхем

- •2.3.2. Типы выходных каскадов ттл цифровых элементов

- •Логический выход

- •Элементы с тремя состояниями

- •Выходные каскады с открытым эмиттером

- •Выход с открытым коллектором

- •Основные характеристики микросхем ттл серий

- •2.4. Логические элементы эмиттерно-связанной логики

- •2.5. Логические элементы на моп‑транзисторах

- •2.6. Кмоп микросхемы

- •2.6.1. Режим неиспользуемых входов

- •2.6.2. Преобразователи уровня

- •2.7. Простейшие интегральные микросхемы

- •2.8. Шинные формирователи и приемопередатчики

- •2.9. Вопросы и задания для самоконтроля

- •3. Устройства комбинационного типа

- •Двоичные шифраторы и дешифраторы

- •3.1.1. Разработка схемы шифратора и его работа

- •3.1.2. Приоритетный шифратор

- •3.1.3. Разработка схемы дешифратора и его работа

- •3.1.4. Преобразователи кодов

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Демультиплексоры

- •3.2.3. Получение мультиплексоров и демультиплексоров на большое количество входов (выходов)

- •3.2.4. Универсальные логические модули

- •3.2.5. Совместная работа мультиплексора и демультиплексора

- •3.3. Сумматоры, алу и матричные умножители

- •3.3.1. Одноразрядный сумматор

- •3.3.2. Сумматор последовательного действия

- •3.3.3. Сумматор параллельного действия с последовательным переносом

- •3.3.4. Сумматор параллельного действия с параллельным переносом

- •3.3.5 Арифметико-логические устройства

- •3.3.6. Матричные умножители

- •3.4. Компараторы

- •3.5 Схемы контроля

- •3.6. Вопросы и задания для самоконтроля

- •4. Узлы последовательностного типа

- •4.1. Триггеры

- •4.1.1. Асинхронные триггеры

- •4.1.2. Асинхронный d-триггер

- •4.1.3. Синхронные триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Триггеров

- •4.1.4. Триггеры с двухступенчатым запоминанием информации

- •4.1.6. Счетный триггер

- •4.1.7. Динамические триггеры

- •4.1.8. Установка начального значения триггера

- •4.1.9. Триггеры Шмидта

- •4.2. Регистры

- •4.2.1. Параллельный регистр

- •4.2.2. Последовательные (сдвигающие) регистры

- •4.2.3. Взаимное преобразование числа из последовательного кода в параллельный

- •4.3. Счётчики

- •4.3.1. Суммирующие счетчики

- •4.3.2. Вычитающие счетчики

- •4.3.3. Реверсивные двоичные счетчики

- •4.3.4. Кольцевые счетчики

- •4.3.5. Условное обозначение счетчиков

- •4.3.6. Быстродействие счетчиков

- •4.3.7. Программирование счетчиков

- •4.4. Вопросы и задания для самоконтроля

- •5. Аналого-цифровые и цифро-аналоговые преобразователи

- •5.1. Аналого-цифровые преобразователи

- •5.1.1. Принцип аналого-цифрового преобразования

- •5.1.2. Ацп с промежуточным преобразованием во временной интервал

- •5.1.3. Аналого-цифровой преобразователь с обратной связью

- •5.1.4 Аналого-цифровой преобразователь следящего типа

- •5.1.5. Параллельный ацп

- •5.1.6. Интегрирующие ацп

- •5.1.7. Ацп последовательных приближений

- •5.2. Цифро-аналоговые преобразователи

- •5.3. Преобразователи интервалов времени

- •5.4. Вопросы для самоконтроля

- •6. Устройства хранения информации

- •6.1. Основные характеристики запоминающих устройств

- •6.2. Оперативные запоминающие устройства

- •6.2.1. Статические озу

- •6.2.2. Динамические озу Принцип действия динамических озу

- •Схемные особенности динамических озу

- •6.3. Постоянные запоминающие устройства

- •Масочные пзу

- •Программируемые пзу

- •6.4. Перепрограммируемые запоминающие устройства

- •Флэш-память

- •6.5. Вопросы для самоконтроля

- •7. Селекторы импульсных сигналов

- •7.1. Амплитудные селекторы

- •7.1.1. Селектор максимального уровня

- •7.1.2. Селектор минимального уровня

- •7.2. Временные селекторы

- •7.3 Селекторы импульсов по длительности

- •7.3.1. Селекторы максимальной длительности

- •7.3.2. Селекторы минимальной длительности

- •7.4 Элементы задержки и формирователи импульсов

- •7.5. Вопросы для самоконтроля

- •8. Средства отображения информации

- •8.1. Газоразрядные цифровые индикаторы

- •8.2. Знакосинтезирующие индикаторы

- •8.3. Вакуумные люминесцентные индикаторы

- •8.4. Вакуумные накаливаемые индикаторы

- •8.5. Полупроводниковые семисегментные индикаторы

- •8.6. Жидкокристаллические индикаторы (жки)

- •8.7. Матричные индикаторы

- •8.8. Подключение индикаторов к эвм

- •8.9. Вопросы и задания для самоконтроля

- •9. Автоматы

- •9.1. Автомат в системе управления

- •9.2. Структурный автомат

- •9.3. Аппаратная реализация автоматов

- •9.4. Вопросы и задания для самоконтроля

- •Заключение

- •Б иблиографический список

- •ПриложенИя

- •Приложение 1. Обозначения цифровых микросхем

- •Приложение 2. Условные графические обозначения элементов цифровой техники

- •Оглавление

4.3.7. Программирование счетчиков

Рассмотренные схемы счетчиков считают количество импульсов в двоичной системе счисления. Такое изменение состояний выходов триггеров счетчика называют естественным и счетчик характеризуется модулем счета М (числом возможных состояний счетчика) равным 2n, где n – число разрядов счетчика. Емкость такого счетчика зависит от количества триггеров и равна М-1. Можно ввести понятие цикла работы счетчика (коэффициента пересчета), которое определяется минимальным количеством импульсов, поступление которых на счетный вход счетчика приводит его в исходное состояние. Эта величина совпадает с введенным ранее коэффициентом деления и модулем счета.

Чтобы получить иной модуль счета (коэффициент пересчета) и емкость счетчика, надо ввести обратные связи между триггерами таким образом, чтобы изменить естественный порядок смены состояний триггеров. Сделать это можно разными способами.

Можно сделать так, чтобы при состоянии триггеров, когда в счетчике записано число на единицу меньшее требуемого модуля счета (коэффициента пересчета), подготовить обратными связями такие уровни сигналов на входах триггеров, которые с поступлением следующего входного импульса переведут счетчик в исходное (нулевое для суммирующего счетчика) состояние.

Рассмотрим построение счетчика с емкостью десять (десятый импульс должен перевести его в исходное состояние). Для его построения необходимо четыре триггера (меньшее количество триггеров не сможет обеспечить требуемую емкость). Работа такого счетчика описана в таблице 4.13.

Из таблицы видно, что после состояния счетчика 1001 (на вход счетчика поступило девять импульсов) должно наступить состояние 0000, после чего счет начинается заново. Но следующий поступающий на его вход импульс при естественном изменении состояний триггеров должен перевести их выходы в состояние 1010. Таким образом, чтобы задать требуемый порядок изменения состояний триггеров, надо следующим входным импульсом первый и четвертый триггеры перевести в нулевое состояние.

Работа счетчика

Емкостью 10 Таблица 4.13

Номер импульса |

Выходы Q4 Q3 Q2 Q1 |

|||

исх. сост. 1 2 3 4 5 6 7 8 9 10 |

0 0 0 0 0 0 0 0 1 1 0 |

0 0 0 0 1 1 1 1 0 0 0 |

0 0 1 1 0 0 1 1 0 0 0 |

0 1 0 1 0 1 0 1 0 1 0 |

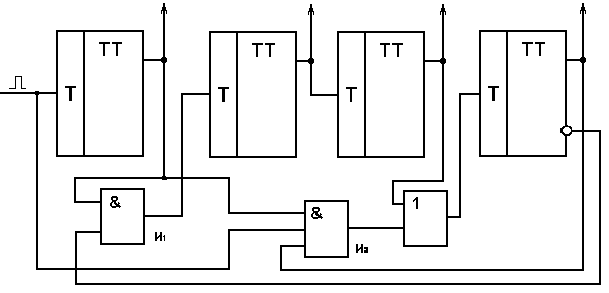

Рис.4.35. Декадный счетчик

До восьмого импульса счетчик работает в естественном порядке смены состояний триггеров. Элемент И1 открыт единичным уровнем с инверсного выхода четвертого триггера.

Импульсы на вход четвертого триггера с выхода третьего проходят через элемент ИЛИ, через который может пройти и импульс с выхода элемента И2. Элемент И2 после девятого входного импульса подготовлен сигналом с прямых выходов первого и четвертого триггеров для того, чтобы пропустить на вход четвертого триггера импульс с входа счетчика, который переведет его в нулевое состояние. После восьмого импульса сигнал нулевого уровня с инверсного выхода четвертого триггера закроет элемент И1 для прохождения на вход второго триггера импульсов с выхода первого, т.к. второй триггер далее не должен переключаться. Первый триггер будет переключаться как и при естественном порядке смены его выходных уровней при поступлении входного импульса.

Таким образом, на входы второго и четвертого триггеров импульсы переключения проходят в зависимости от состояния четвертого триггера: если на его прямом выходе уровень нуля, то они проходят в естественном порядке через схемы И1, И2 и ИЛИ, если уровень логической единицы, то естественный порядок меняется, при поступлении десятого импульса первый и четвертый триггеры перейдут в нулевое состояние и на выходе счетчик будет 0.

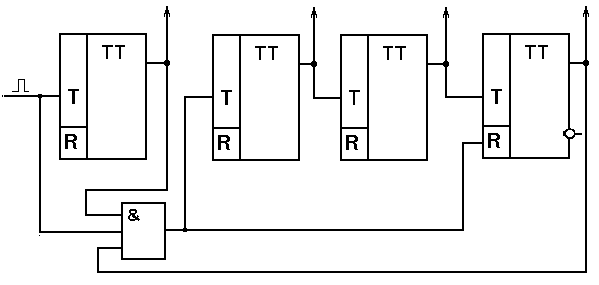

Изменение естественного порядка счета импульсов можно сделать и иначе. Например, можно при поступлении максимального (в нашем случае, десятого) импульса перевести второй и четвертый триггеры в нулевое состояние. Сбрасывать второй триггер необходимо, так как при переходе первого триггера из 1 в 0, что произойдет при поступлении на его вход десятого входного импульса, и второй триггер может перейти в единичное состояние. Сигнал сброса формируется схемой совпадения (логическое И), на которую поступают входной импульс и сигналы с выходов первого и четвертого триггеров. С выхода схемы И сигнал сброса подают на установочные R-входы второго и четвертого триггеров (рис. 4.36). Тогда при поступлении десятого входного импульса, будет сброшен четвертый триггер, а второй триггер не изменит состояния 0.

Рис.4.36. Вариант декадного счетчика

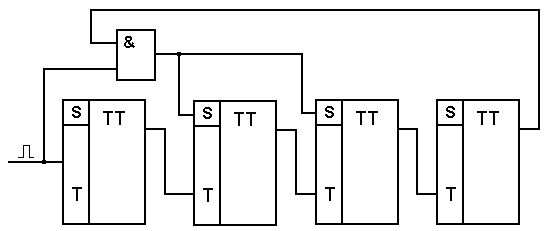

Для реализации декадного делителя частоты можно при поступлении девятого импульса перевести все триггеры в единичное состояние (наполнить счетчик) с тем, чтобы следующий (десятый) импульс записал в нем число 0000. Для этого достаточно после восьмого входного импульса подготовить канал для прохождения управляющего сигнала на установочные входы S, который переведет все триггеры в единичное состояние при поступлении девятого входного импульса (рис. 4.37).

Рис.4.37. Декадный делитель частоты

Такой счетчик до восьмого импульса работает с естественным порядком изменения состояния. Девятый импульс переведет второй и третий триггеры в состояние 1 через элемент И, подготовленный к прохождению входного импульса единичным сигналом с прямого выхода четвертого триггера, при этом первый триггер переведется в единичное состояние входным импульсом, а четвертый останется в этом состоянии. В счетчике окажется записано число 1111. С поступлением десятого импульса все триггеры вернутся в исходное состояние – 0000.