- •В.В. Болгов, в.И. Енин, а.В. Смольянинов

- •Схемотехника

- •В.В. Болгов, в.И. Енин, а.В. Смольянинов Схемотехника

- •Схемотехника

- •Введение

- •После изучения дисциплины необходимо знать:

- •После изучения дисциплины необходимо уметь:

- •В.1. Роль и место курса “Схемотехника” в учебном процессе

- •В.2. Основные направления развития цифровых устройств

- •В.3. Самостоятельная работа студентов и контроль знаний

- •1 . Основы теории логических функций.

- •1.1. Логические функции

- •1.2. Основные законы и тождества алгебры логики

- •1.3. Формы представления логических функций

- •Совершенная дизъюнктивная нормальная форма

- •Совершенная конъюнктивная нормальная форма

- •Получение логических выражений скнф и сднф

- •1.4. Минимизация логических функций

- •Метод Квайна

- •Метод карт Вейча

- •1.5. Построение и анализ работы логических схем

- •1.6. Построение логических схем с несколькими выходами

- •1.7. Вопросы и задания для самоконтроля

- •2. Интегральные микросхемы

- •2.1. Технологии цифровых интегральных схем

- •2.2. Параметры интегральных микросхем

- •2.3. Логические элементы транзисторно-транзисторной логики

- •2.3.1. Входные каскады ттл микросхем

- •2.3.2. Типы выходных каскадов ттл цифровых элементов

- •Логический выход

- •Элементы с тремя состояниями

- •Выходные каскады с открытым эмиттером

- •Выход с открытым коллектором

- •Основные характеристики микросхем ттл серий

- •2.4. Логические элементы эмиттерно-связанной логики

- •2.5. Логические элементы на моп‑транзисторах

- •2.6. Кмоп микросхемы

- •2.6.1. Режим неиспользуемых входов

- •2.6.2. Преобразователи уровня

- •2.7. Простейшие интегральные микросхемы

- •2.8. Шинные формирователи и приемопередатчики

- •2.9. Вопросы и задания для самоконтроля

- •3. Устройства комбинационного типа

- •Двоичные шифраторы и дешифраторы

- •3.1.1. Разработка схемы шифратора и его работа

- •3.1.2. Приоритетный шифратор

- •3.1.3. Разработка схемы дешифратора и его работа

- •3.1.4. Преобразователи кодов

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Демультиплексоры

- •3.2.3. Получение мультиплексоров и демультиплексоров на большое количество входов (выходов)

- •3.2.4. Универсальные логические модули

- •3.2.5. Совместная работа мультиплексора и демультиплексора

- •3.3. Сумматоры, алу и матричные умножители

- •3.3.1. Одноразрядный сумматор

- •3.3.2. Сумматор последовательного действия

- •3.3.3. Сумматор параллельного действия с последовательным переносом

- •3.3.4. Сумматор параллельного действия с параллельным переносом

- •3.3.5 Арифметико-логические устройства

- •3.3.6. Матричные умножители

- •3.4. Компараторы

- •3.5 Схемы контроля

- •3.6. Вопросы и задания для самоконтроля

- •4. Узлы последовательностного типа

- •4.1. Триггеры

- •4.1.1. Асинхронные триггеры

- •4.1.2. Асинхронный d-триггер

- •4.1.3. Синхронные триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Триггеров

- •4.1.4. Триггеры с двухступенчатым запоминанием информации

- •4.1.6. Счетный триггер

- •4.1.7. Динамические триггеры

- •4.1.8. Установка начального значения триггера

- •4.1.9. Триггеры Шмидта

- •4.2. Регистры

- •4.2.1. Параллельный регистр

- •4.2.2. Последовательные (сдвигающие) регистры

- •4.2.3. Взаимное преобразование числа из последовательного кода в параллельный

- •4.3. Счётчики

- •4.3.1. Суммирующие счетчики

- •4.3.2. Вычитающие счетчики

- •4.3.3. Реверсивные двоичные счетчики

- •4.3.4. Кольцевые счетчики

- •4.3.5. Условное обозначение счетчиков

- •4.3.6. Быстродействие счетчиков

- •4.3.7. Программирование счетчиков

- •4.4. Вопросы и задания для самоконтроля

- •5. Аналого-цифровые и цифро-аналоговые преобразователи

- •5.1. Аналого-цифровые преобразователи

- •5.1.1. Принцип аналого-цифрового преобразования

- •5.1.2. Ацп с промежуточным преобразованием во временной интервал

- •5.1.3. Аналого-цифровой преобразователь с обратной связью

- •5.1.4 Аналого-цифровой преобразователь следящего типа

- •5.1.5. Параллельный ацп

- •5.1.6. Интегрирующие ацп

- •5.1.7. Ацп последовательных приближений

- •5.2. Цифро-аналоговые преобразователи

- •5.3. Преобразователи интервалов времени

- •5.4. Вопросы для самоконтроля

- •6. Устройства хранения информации

- •6.1. Основные характеристики запоминающих устройств

- •6.2. Оперативные запоминающие устройства

- •6.2.1. Статические озу

- •6.2.2. Динамические озу Принцип действия динамических озу

- •Схемные особенности динамических озу

- •6.3. Постоянные запоминающие устройства

- •Масочные пзу

- •Программируемые пзу

- •6.4. Перепрограммируемые запоминающие устройства

- •Флэш-память

- •6.5. Вопросы для самоконтроля

- •7. Селекторы импульсных сигналов

- •7.1. Амплитудные селекторы

- •7.1.1. Селектор максимального уровня

- •7.1.2. Селектор минимального уровня

- •7.2. Временные селекторы

- •7.3 Селекторы импульсов по длительности

- •7.3.1. Селекторы максимальной длительности

- •7.3.2. Селекторы минимальной длительности

- •7.4 Элементы задержки и формирователи импульсов

- •7.5. Вопросы для самоконтроля

- •8. Средства отображения информации

- •8.1. Газоразрядные цифровые индикаторы

- •8.2. Знакосинтезирующие индикаторы

- •8.3. Вакуумные люминесцентные индикаторы

- •8.4. Вакуумные накаливаемые индикаторы

- •8.5. Полупроводниковые семисегментные индикаторы

- •8.6. Жидкокристаллические индикаторы (жки)

- •8.7. Матричные индикаторы

- •8.8. Подключение индикаторов к эвм

- •8.9. Вопросы и задания для самоконтроля

- •9. Автоматы

- •9.1. Автомат в системе управления

- •9.2. Структурный автомат

- •9.3. Аппаратная реализация автоматов

- •9.4. Вопросы и задания для самоконтроля

- •Заключение

- •Б иблиографический список

- •ПриложенИя

- •Приложение 1. Обозначения цифровых микросхем

- •Приложение 2. Условные графические обозначения элементов цифровой техники

- •Оглавление

4.1.2. Асинхронный d-триггер

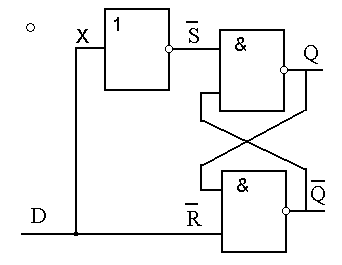

В D-триггере недостаток RS-триггера устраняется. Если в RS-триггере вход S соединить со входом R через инвертор (рис. 4.4,а), то получится D-триггер. Полученный таким образом вход называется входом D. Теперь поданный на него логический сигнал поступает как на вход S (без изменения), так и на вход R (инвертируясь).

Е

а б

Рис.4.4. Асинхронный D-триггер

На входах RS-триггера никогда не появится двух пассивных или двух активных уровней. Асинхронные D-триггера используются редко.

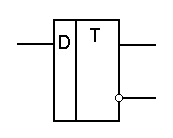

Условное обозначение приведено на рис. 4.5.

Вход |

Входы |

Выходы |

||

D |

S |

R |

Q |

|

1 0 |

1 0 |

0 1 |

1 0 |

0 1 |

абота

асинхронного

абота

асинхронного

D-триггера Таблица 4.4

Рис.4.5.Обозначение

асинхронного D-триггера

4.1.3. Синхронные триггеры

Синхронные триггеры меняют свое состояние (принимают информацию) только тогда, когда подается разрешающий (тактовый) сигнал на специально организованный синхронизирующий вход С. Если на входе С уровень логического нуля, то триггер остается в прежнем состоянии.

Синхронный rs-триггер

Работа синхронного RS-триггера описана таблицей 4.5. При C=0 любые комбинации сигналов на входах S и R не меняют состояния выхода триггера. При С=1 триггер работает как и асинхронный триггер. Состояние сигналов на входах S=R=C=1 недопустимо, что обозначено * (основной недостаток RS-триггеров).

Работа синхронного

RS-триггера Таблица 4.5

Входы |

Выходы |

|||

С |

S |

R |

Q |

|

0 |

0 |

0 |

Q |

|

0 |

1 |

0 |

Q |

|

0 |

0 |

1 |

Q |

|

0 |

1 |

1 |

Q |

|

1 |

0 |

0 |

Q |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

* |

* |

Аналогично и для выхода : либо сохранится предыдущее состояние , либо оно станет равным единице, когда на входах R и C одновременно поданы уровни логической единицы. Система уравнений, описывающая работу рассматриваемого триггера:

(4.4)

(4.4)

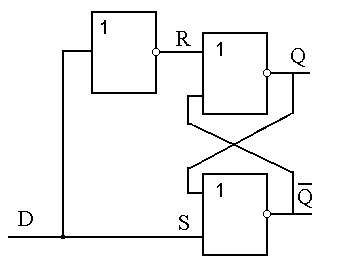

Отличие полученной системы логических выражений от системы (4.1) в том, что информационные входы S и R объединяются с сигналом С. Для объединения сигналов достаточно применить элементы И (для триггера с инверсными входами – И-НЕ, чтобы одновременно инвертировать входной сигнал). На рис. 4.6,а представлен синхронный RS-триггер на элементах ИЛИ-НЕ, на рис. 4.6,б – синхронный RS-триггер на элементах И-НЕ. Поступающие на входы S и R асинхронного RS-триггера сигналы образуются перемножением сигналов со входов S или R и входа C. Когда на входе С уровень нуля (пассивный сигнал), на входы асинхронного триггера проходят также пассивные сигналы и он не работает (не меняет своего состояния). Активный сигнал на входе С открывает элементы И (И-НЕ), и на входы асинхронного триггера поступают уровни сигналов, меняющие его состояние в соответствии с таблицей работы асинхронного RS-триггера.

а б

Рис.4.6. Синхронный RS-триггер

Пунктирной линией на рис. 4.6 обозначен асинхронный RS-триггер, поэтому синхронный RS-триггер можно рассматривать как асинхронный, дополненный элементами И (И-НЕ). Можно считать, что на элементах И (И-НЕ) выполнен замок, который открывается для прохождения информационных сигналов на асинхронный триггер при поступлении на вход С уровня единицы.