- •В.В. Болгов, в.И. Енин, а.В. Смольянинов

- •Схемотехника

- •В.В. Болгов, в.И. Енин, а.В. Смольянинов Схемотехника

- •Схемотехника

- •Введение

- •После изучения дисциплины необходимо знать:

- •После изучения дисциплины необходимо уметь:

- •В.1. Роль и место курса “Схемотехника” в учебном процессе

- •В.2. Основные направления развития цифровых устройств

- •В.3. Самостоятельная работа студентов и контроль знаний

- •1 . Основы теории логических функций.

- •1.1. Логические функции

- •1.2. Основные законы и тождества алгебры логики

- •1.3. Формы представления логических функций

- •Совершенная дизъюнктивная нормальная форма

- •Совершенная конъюнктивная нормальная форма

- •Получение логических выражений скнф и сднф

- •1.4. Минимизация логических функций

- •Метод Квайна

- •Метод карт Вейча

- •1.5. Построение и анализ работы логических схем

- •1.6. Построение логических схем с несколькими выходами

- •1.7. Вопросы и задания для самоконтроля

- •2. Интегральные микросхемы

- •2.1. Технологии цифровых интегральных схем

- •2.2. Параметры интегральных микросхем

- •2.3. Логические элементы транзисторно-транзисторной логики

- •2.3.1. Входные каскады ттл микросхем

- •2.3.2. Типы выходных каскадов ттл цифровых элементов

- •Логический выход

- •Элементы с тремя состояниями

- •Выходные каскады с открытым эмиттером

- •Выход с открытым коллектором

- •Основные характеристики микросхем ттл серий

- •2.4. Логические элементы эмиттерно-связанной логики

- •2.5. Логические элементы на моп‑транзисторах

- •2.6. Кмоп микросхемы

- •2.6.1. Режим неиспользуемых входов

- •2.6.2. Преобразователи уровня

- •2.7. Простейшие интегральные микросхемы

- •2.8. Шинные формирователи и приемопередатчики

- •2.9. Вопросы и задания для самоконтроля

- •3. Устройства комбинационного типа

- •Двоичные шифраторы и дешифраторы

- •3.1.1. Разработка схемы шифратора и его работа

- •3.1.2. Приоритетный шифратор

- •3.1.3. Разработка схемы дешифратора и его работа

- •3.1.4. Преобразователи кодов

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Демультиплексоры

- •3.2.3. Получение мультиплексоров и демультиплексоров на большое количество входов (выходов)

- •3.2.4. Универсальные логические модули

- •3.2.5. Совместная работа мультиплексора и демультиплексора

- •3.3. Сумматоры, алу и матричные умножители

- •3.3.1. Одноразрядный сумматор

- •3.3.2. Сумматор последовательного действия

- •3.3.3. Сумматор параллельного действия с последовательным переносом

- •3.3.4. Сумматор параллельного действия с параллельным переносом

- •3.3.5 Арифметико-логические устройства

- •3.3.6. Матричные умножители

- •3.4. Компараторы

- •3.5 Схемы контроля

- •3.6. Вопросы и задания для самоконтроля

- •4. Узлы последовательностного типа

- •4.1. Триггеры

- •4.1.1. Асинхронные триггеры

- •4.1.2. Асинхронный d-триггер

- •4.1.3. Синхронные триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Триггеров

- •4.1.4. Триггеры с двухступенчатым запоминанием информации

- •4.1.6. Счетный триггер

- •4.1.7. Динамические триггеры

- •4.1.8. Установка начального значения триггера

- •4.1.9. Триггеры Шмидта

- •4.2. Регистры

- •4.2.1. Параллельный регистр

- •4.2.2. Последовательные (сдвигающие) регистры

- •4.2.3. Взаимное преобразование числа из последовательного кода в параллельный

- •4.3. Счётчики

- •4.3.1. Суммирующие счетчики

- •4.3.2. Вычитающие счетчики

- •4.3.3. Реверсивные двоичные счетчики

- •4.3.4. Кольцевые счетчики

- •4.3.5. Условное обозначение счетчиков

- •4.3.6. Быстродействие счетчиков

- •4.3.7. Программирование счетчиков

- •4.4. Вопросы и задания для самоконтроля

- •5. Аналого-цифровые и цифро-аналоговые преобразователи

- •5.1. Аналого-цифровые преобразователи

- •5.1.1. Принцип аналого-цифрового преобразования

- •5.1.2. Ацп с промежуточным преобразованием во временной интервал

- •5.1.3. Аналого-цифровой преобразователь с обратной связью

- •5.1.4 Аналого-цифровой преобразователь следящего типа

- •5.1.5. Параллельный ацп

- •5.1.6. Интегрирующие ацп

- •5.1.7. Ацп последовательных приближений

- •5.2. Цифро-аналоговые преобразователи

- •5.3. Преобразователи интервалов времени

- •5.4. Вопросы для самоконтроля

- •6. Устройства хранения информации

- •6.1. Основные характеристики запоминающих устройств

- •6.2. Оперативные запоминающие устройства

- •6.2.1. Статические озу

- •6.2.2. Динамические озу Принцип действия динамических озу

- •Схемные особенности динамических озу

- •6.3. Постоянные запоминающие устройства

- •Масочные пзу

- •Программируемые пзу

- •6.4. Перепрограммируемые запоминающие устройства

- •Флэш-память

- •6.5. Вопросы для самоконтроля

- •7. Селекторы импульсных сигналов

- •7.1. Амплитудные селекторы

- •7.1.1. Селектор максимального уровня

- •7.1.2. Селектор минимального уровня

- •7.2. Временные селекторы

- •7.3 Селекторы импульсов по длительности

- •7.3.1. Селекторы максимальной длительности

- •7.3.2. Селекторы минимальной длительности

- •7.4 Элементы задержки и формирователи импульсов

- •7.5. Вопросы для самоконтроля

- •8. Средства отображения информации

- •8.1. Газоразрядные цифровые индикаторы

- •8.2. Знакосинтезирующие индикаторы

- •8.3. Вакуумные люминесцентные индикаторы

- •8.4. Вакуумные накаливаемые индикаторы

- •8.5. Полупроводниковые семисегментные индикаторы

- •8.6. Жидкокристаллические индикаторы (жки)

- •8.7. Матричные индикаторы

- •8.8. Подключение индикаторов к эвм

- •8.9. Вопросы и задания для самоконтроля

- •9. Автоматы

- •9.1. Автомат в системе управления

- •9.2. Структурный автомат

- •9.3. Аппаратная реализация автоматов

- •9.4. Вопросы и задания для самоконтроля

- •Заключение

- •Б иблиографический список

- •ПриложенИя

- •Приложение 1. Обозначения цифровых микросхем

- •Приложение 2. Условные графические обозначения элементов цифровой техники

- •Оглавление

3.1.3. Разработка схемы дешифратора и его работа

Двоичные дешифраторы относятся к преобразователям кода. На вход дешифратора поступают коды символов, которые преобразуются в значения символов (двоичной код преобразуется в код «один из N»). Дешифратор, имеющий N входов, не может иметь больше 2N выходов. В зависимости от входного двоичного кода на выходе дешифратора возбуждается один и только один выход.

В качестве примера рассмотрим построение дешифратора двоичного кода (8421) цифр в десятичные цифры, каждая из которых имеет свой выход (задача, обратная рассмотренной при изучении шифратора).

У дешифратора на входы поступают коды символов, которые преобразуются (декодируются) в символы, вызывающие появление активного уровня сигнала только на одном выходе. Его работа описывается той же, что и работа шифратора, таблицей 3.1, в которой меняются местами входные и выходные переменные: входными переменными будут коды десятичных цифр - значения X1, X2, X4, X8, а выходными – выходы самих десятичных цифр Y0 – Y9.

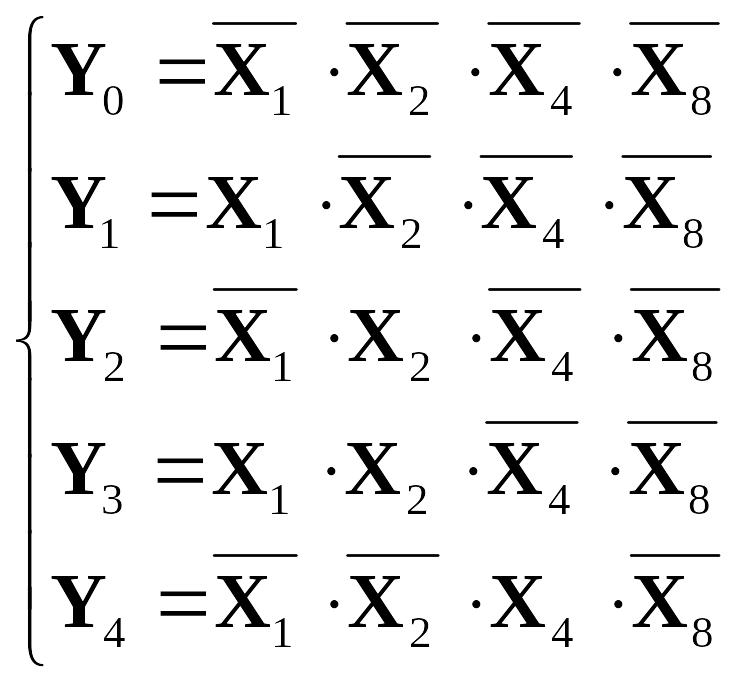

Построение дешифратора также начинается с записи описывающих его работу логических выражений. Так как на каждом выходе активный уровень (единица по таблице 3.1) появляется только при строго определенной комбинации входных переменных, то следует взять конъюнкцию входных переменных, а те из переменных, которые в коде цифры принимают значение нуля, проинвертировать, чтобы конъюнкция оказалась равна единице:

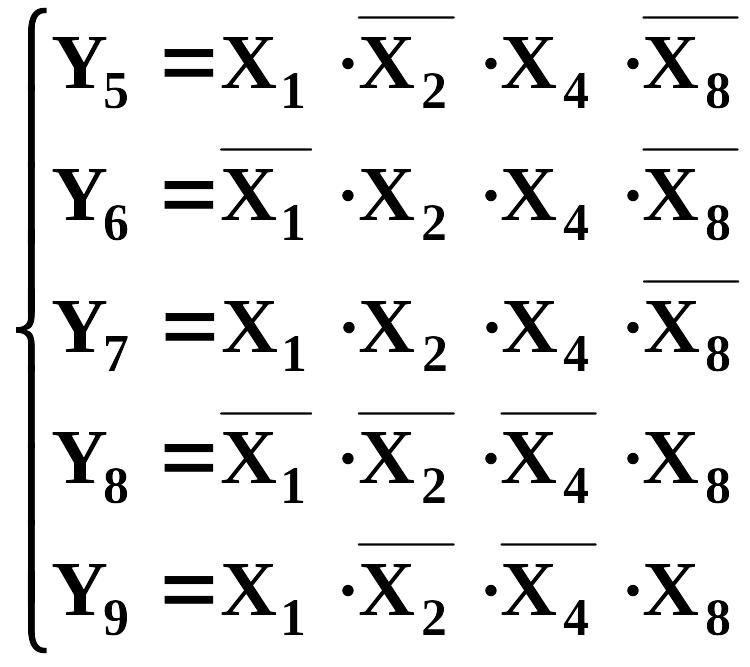

Для построения схемы рассматриваемого дешифратора необходимо взять 10 элементов И на 4 входа каждый и соединить их в соответствии с выше приведенной системой уравнений (рис. 3.4).

Рис 3.4. Схема дешифратора

Теперь, если подать на входы какой-либо код в соответствии с таблицей 3.1, получим уровень единицы только на одном выходе (код символа которого задан входными переменными), на остальных же выходах будут уровни логического нуля.

Построение схем шифратора и дешифратора состоит из одинаковых этапов (составление таблицы работы, которая у них совпадает, составление по таблице системы логических выражений, в которой входные переменные для шифратора являются выходными для дешифратора и наоборот, приведение системы логических выражений к требуемому базису и построение схемы в соответствии с полученной системой). Необходимо обратить внимание на то, что при описании работы шифратора используют логические суммы (дизъюнкции) входных переменных, тогда как у дешифратора – логические произведения (конъюнкции).

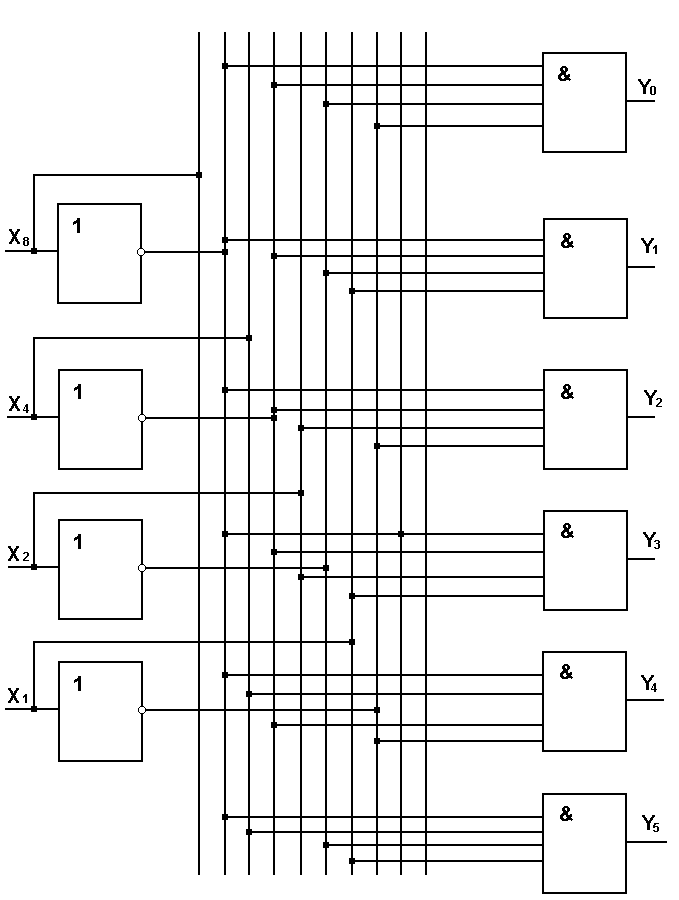

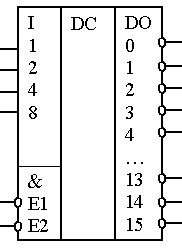

Промышленностью выпускаются микросхемы дешифраторов на ограниченное число входов и выходов (обычно на четыре входа). Обычно они имеют инвертированные выходы (формируют инверсию выходных сигналов) и один или несколько управляющих входов. При запрещении работы микросхемы на выходе обычно устанавливается высокий уровень. На рис. 3.5 в качестве примера приведена ИМС дешифратора К155ИД3, работа которого описывается таблицей 3.3. Входы для подачи кодов сигналов обозначены 1, 2, 4, 8, соответствующие кодам выходы обозначены числами 1-15. Входы Е1 и Е2 служат для разрешения работы дешифратора. Причем его работа разрешена только в том случае, когда на оба разрешающих входа поданы уровни логического нуля.

Работа дешифратора К155ИД3 Таблица 3.3

-

Входы

Выходы

Е1

Е2

1

2

4

8

0

1

2

3

4

…

15

1

*

*

*

*

*

1

1

1

1

1

…

1

*

1

*

*

*

*

1

1

1

1

1

…

1

0

0

0

0

0

0

0

1

1

1

1

…

1

0

0

1

0

0

0

1

0

1

1

1

…

1

0

0

0

1

0

0

1

1

0

1

1

…

1

0

0

1

1

0

0

1

1

1

0

1

…

1

.

.

.

.

.

.

.

.

.

.

.

…

.

0

0

1

1

1

1

1

1

1

1

1

…

0

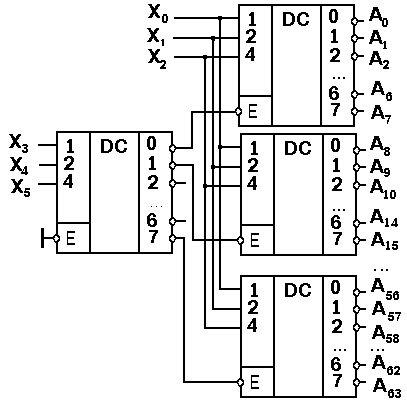

На базе выпускаемых микросхем дешифраторов можно реализовать дешифратор на любое число разрядов. Для расширения числа входов и выходов дешифраторы объединяют в несколько ступеней, причем входы дешифраторов второй ступени подключаются к выходам дешифраторов первой ступени и так далее (рис. 3.6). Дешифратор старших разрядов (входы Х3-Х5) определяет, какой из дешифраторов младших разрядов (Х0-Х2) входного кода будет работать. Младшие разряды кодов поступают на все входы младших дешифраторов параллельно.

Рис. 3.5 Дешифратор К155ИД3 Рис.3.6 Расширение входов

и выходов дешифраторов