Учебное пособие 1900

.pdfваемых данных: булевый (1 бит), байтовый (8 бит), целый (16 бит) и вещественный (32 бита), всего 256 портов каждого типа, для каждого из которых имеются команды записи и чтения. Предусмотренная функция опроса состояния порта позволяет просканировать подключенное устройство и определить его доступную функциональность. Данная организация программ и методов их взаимодействия позволяют: минимизировать зависимость от конкретного микроконтроллера (система может быть перенесена на другую элементную базу с минимальными изменениями); обеспечить прямую и обратную совместимость связки «устройство–ПК».

Вся система разделена на мало зависимые части, можно выделить следующие функциональные блоки системы: блок точной подстройки устройства; блок регуляции и управления технологическим процессом; блок накопления данных; блок предварительной обработки данных; блок анализа и генерации математической модели, блок визуализации полученных результатов. Некоторые блоки требуют прямой связи с устройством, и в тоже время допускается их одновременная работа, что приводит к необходимости объединения части их функциональности в виде отдельного модуля для разрешения проблемы одновременного синхронного доступа к функциям устройства. Допускается существование нескольких модулей с различными методиками генерации математической модели. На данный момент реализован модуль анализа, основанный на применении нейронных сетей. Математическая модель представляется в виде «черного ящика», внутренности которого реализует настроенная специальным образом нейронная сеть. Данный подход позволяет представлять модели любых размерностей без специальных изменений в логике работы программы. Так же возможно добавление заранее известных математических зависимостей (например передаточные функции исполнительных механизмов, датчиков), что увеличивает точность итоговой модели и уменьшает долю «приближенных» данных.

Предложенная архитектура построения информационной системы для анализа технологических процессов является достаточно гибкой с возможностью произвольной замены отдельных компонентов и с большими возможностями для расширения. В частности расширения доступных методик построения модели, модулей конфигурирования системы, анализа данных и визуализации полученных результатов.

51

Литература

1.Тютин М.В., Барабанов В.Ф., Черных В.Я. Аппаратнопрограммный комплекс для автоматизированного анализа технологических процессов // Вестник ВГТУ, том 3, №5, 2007 г., с. 60-65

2.James A. Freeman, David M. Skapura. Neural networks : algorithms, applications, and programming techniques // 1991 г., с. 103-106

3.Дейл Роджерсон; Основы COM. // 1998.

УДК 004.451.2

КОМПЬЮТЕРНОЕ ПРОЕКТИРОВАНИЕ ТЕХНОЛОГИЙ НА ОСНОВЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОГО КОДИРОВАНИЯ

Лосев А.А.

Воронежский государственный технический университет

E-mail: losev.vrn@mail.ru

Актуальность компьютерного проектирования технологических процессов обусловливается высокой техническоэкономической эффективностью автоматизированного проектирования; повышением вычислительных возможностей современной компьютерной техники; возможностью сокращения сроков проектирования и опытной отработки технологий.

Существуют несколько вариантов реализации данного метода. Первый из них предполагает использование БД технологий на конкретные детали – на каждую деталь есть технология и она хранится под кодом. В этом случае проектирование будет сводиться к поиску наиболее точно подходящей детали для рабочей детали и дальнейшей ручной корректировке ТП найденной детали, если таковая потребуется. В этом варианте достигается наибольшая скорость и точность проектирования, но для его реализации потребуется создать БД колоссального размера.

Второй вариант в качестве своей основы использует БД УТП и его использование возможно лишь в условиях, когда на предприятии имеется развитая групповая технология. Также САПР, реализующая проектирование ТП этим методом должна иметь обширную базу данных (БД) унифицированных ТП, но эта БД будет значительно меньше, чем в первом варианте. Для адресации к этой БД должна быть продумана система кодирования и поисковая система,

52

электронный документооборот.

Процедуру проектирования можно разбить на 3 этапа:

1-й этап проектирования предназначен для поиска (адресации) КД на основе конструкторского кода. На данном этапе определяется конструкторско-технологический код детали – он будет являться ключом поиска КД.

2-й этап проектирования предназначен для выборки из базы данных модели УТП для найденной КД.

3-й этап проектирования предназначен для настройки УТП на обработку заданной детали. На этом этапе модель УТП преобразуется в модель рабочего ТП, по которому будет обработана заданная деталь.

Настройка УТП может быть 2-х типов: структурная и параметрическая. На первом этапе определяется ключ поиска – конструк- торско-технологический код – с его помощью запускается процесс поиска по общим характеристикам. Результатом адресации на первом этапе является множество МКД номеров комплексных деталей (НКД), к которым адресовалась заданная i - я деталь: МКД = {НКДm}; m = 1,mk , где mk - количество найденных комплексных деталей. На втором этапе анализируются найденные КД в следующем порядке. Из множества МКД последовательно отбираются номера КД. Для них из базы данных выбираются эскизы КД и просматриваются на экране дисплея. Технолог определяет, какая КД в наибольшей степени подходит для заданной детали. Номер комплексной детали запоминается.

На следующем шаге происходит выборка из БД модели унифицированного технологического процесса для найденной комплексной детали. В модели КД обычно фиксируется идентификатор того УТП, с помощью которого можно обработать данную деталь. По этому номеру выполняется обращение к базе данных и параметрическая модель УТП записывается в оперативную базу данных. Модель, хранимая в оперативной базе, условно считается параметрической моделью рабочего технологического процесса, так как еще не подвергнута настройке на обработку заданной детали. На заключительном этапе проектирования, происходит преобразование УТП в модель рабочего технологического процесса, по которому будет обработана заданная деталь. Получение параметрической модели рабочего ТП для детали выполняется путем параметрической настройки. Так как структура проектируется на уровне

53

процесса, то параметрическая настройка заключается в интеллектуальном удалении операций, которые не нужны для обработки заданной детали.

Третий вариант реализации предполагает наличие БД КТЭ, соответствующих им операций, а также классификатора, в котором КТЭ объединяются в группы в соответствие с кодом ЕСКД. Здесь предпринимается попытка автоматической сборки РП из операций (переходов) обработки отдельных КТЭ.

УДК 004.046

ПРОГРАММА ГЕНЕРАЦИИ КОНТРОЛИРУЮЩИХ ТЕСТОВ ДЛЯ ДИСКРЕТНЫХ УСТРОЙСТВ

Белозоров С.А.

Воронежский государственный технический университет

E-mail: skimin0k@bk.ru

В связи с постоянным ростом сложности и функциональности цифровых устройств, все более острой становится проблема их контроля и диагностирования. При этом процесс составления контролирующих тестов составляет до 50% общей трудоемкости изготовления электронных изделий. И в тоже время это сказывается и на их стоимости.

Таким образом, повышение качества изготавливаемых изделий при снижении трудоемкости контроля и их стоимости является одной из главных задач производства средств вычислительной техники. Данный факт и определяет актуальность работы.

Целью работы является разработка алгоритмического обеспечения задач автоматизированного синтеза контролирующих тестов на основе ассоциативных эволюционных алгоритмов для внутрисхемного контроля цифровых узлов. При этом должен быть получен базовый тестовый набор, гарантирующий низкую вероятность наличия неисправностей в схеме, и группы локализующих тестов, стремящихся по результатам базового теста указать предположительное местоположение неисправности. При этом каждая группа локализующих тестов отвечает только за часть ошибок, обнаруженных базовым тестом.

Исходя из цели работы будут решаться следующие задачи: моделирование цифровых схем с неисправностями;

54

моделирование процессов синтеза тестов для внутрисхемного контроля цифровых узлов;

выбор критерия оценки качества тестовых наборов; выбор наиболее подходящего эволюционного алгоритма;

разработка алгоритмического обеспечения синтеза тестов для цифровых узлов, обеспечивающего требуемые показатели эффективности (полнота контроля, длина теста);

экспериментальное исследование разработанных моделей и алгоритмов.

На данный момент было проведено исследование существующих методов синтеза тестов и было выявлено, что только малая часть из них производит внутреннее тестирование интегральных схем. Большинство тестов направлено только на выявление ошибок монтажа схемы на печатную плату.

Планируемые этапы работы (на 2 года):

Разработка системы моделирования неисправных цифровых схем, описанных на вентильном уровне. Данная система моделирования позволит производить эксперименты над тестовыми последовательностями, проверку гипотез, поиск критериев оценки тестовых последовательностей.

Составление наиболее эффективных критериев оценки тестовых последовательностей.

Разработка алгоритма синтеза тестовых последовательностей для комбинационных схем. Данный этап обеспечивает получение первых экспериментальных результатов.

Разработка алгоритма синтеза тестовых последовательностей на основе эволюционных алгоритмов для блока с памятью. Данный этап позволит достичь экспериментальных результатов для синтеза строгой последовательности тестов в наборе.

Разработка алгоритма разбиения цифровой схемы на комбинационные блоки и блоки с памятью и последующего объединения тестовых последовательностей для этих блоков в общий тест для всего устройства. На данном этапе важно отделить как можно большие комбинационные блоки от блоков с памятью и предусмотреть последующее объединение тестов для них, что позволит несколько ускорить процедуру синтеза тестов с минимальным проигрышем в длине тестового набора.

Доработка систем моделирования неисправных цифровых схем и синтеза тестовых последовательностей для работы с VHDL-

55

описанием устройства.

В результате будет создан программный продукт, который по заданному VHDL описанию будет синтезировать тестовые последовательности для заданного устройства с целью их дальнейшей подачи на устройство с использованием механизма периферийного сканирования.

УДК 004.051

РАЗРАБОТКА ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ ОПЕРАТИВНОГО ОБНАРУЖЕНИЯ «БЛУЖДАНИЙ» ЭВМ

Рожков М.В.

Воронежский государственный технический университет

E-mail: ferux@mail.ru

При использовании микроЭВМ в системе, работающей в реальном масштабе времени, не исключена возможность того, что в результате сбоя или отказа она начнѐт беспорядочное «блуждание» по памяти, рассматривая числовые массивы как цепочки команд, команды – как данные или адреса и т.д. Поскольку неправильное функционирование недопустимо для многих объектов, возникает задача быстрого обнаружения таких «срывов».

На текущий момент начато исследование возможных ошибок, приводящих к блужданиям. Выделен класс ошибок, возникающих в командах управления последовательностью выполнения операций (команды перехода, вызова процедур и программных прерываний и выхода из них, команды организации циклов).

По результатам моделирования последствий ошибок из данного класса видна неэффективность способа, предложенного в существующем патенте. В нѐм предполагается заполнять свободные области после программы массивами машинных кодов одних и тех же команд, например, «Сброс» или «Безусловный переход к команде с адресом А», что позволит обнаружить факт наличия случайного блуждания процессора и автоматически вернуть его к началу рабочей программы или некоторой заданной точке А программы

Неэффективность заключается в том, что программный счѐтчик (PC) после ошибок из данного класса изменяет своѐ значение не сильно, и тем самым остаѐтся в блоке программы, таким обра-

56

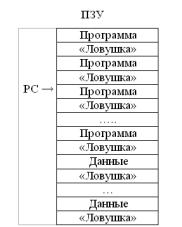

зом пройдѐт немало машинных тактов, пока процессор доберѐтся до области с командами-ловушками, что недопустимо в некоторых системах. Поскольку моделирование проводилось на 32х разрядном процессоре MicroBlaze его результаты можно распространить только близкие к нему процессоры. Такое поведение процессора связано с тем, что при прямой адресации процессор может изменить значение PC на ± 215 = ±32Кб, т.е. не очень большое значение по сравнению с размером памяти существующих модулей. По этой причине предлагается располагать блоки ловушки не после программы, а внутри еѐ (рисунок). Это должно повысить оперативность обнаружения «блужданий».

УДК 004.922

РАЗРАБОТКА УНИВЕРСАЛЬНОЙ СИСТЕМЫ 3D ВОССТАНОВЛЕНИЯ И ВИЗУАЛИЗАЦИИ В РАМКАХ PLMСИСТЕМЫ

Сафронов В.В., Барабанов В.Ф.

Воронежский государственный технический университет

E-mail: safronov.vitaliy@mail.ru

Важным этапом проектирования печатных плат является подготовка уже разработанного проекта к производству. Под этим подразумевается генерация управляющих файлов: для изготовления фотошаблонов; станков сверления отверстий; оборудования

57

автоматического тестирования плат и оборудования автоматической расстановки компонентов.

Несмотря на то, что в настоящее время пользователям доступно огромное количество систем автоматизированного проектирования в области электроники, данные системы позволяют получать лишь схематическое изображение, чего зачастую бывает недостаточно для пространственного представления изделия и его последующего интегрирования в другие системы.

САПР пакеты, наиболее распространѐнные в настоящее время в России не позволяют вести полноценную технич е- скую документацию по разрабатываемому проекту. В связи с этим реализуемая программная система предусматривает полноценную возможность сопряжения с PLM пакетом. Product Lifecycle Management (PLM) (жизненный цикл изделия) —

технология управления жизненным циклом изделий. Организаци- онно-техническая система, обеспечивающая управление всей информацией об изделии и связанных с ним процессах на протяжении всего его жизненного цикла, начиная с проектирования и производства до снятия с эксплуатации.

Целю разрабатываемой программной системы, является: дополнение ECAD данных для восстановления 3D модели печатной платы в системе PLM; создание универсальной справочной системы 3D восстановления и визуализации рамках PLM систем; специализированная конвертация данных, позволяющая осуществлять взаимодействие с базами систем проектирования и PLM систем.

Основные задачи построения системы 3D визуализации: Обмен данными между ECAD системами и пакетом NX; Осуществление передачи информации об элементах для 3D

восстановления и визуализации ПП; Редактирование элементов и их параметров; Взаимодействие с PLM системой;

Расширение интегрированных библиотек в части 3D изображения, а также добавления габаритных размеров элемента;

Создание таблиц соответствия: данных САПР пакета и данных PLM системы.

На данный момент:

1. Разработан справочный модуль системы:

58

Рис.1. Интерфейс справочного модуля системы 3D восстановления и визуализации

2. Разработан шаблон передачи данных из САПР пакетов для визуализации в PLM систему:

.

Рис.2. Результат визуализации слева без применения шаблона, справа с применением шаблона

Литература

1.Гончаров П.С., Ельцов М.Ю., Коршиков С.Б., Лаптев И.В., Осиюк В.А. NX для конструктора-машиностроителя.. — ИД ДМК Пресс. Москва, 2010. — 504 с.

2.http://www.plm.automation.siemens.com

УДК 004.415.2.041

МЕТОДЫ ОБРАБОТКИ СИГНАЛОВ С ПОМЕХАМИ

Азарова Е.С.

Воронежский институт высоких технологий

E-mail: AzarovaEkater@yandex.ru

Вейвлеты представляют собой особые функции в виде коротких волн (всплесков) с нулевым интегральным значением и с локализацией по оси независимой переменной (t или x), способных к сдвигу по этой оси и масштабированию (растяжению/сжатию). Любой из наиболее часто используемых типов вейвлетов порождает полную ортогональную систему. В случае вейвлет-анализа (декомпозиции) процесса (сигнала) благодаря изменению масштаба вейвлеты спо-

59

собны выявить различие в характеристиках процесса па различных шкалах, а посредством сдвига можно проанализировать свойства процесса в различных точках на всем исследуемом интервале. Именно благодаря свойству полноты этой системы можно осуществить восстановление (реконструкцию или синтез) процесса посредством обратного вейвлет-преобразования (ВП). Некоторыми специалистами сжатие данных с помощью wavelet преобразования рассматривается как будущее Internet и телевизионной графики с высоким разрешением, т.к. этот метод обладает способностью более чистого сжатия сигналов, чем другие.

Непрерывное (интегральное) вейвлет-преобразование (НВП или CWT – continuous wavelet transform).

Непрерывное ВП нашло широкое применение в обработке сигналов. В частности вейвлет-анализ (ВА) дает уникальные возможности в распознавании локальных и «тонких» особенностей сигналов (функций), что важно во многих областях радиотехники, связи, радиоэлектроники, геофизики и других областях науки и техники.

Классическое преобразование Фурье (ПФ) является традиционным математическим аппаратом для анализа стационарных процессов. При этом сигналы разлагаются в базисе косинусов и синусов или комплексных экспонент. Эти базисные функции простираются вдоль всей оси времени.

С практической точки зрения и с позиций точного представления произвольных сигналов ПФ имеет ряд ограничений и недостатков. Обладая хорошей локализацией по частоте, оно не обладает временным разрешением. ПФ даже для одной заданной частоты требует знания сигнала не только в прошлом, но и в будущем, а это - теоретическая абстракция. Обусловлено это тем, что базисной функцией при разложении в ряд Фурье является гармоническое колебание, которое математически определено на временном интервале от - до + . ПФ не учитывает, что частота колебания может изменяться во времени. Локальные особенности сигнала (разрывы, ступеньки, пики и т.п.) дают едва заметные составляющие спектра, по которым обнаружить эти особенности, и тем более их место и характер, практически невозможно. В этом случае в котором применяется предварительная операция умножения сигнала S(r) на «окно» w(t-b); при этом окном является локальная во времени невозможно и точное восстановление сигнала из-за появления эффекта Гиббса. Для получения о сигнале высокочастотной информации

60