Синтез цифровых счётчиков импульсов. методические указания к выполнению курсовой работы по дисциплине «Цифровые устройства и микропроцессоры». Кондусов В.А., Алперин Е.Д

.pdfТаблица 6

Функционирование и задания сигналов на синхронизирующих входах С

Номер |

Номер |

|

|

|

|

|

|

|

|

|

|

|

|

тактового |

клетки |

|

|

|

|

+1 |

+1 |

+1 |

+1 |

С |

С |

С |

С |

импульса |

карты |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

n |

Карно |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

- |

- |

- |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

- |

- |

1 |

1 |

2 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

- |

- |

- |

1 |

3 |

3 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

- |

1 |

1 |

1 |

4 |

4 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

- |

- |

5 |

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

- |

- |

- |

1 |

6 |

9 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

- |

- |

1 |

1 |

7 |

10 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

- |

- |

- |

1 |

8 |

11 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

- |

1 |

1 |

1 |

9 |

12 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

- |

- |

- |

1 |

10 |

13 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

- |

- |

1 |

1 |

11 |

14 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

- |

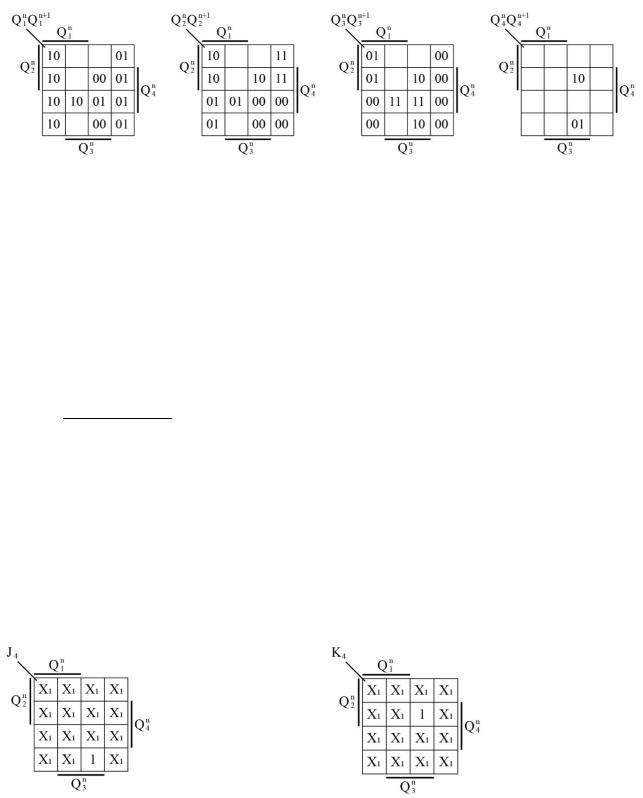

4. Заполняем карты Карно (рис. 9) для каждого разряда по полученной таблице функционирования по правилам, аналогичным как при синтезе синхронных счетчиков. Отмечаем крестиком (или оставляем пустыми) ячейки, где триггер совершает переход 0→0 или 1→1 без разрешающего сигнала на входе. В диаграмме останутся лишь те номера клеток (4 и 14), в ячейках синхронизирующего входа которых есть единица (комбинации разрядов, в которых триггер меняет своё состояние в связи с подачей синхронизирующего сигнала С4 с выхода Q3, т. е. 4→ 3). Т. е. оставляем пустыми (или ставим Х) на номера клеток исключаемых комбинаций согласно таблице функционирования счётчика: 5, 6, 7, 15 и номера клеток, комбинации которых не изменяются в связи с отсутствием в этот момент синхронизирующего сигнала, т. е. все остальные: 0, 1, 2, 3, 8, 9, 10, 11, 12, 13.

В диаграммах , , остаются пустыми только номера клеток исключаемых комбинаций: 5, 6, 7, 15, а номера клеток, где триггеры совершают переход 0→0 или 1→1, не

20

помечаются крестиком (Х), так как эти переходы совершаются при наличии синхросигнала, поступающего от Тс .

Рис. 9. Карты Карно для разрядов счётчика

Замечаем, что диаграммы для первого, второго, третьего разрядов не изменились по сравнению с синтезом синхронного счетчика (синхронизирующий сигнал для 1, 2 и 3-го триггеров является таким же Тс, как и в синхронном счётчике, т. е. Тс →С1 = С2 = = С3), поэтому воспользуемся ранее полученными в п. 1 уравнениями входов:

|

|

|

; |

|

|

|

|

; |

||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

; |

. |

||||||||

|

|

|

||||||||

5. Заполняем карты Карно (рис. 10) для уравнений входов четвертого триггера и считываем с карт Карно уравнения входов в минимизированном виде: J4 = 1, K4 = 1.

J4 = 1 |

K4 = 1 |

Рис. 10. Карты Карно и уравнения входов для четвертого триггера

21

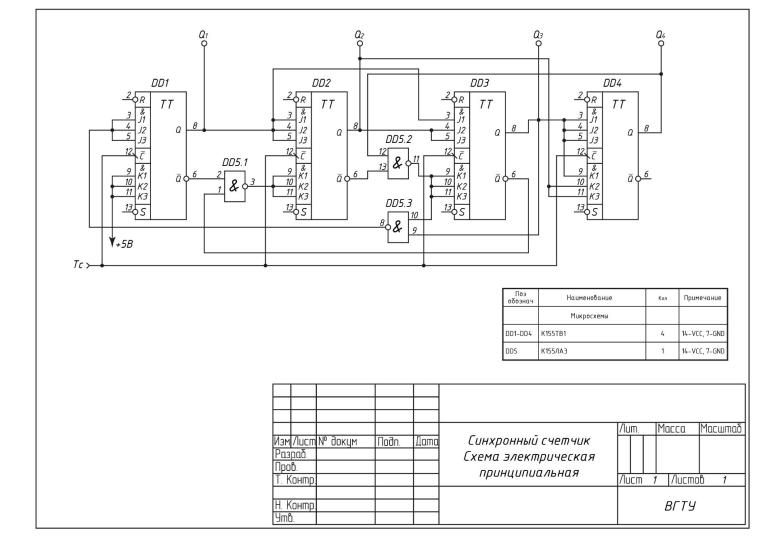

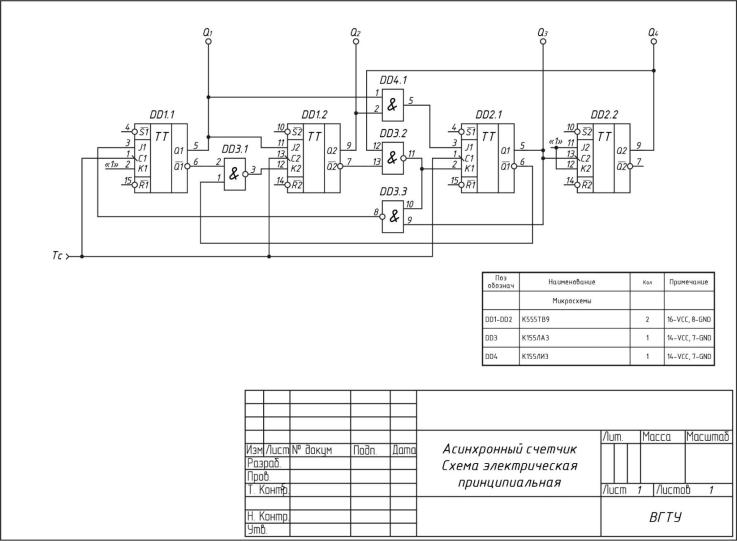

На основании уравнений входов разрабатываем схему асинхронного счетчика. Схема приведена в прил. 4.

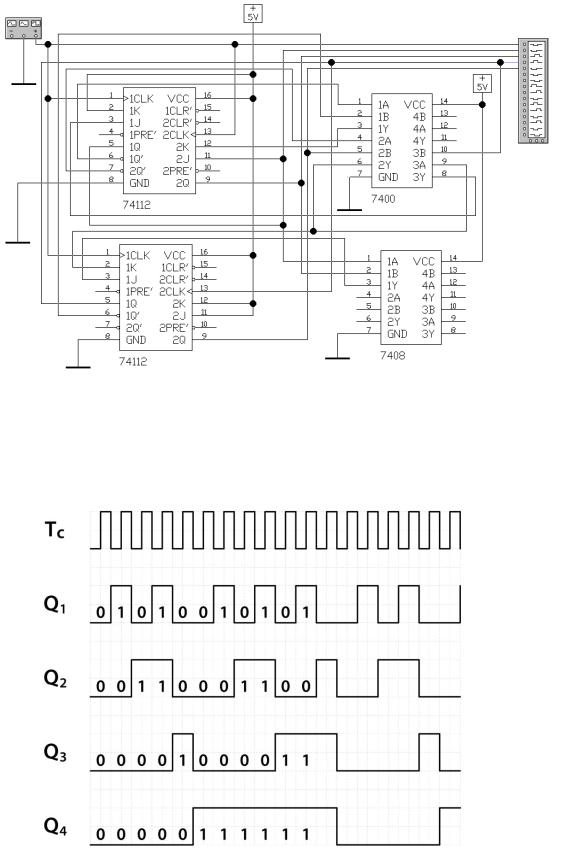

6. Проведём моделирование асинхронного счетчика в программе EWB 5.12 согласно разработанной электрической принципиальной схеме, представленной в прил. 4. При разработке схемы учтем свойства счетчика ввиду того, что микросхема К555ТВ9 имеет два JK-триггера, но по одному входу J и K. Вместо отечественных микросхем JK-триггеров К555ТВ9 применим зарубежные аналоги этой микросхемы SN74112, вместо микросхемы К155ЛА3 – её аналог SN7400, а вместо микросхемы К155ЛИ3 – её аналог SN7408. Четыре разряда обеспечат 2 микросхемы JK-триггера SN74112, функцию И-НЕ выполнит микросхема 7400, функцию И – микросхема 7408.

Микросхемы К555ТВ9 и их аналоги SN74112 представляют собой JK-триггеры с внутренней задержкой и динамическим управлением. Вход синхронизации CLK у всех триггеров инверсный динамический, поэтому данные триггеры тактируются отрицательным перепадом импульса CLK.

Схема модели асинхронного счётчика представлена на рис. 11. Временные диаграммы на выходах триггеров, полученные

с помощью модели логического анализатора, представлены на рис. 12.

Триггеры переключаются по заднему фронту тактового сигнала. На диаграммах отсутствуют исключаемые кодовые комбинации и все числа счета получены в соответствии с таблицей истинности в техническом задании (табл. 1).

Разрешающая способность Тсч и быстродействие счетчика, определяемое временем установления кода Туст асинхронного счётчика, определяются так же, как и для синхронного счётчика.

22

Рис. 11. Схема модели асинхронного счетчика на компонентах программы EWB 5.12

Рис. 12. Временные диаграммы с выходов триггеров асинхронного счётчика на лицевой панели логического анализатора

23

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1.Александров К. К. Электротехнические чертежи и схемы [Текст] / К. К. Александров, Е. Г. Кузьмин. – М.: Энергоатомиздат,

1999. – 288 с.

2.Бойт К. Цифровая электроника [Текст] / К. Бойт. – М.: Техносфера, 2007. – 472 с.

3.Новожилов О. П. Основы цифровой техники: учеб. пособие [Текст] / О. П. Новожилов. – М.: РадиоСофт, 2004. – 528 с.

4.Пухальский Г. И. Цифровые устройства: учеб. пособие для втузов [Текст] / Г. И. Пухальский, Т. Я. Новосельцева. – СПб.: Политехника, 1996. – 885 с.

5.Угрюмов Е. П. Цифровая схемотехника: учеб. пособие [Текст] / Е. П. Угрюмов. – СПб.: БХВ-Петербург, 2001. – 528 с.

24

ПРИЛОЖЕНИЕ 1

ТИТУЛЬНЫЙ ЛИСТ

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«Воронежский государственный технический университет»

Кафедра радиотехники

КУРСОВАЯ РАБОТА

по дисциплине «Цифровые устройства и микропроцессоры»

Синтез синхронных и асинхронных счётчиков

Расчетно-пояснительная записка (вариант 20)

Разработал студент гр. РТ-171 |

А. Б. Иванов |

Руководитель |

В. А. Кондусов |

Работа защищена с оценкой _____________________________

«___» _______ 2019 г.

Воронеж 2019

25

ПРИЛОЖЕНИЕ 2

ЗАДАНИЕ НА КУРСОВУЮ РАБОТУ

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«Воронежский государственный технический университет»

Кафедра радиотехники

ЗАДАНИЕ

на курсовую работу студента группы РТ-171 направления 11.03.01 «Радиотехника»

_____________________________________________

Ф.И.О.

1.Тема: «Синтез синхронных и асинхронных счётчиков».

2.Задание 1. Синтезировать суммирующий синхронный счетчик на универсальных JK-триггерах К155ТВ1(7472). Данные для синтеза,

в соответствии с вариантом табл. 3 (вариант 20, код 5-4-2-1, Ксч = 12), приведены в табл. 1.

Номер |

|

|

|

|

тактового |

|

|

|

|

импульса |

|

|

|

|

n |

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

5 |

1 |

0 |

0 |

0 |

6 |

1 |

0 |

0 |

1 |

7 |

1 |

0 |

1 |

0 |

8 |

1 |

0 |

1 |

1 |

9 |

1 |

1 |

0 |

0 |

10 |

1 |

1 |

0 |

1 |

11 |

1 |

1 |

1 |

0 |

|

|

26 |

|

|

3.Изобразить временные диаграммы. Определить разрешающее время счетчика – Тсч и время установления кода – Туст.

4.Задание 2. Синтезировать суммирующий асинхронный счетчик на универсальных JK-триггерах К555ТВ9 (SN74112). Данные для синтеза, в соответствии с вариантом 20, приведены в табл. 1. Изобразить временные диаграммы. Определить разрешающее время счетчика – Тсч и время установления кода – Туст.

5.Структура, объём и оформление курсовой работы.

Пояснительная записка должна содержать: титульный лист; задание на курсовое проектирование; лист «Замечания руководителя»; содержание с указанием номеров страниц; перечень условных обозначений; введение; текст РПЗ; замечания; список используемых источников; приложения (спецификация чертежей, дополнительные сведения и т. п.).

Объём пояснительной записки: 20-25 страниц, включая приложения. Графическая часть:

–схема электрическая принципиальная синхронного счётчика –

1лист (формат А4); перечень элементов (ПЭ);

–схема электрическая принципиальная асинхронного счётчика –

1лист (формат А4); перечень элементов (ПЭ).

Дата выдачи задания: |

«___» ________201 г. |

|

Срок защиты: |

до «___»________ 201 г. |

|

Руководитель работы: |

_________________ |

__.__. ________ |

Задание принял |

________________ |

__.__. ________ |

27

ПРИЛОЖЕНИЕ 3

СХЕМА СИНХРОННОГО СЧЁТЧИКА

28

ПРИЛОЖЕНИЕ 4

СХЕМА АСИНХРОННОГО СЧЁТЧИКА

29

29