Исследование узлов систем управления. лабораторный практикум. Герасимов М.И., Болдырев И.А

.pdf2.19 Соберите на стенде итоговую схему, разработанную в п. 1.5. Проверьте функционирование схемы, запишите её как ИЕ15-1. Сделайте вывод о результатах исследования, запишите его в отчет.

Контрольные вопросы

1.Дайте словесное описание микросхемы К555ТВ9 с элементами классификации.

2.Объясните работу схемы, разработанной при выполнении п. 1.2 предварительного задания, приведите сделанный вами вывод (п. 2.6).

3.Дайте словесное описание микросхемы К555ТМ2 с элементами классификации.

4.Объясните работу схемы, разработанной при выполнении п. 1.3 предварительного задания, приведите сделанный вами вывод (п. 2.11).

5.Дайте словесное описание микросхемы К555ИР8 с элементами классификации.

6.Объясните работу нереверсивной схемы, разработанной при выполнении п. 1.4 предварительного задания, приведите сделанный вами вывод (п. 2.18).

7.Объясните работу узла реверса, разработанного при выполнении п. 1.4 предварительного задания, приведите сделанный вами вывод (п. 2.18).

8.Дайте словесное описание микросхемы К555ИЕ15 с элементами классификации.

9.Объясните работу каждого узла схемы, разработанной при выполнении п. 2.1.5 предварительного задания.

10.Дайте описание функционирования разработанного вами КК на базе счетчика.

11.Проведите сравнение всех опробованных вами вариантов КК.

12.Функциональное назначение многофазных генераторов

икольцевых коммутаторов.

13.Варианты элементной базы кольцевых коммутаторов.

21

14.Особенности КК при числе фаз М ≠ 2к.

15.Назначение логических элементов в КК на триггерах и регистрах.

16.Описание функционирования схемы на рис. 1.3.

17.Описание функционирования схемы на рис. 1.3.

18.Структура КК на основе триггеров, описание работы собранных схем, выводы.

19.Структура нереверсивного КК на основе регистра, описание работы собранных схем, выводы.

20.Структура реверсивного КК на основе регистра, описание работы собранных схем, выводы.

21.Структура КК на основе счетчиков, описание работы собранных схем, выводы.

22

ЛАБОРАТОРНАЯ РАБОТА №2 СИНТЕЗ ДЕЛИТЕЛЯ ЧАСТОТЫ

Цель работы:

–изучить принципы построения схем счетчиков и делителей частоты;

–на примере загружаемого реверсивного счетчика получить практические навыки использования многофункциональных микросхем в различных узлах цифровой техники.

Теоретические сведения

Определение счетчиков Счетчики – общее название последовательностных эле-

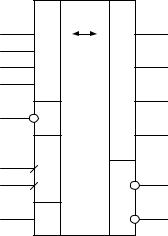

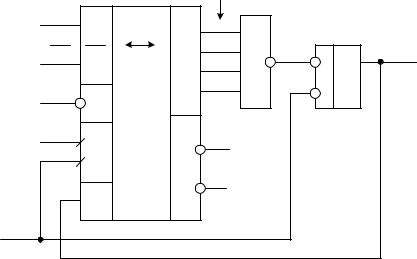

ментов цифровой микросхемотехники, выполняющих несколько логических функций. Основной функцией может быть либо подсчет поступающих на вход импульсов (счетных импульсов) с выдачей текущего результата счета в заданном коде, либо выделение нужного числа импульсов из серии постоянной длины, либо деление частоты входного импульсного сигнала. Счетчики, способные выполнять и подсчет импульсов и деление частоты, можно отнести к полным, а выделяющие заданное число импульсов K из серии N – к специальным. Делители с этой точки зрения представляют собой частный случай специальных счетчиков с выделением одного импульса из N. Дополнительные функции обеспечивают установку счетчика в заданное состояние перед счетом, переход в режим хранения, управление направлением счета и др. Структурно счетчики состоят из нескольких соединенных каскадно схем Т- триггеров. Наиболее характерны два способа построения счетчиков: с последовательным (рис. 2.1, а) и с параллельным переносом (рис. 2.1, б – цепь обнуления R не показана). В счетчике с последовательным переносом триггеры соединены последовательно, так что каждый последующий разряд срабатывает после того, как переключился предыдущий. Результат

23

|

|

|

Q0 |

|

|

Q1 |

|

|

Q2 |

|

|

Q3 |

||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Т |

Т |

|

|

Т |

Т |

|

|

Т |

Т |

|

|

Т |

Т |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а

&

P4

P0 |

E T |

P1 |

E T |

& |

& P3 |

E T |

|

|

E T |

|

|||

|

T |

|

T |

T |

|

T |

С |

Q0 |

|

Q1 |

Q2 |

|

Q3 |

|

|

|

|

|

|

б

Рис. 2.1

снимается в виде двоичного кода с выходов всех разрядов одновременно. Сигнал с выхода старшего разряда может использоваться для подачи на вход счетчика старших разрядов (Q4 =P4). Быстродействие таких счетчиков невелико, что обусловлено последовательным во времени срабатыванием разрядов. Соответственно быстродействие счетчика в n раз меньше быстродействия составляющих его триггеров (n – разрядность счетчика), смена кодов на выходах может сопровождаться последовательностью ложных переходных состояний (например, вместо перехода 01112-10002 получаем 0111-0110-0100-0000- 1000). Микросхемы счетчиков с такой организацией переноса называют асинхронными.

Счетчик с параллельным переносом (синхронный) характеризуется наибольшим быстродействием, поскольку счетные импульсы воздействуют одновременно на все триггеры. Условие переключения определяет логический элемент И, включенный на входе Е каждого разряда счетчика. На выходе этого элемента формируется разрешающий переключение сиг-

24

нал, если все предыдущие разряды имеют состояние лог.1. Таким образом, с поступлением каждого счетного импульса переключаются те триггеры, которым предшествуют разряды с состоянием лог.1 на выходах. При заполнении счетчика единицами формируется сигнал переноса P в старший разряд. Наличие выхода сигнала переноса позволяет объединять между собой четырехразрядные счетчики путем соединения выхода переноса одной микросхемы со счетным входом другой. Быстродействие полученного каскадированного счетчика будет меньше быстродействия составляющих его микросхем. Другим классификационным признаком счетчиков является направление счета. По этому признаку различают счетчики суммирующие (up-counter), вычитающие (down-counter) и реверсивные (up-down-counter). В первых с каждым счетным импульсом результат увеличивается на 1. В вычитающих счетчиках имеет место обратная смена состояний. Реверсивные счетчики могут работать в режимах суммирования и вычитания.

По способу кодирования внутренних состояний полные счетчики делятся на подгруппы: двоичные, двоичнодесятичные (декадные), двенадцатиричные (ИЕ4) счетчики, счетчики Джонсона (выпускаются в сериях КМОП) и др. Наиболее полно представлены в различных сериях микросхем двоичные счетчики. Как правило, микросхемы двоичного счетчика содержат четыре разряда, могут иметь выходы сигналов переноса и, следовательно, допускают непосредственное соединение с другой такой же микросхемой при наращивании разрядности счетчика. Наряду с двоичными широкое распространение получили двоично-десятичные счетчики. В отличие от двоичных они имеют число состояний, равное 10, а не 2n. В схеме такого счетчика четыре триггера, но шесть "лишних" состояний исключены. Во всех счетчиках предусмотрены дополнительные входы обнуления R, а во многих – входы разрешения предварительной установки состояния L. Эти функции обычно используют при реализации делителей. Выпол-

25

няться они могут как асинхронно, так и синхронно (в момент подачи очередного счетного импульса). Функция L обычно имеет приоритет перед функцией счета, а функция R – перед ними обеими, так что одновременная подача нескольких управляющих воздействий ведет к выполнению наиболее приоритетной функции.

Специальные счетчики и делители

Особенность этих устройств состоит в том, что для выходного сигнала они имеют единственный вывод (хотя могут иметь и дополнительные выходы для каскадирования и т.п.). Основной функцией специальных счетчиков является выделение нужного числа импульсов из серии постоянной длины. Среди микросхем семейства ТТЛ в законченном виде выпускается только счетчик К155ИЕ8 (К импульсов из 64). В нем установка двоичного кода количества импульсов производится в режиме загрузки, имеются выходы и входы для каскадирования.

Делители предназначены для деления числа входных импульсов или частоты их следования на заданный коэффициент. Среди микросхем семейства ТТЛ в законченном виде выпускаются счетчики К555ПЦ1 (в 2N раз, где N = 2…31) /6/. В семействе КМОП есть программируемые делители на счетчиках

Джонсона К561ИЕ19 и 564ИЕ19 с Кдел от 3 до 21327. Однако в большинстве случаев делители строят на основе двоичных

счетчиков: полных или специальных. В частности, для получения делителя в 2n раз, где n = 1…5, используют счетчик К155ИЕ8, подавая на входы загрузки двоичный код числа n.

Рассмотрим реализацию делителей на полных счетчиках. Коэффициент деления Кдел может иметь постоянное или переменное, т.е. программируемое, значение. Делители с переменным Кдел управляются от внешних устройств, задающих коэффициент деления, а делителям с постоянным коэффициентам он задается путем соответствующей коммутации входов и выходов. Делители на полных счетчиках могут быть построены

26

по различным схемотехническим вариантам, например, с предварительной установкой исходного состояния, от которого счет ведется (вверх или вниз) до переполнения счетчика, либо с установкой заданного конечного состояния, до которого, начиная с нулевого, ведется счет входных импульсов, после чего результат сбрасывается и начинается новый счетный цикл. Последняя схема может использоваться не только в делителях, но и в узлах счета импульсов по основанию Кдел, тогда как счетчик с предустановкой исходного состояния выдает в ходе счета коды, не соответствующие количеству поступивших импульсов, а, следовательно, для счета использоваться не может. В счетчиках с предустановкой исходного состояния результирующий сигнал снимается с выхода переполнения, а в счетчиках со сбросом – с выхода дешифратора (компаратора) состояний – дополнительной схемы, выявляющей граничное состояние счетчика. Некоторые микросхемы счетчиков имеют для выполнения функции начальной установки встроенные элементы И (например, К555ИЕ5), что позволяет строить делители со сбросом без дополнительных элементов только с помощью обратных связей. Делители с переменным Кдел и установкой заданного конечного состояния включают в себя, помимо счетчика, компаратор кодов, на входы которого подают выходной код счетчика и опорный код А= Кдел, а выход подключают к R-входу счетчика. При достижении счетчиком состояния, код которого равен опорному, компаратор выдает сигнал, возвращающий счетчик в нулевое состояние. Следует отметить, что пребывание счетчика в заданном состоянии оказывается кратковременным (на временной диаграмме виден только так называемый "клык"), так что счетчик последовательно проходит состояния от 0 до Кдел–1 (всего Кдел состояний). Если схема используется в качестве счетчика импульсов по основанию Кдел, наличие "клыков" может быть недопустимым и в схему потребуется вводить дополнительные элемен-

27

ты. Рассмотрим функционирование счетчика К555ИЕ7 и раз- |

|||||

личные схемы делителей, выполненные на его основе. |

|||||

|

|

|

|

Микросхема ИЕ7 |

|

|

Микросхема представляет собой загружаемый синхрон- |

||||

ный четырехразрядный двоичный реверсивный счетчик с |

|||||

асинхронной установкой в 0. Его условное обозначение изо- |

|||||

бражено на рис. 2.2, функциональная схема и временнáя диа- |

|||||

грамма функционирования приведены в справочниках. Струк- |

|||||

турно счетчик состоит из четырех соединенных каскадно схем |

|||||

тактируемых RS-триггеров с комбинационной логикой на вхо- |

|||||

дах. Эта логика обеспечивает замыкание обратных связей, пе- |

|||||

реводящее триггеры в счетный режим, параллельный перенос |

|||||

между разрядами, загрузку произвольного кода и установку |

|||||

триггеров в "0". При этом реализуется приоритет функции за- |

|||||

грузки перед функцией счета, а функции начальной установки |

|||||

– перед ними обеими, так что одновременная подача несколь- |

|||||

ких управляющих воздействий ведет к выполнению наиболее |

|||||

приоритетной функции. Вход CU (count up, обозначается так- |

|||||

|

|

|

|

|

же С1 или "+1") предназначен для |

|

D |

СТ16 |

Q |

|

подачи подсчитываемых импульсов |

15 |

|

|

3 |

||

0 |

|

0 |

в режиме прямого счета, а вход CD |

||

1 |

|

|

|||

1 |

|

|

|

(count down, C2, "-1") – в режиме |

|

10 |

|

|

2 |

||

2 |

|

1 |

обратного счета. Входы CU и CD |

||

9 |

|

|

|||

|

|

|

|||

3 |

|

|

|

являются динамическими, причем |

|

|

|

|

6 |

||

|

|

|

|

||

|

|

|

2 |

|

|

11 |

|

|

|

сигналы на этих входах восприни- |

|

L |

|

|

|

||

|

|

|

7 |

маются схемой счетчика тогда, ко- |

|

|

|

|

3 |

||

|

|

|

|

гда они изменяют свое состояние с |

|

|

C |

|

|

|

|

5 |

U |

|

|

|

"0" на "1". При прямом счете на |

4 |

|

|

12 |

входе CD должно быть напряжение |

|

D |

|

PU |

|||

|

|

|

лог.1, при обратном счете напряже- |

||

|

|

|

|

|

|

14 |

R |

|

PD |

13 |

ние лог.1 должно быть на входе CU. |

|

|

|

|

||

|

|

|

|

|

Для записи в счетчик параллельного |

|

|

Рис. 2.2 |

|

кода предназначены входы D0-D3, |

|

|

|

|

при этом на вход L (load) должен |

||

|

|

|

|

|

|

быть подан сигнал логического нуля (иногда этот вход обозна- |

|||||

28

чают V или C). Установка счетчика в нулевое состояние (сброс) осуществляется подачей лог.1 на вход R и отрабатывается независимо от значений сигналов на остальных входах.

Выходы PU, PD (propagation carry up/down) предназначены для передачи сигнала переноса в соседнюю (старшую) микросхему. На выходе PU (обозначается также "≥15", "P") сигнал лог.0 появляется только в том случае, когда все триггеры счетчика находятся в единичном состоянии и поступил очередной импульс на вход CU. На выходе PD ("≤0", "B") сигнал лог.0 появляется в том случае, когда все триггеры счетчика находятся в нулевом состоянии и поступил очередной импульс на вход CD. При последовательном соединении нескольких микросхем К555ИЕ7 (то есть при увеличении разрядности счетчиков) выход РU предыдущей микросхемы соединяется со входом CU последующей, а выход РD предыдущей микросхемы со входом CD последующей.

Делители на базе счетчика ИЕ7

Рассмотрим реализацию на базе счетчика ИЕ7 делителя с постоянным коэффициентом Кдел и обнулением после прихода в заданное состояние. В этом случае в качестве дешифратора используют элемент И, на входы которого подают выходные сигналы с тех разрядов счетчика, которые в состоянии А= Кдел имеют значения лог.1. Выход логического элемента соединяют с R-входом счетчика. Такой счетчик последовательно прохо-

дит Кдел состояний от 0 до Кдел –1 (пребывание счетчика в состоянии А= Кдел оказывается кратковременным – он обнуляет-

ся). Результирующий сигнал может сниматься с выхода элемента И, однако он имеет малую длительность и для устойчивой работы последующих функциональных узлов лучше пользоваться выходным сигналом того разряда счетчика, который изменяет свое значение один раз за период счета. Более того, кратковременность импульса начальной установки может привести к необнулению некоторых разрядов счетчика, поэтому рекомендуется ввести либо схему задержки, удлиняющую им-

29

|

|

|

A |

|

|

|

|

D0 |

СT16 |

Q |

& |

|

|

|

0 |

|

|

|||

|

|

|

|

|

|

|

|

D3 |

|

1 |

S |

T |

N/A |

|

|

2 |

|

|||

|

|

|

|

|

|

|

лог.1 |

L |

|

3 |

R |

|

|

|

|

|

|

|

|

|

лог.1 |

CD |

|

|

|

|

|

|

|

PU |

|

|

|

|

|

|

|

|

|

|

|

|

CU |

|

|

|

|

|

|

R |

|

PD |

|

|

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

Рис. 2.3 |

|

|

|

пульс начальной установки, либо дополнительный триггер. Схема делителя на счетчике ИЕ7 с триггером приведена на рис. 2.3.

Для сокращения разнообразия микросхем RS-триггер можно выполнить на такой же микросхеме, как и дешифратор (И-НЕ) – см. материал, изученный в разделе «Триггеры» курса «Цифровая электроника». Более того, если отказаться от возможности выявления А=15, то и компаратор, и триггер можно разместить в одном корпусе, включающем три логических элемента.

Для счетчика ИЕ7, имеющего функцию загрузки произвольного кода, возможен и другой схемотехнический вариант делителя – с предварительной установкой исходного состояния В, от которого счет ведется до переполнения счетчика. В этом случае на входах D0-D3 устанавливают код В, выход PU или PD (в зависимости от желаемого направления счета) подключают ко входу L, так что после перехода счетчика в конеч-

30