- •Содержание

- •Введение

- •Анализ задания

- •Построение схемы

- •2.1. Блок, задающий тактовый сигнал

- •2.2. Блок обработки входного сигнала

- •2.3. Программируемый делитель частоты

- •2.4. Счетчик клеток

- •2.5. Блок управления фазами шагового двигателя

- •Временные диаграммы

- •Итоговая схема

- •Заключение

- •Список использованных источников

2.5. Блок управления фазами шагового двигателя

Рис.6 Схема блока управления фазами шагового двигателя

Рис. 7 Схема внутреннего устройства компаратора CMP

Блок управления 4-мя фазами шагового двигателя выполнен из 8 компараторов 7485. Каждая фаза управляется с помощью двух компараторов. Сигнал с шины CNT[3..0] счетчика клеток, поступает на входы A 3..0 микросхем 7485 и сравнивается с двумя 4-х битными константами, которые задают время включения BEG[3..0] и выключения END[3..0] фазы шагового двигателя. Когда число CNT больше или равно BEG и меньше или равно END , то на выходе компаратора CMP получается лог.1. Исходя из задания на курсовой проект фаза A должна работать с 0 по 2 счет, В- с 3 по 5, С- с 6 по 8, D- с 9 по 11. Это реализуется с помощью 4-х блоков компараторов CMP .Для фазы А константы были подключены с помощью VCC и GND 0-0000 и 2- 0100, для упрощения подключения остальных констант использовалась мега функция LPM_CONSTANT. Далее сигналы с 4-х модулей CMP попадаются на каскад из D-триггеров 74377 для подавления ложных вкл./выкл. D-триггеры вносят задержку вкл./выкл. фаз в один период тактового сигнала CLK, но это никак не влияет на корректность управления шаговым двигателем.

Временные диаграммы

Временная диаграмма блока, задающего тактовый сигнал CLK. Из диаграммы видно, что частота сигнала в 2кГц делится на 2.

Рис. 8 Временная диаграмма блока, задающего тактовый сигнал

Из данной диаграммы видно, что шифратор осуществляет преобразование входного позиционного кода в двоичный выходной на примере замкнутого 12 контакта галетного переключателя.

Рис. 9 Временная диаграмма блока, задающего тактовый сигнал

Далее проверим работоспособность программируемого делителя частоты. Когда на шине NUM[3..0] 0, то CKE постоянно выдает лог.1, когда на NUM[3..0]- CKE выдает сигнал с периодом в 2мс, при NUM[3..0] 15- CKE выдает сигнал с периодом в 16мс. Это доказывает, что схема работает верно.

Рис. 10 Временные диаграммы программируемого делителя частоты

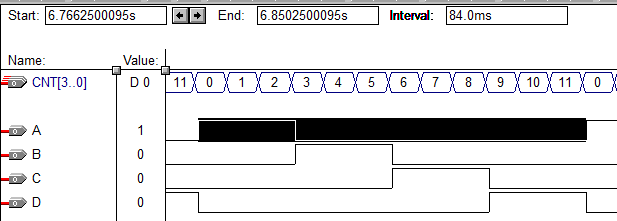

Из временных диаграмм видно, что счетчик клеток считает от 0 до 11. Период счета соответствует периоду сигнала CKE в положении галетного переключателя от 2 до 16, при положении 1 счетчик считает импульсы CLK.

Рис. 11 Временные диаграммы счетчика клеток

Ниже приведены временные диаграммы блока управления фазами шагового двигателя. Фаза A работает с 0 по 2 счет, В- с 3 по 5, С- с 6 по 8, D- с 9 по 11. Из-за D-триггеров происходит сдвиг на период сигнала CLK.

Рис. 11 Временные диаграммы блока управления фазами шагового двигателя

Итоговая временная диаграмма для схемы управления шагового двигателя:

Рис. 12 Итоговая временная диаграмма

Итоговая схема

Рис. 13 Итоговая схема

Заключение

В данной ходе курсовой работы была разработана схема, реализующая управление 4-мя фазами шагового двигателя. Такие двигатели применяются в механизмах, где детали поворачиваются точно на требуемый угол. Вращение вала шагового двигателя состоит из малых перемещений, так называемых, шагов. Период включения каждой фазы, т.е. шага, задавался положением 16-ти позиционного галетного переключателя.

Создание схемы и проверка ее работоспособности были проведены в среды MAX+plus.