Схемота / DgCXT_Labs_3

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №3

по дисциплине «Цифровая схемотехника»

Тема: Исследование систем триггеров

Студент гр. 7201 |

|

Шапошников В.А. |

Преподаватель |

|

Аристов С.А. |

Санкт-Петербург

2020

Цель работы:

Исследование систем триггеров

Экспериментальные результаты.

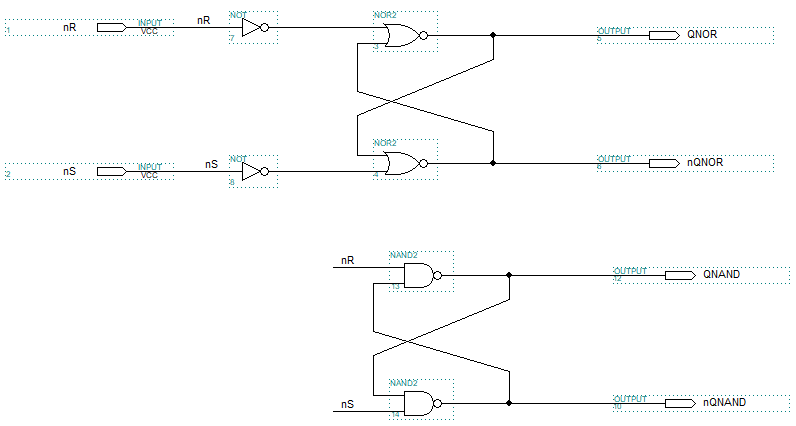

Исследование RS-триггеров на элементах 2ИЛИ-НЕ и 2И-НЕ

Рис.1 Схема для исследования RS-триггеров

на элементах 2ИЛИ-НЕ и 2И-НЕ

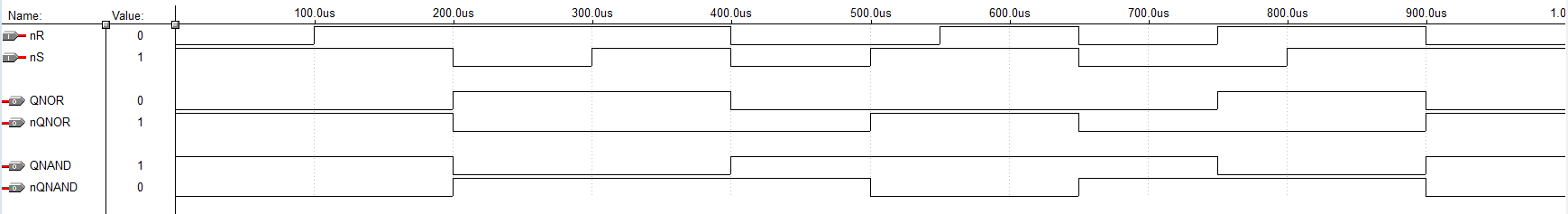

Рис.2 Временная диаграмма исследования RS-триггеров

на элементах 2ИЛИ-НЕ и 2И-НЕ

Табл.1 Переходы RS-триггера на логических элементах 2ИЛИ-НЕ

Текущеее состояние |

Новое состояние |

|||

nS |

nR |

Qn |

Qn+1 |

Qn+1 inv |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

Табл. 2 Переходы RS-триггера на логических элементах 2И-НЕ

Текущеее состояние |

Новое состояние |

|||

nS inv |

nR inv |

Qn |

Qn+1 |

Qn+1 inv |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

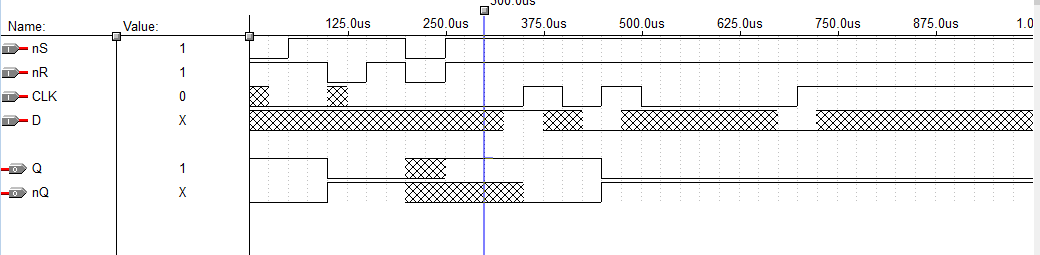

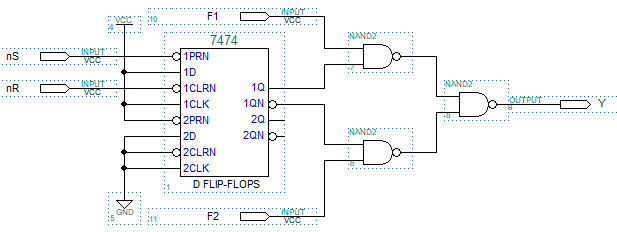

Исследование D-триггера с входами асинхронного сброса и установки

Рис.3 Схема для исследования D-триггера

Рис.4 Временная диаграмма исследования D-триггера

Табл.3 Переходы D-триггера с входами асинхронного сброса и установки

nS |

nR |

CLK |

D |

Qn |

Qn+1 |

Qn+1 inv |

0 |

1 |

x |

x |

x |

1 |

0 |

1 |

0 |

x |

x |

x |

0 |

1 |

0 |

0 |

x |

x |

x |

x |

x |

1 |

1 |

↑ |

1 |

x |

1 |

0 |

1 |

1 |

↑ |

0 |

x |

0 |

1 |

1 |

1 |

0 |

x |

x |

0 |

1 |

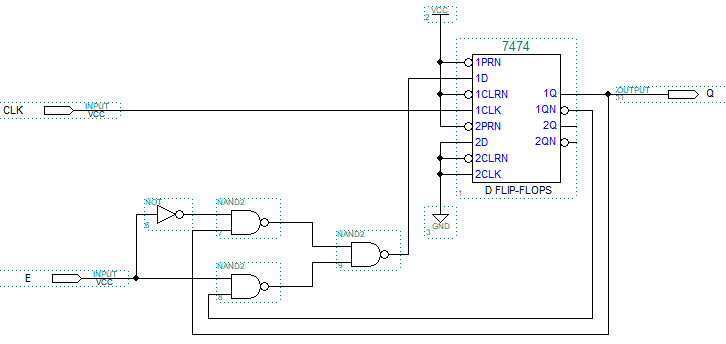

Исследование счетного триггера на основе D-триггера

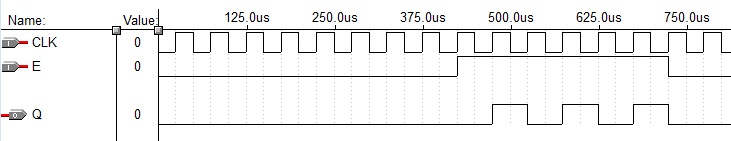

Рис.5 Схема счетного триггера на основе D-триггера

Рис.6 Временная диаграмма счетного триггера на основе D-триггера

Состояние выхода триггера меняется с изменением фронта сигнала на входе E. На вход этот вход подается переменный сигнал с частотой 20MГц, на выходе получается сигнал с частотой в 2 раза меньше – 10MГц. Из временной диаграммы видно что, выходной сигнал изменяется в 1 или 0 при изменении фронта сигнала на входе Е.

Исследование генератора сигнала с выбором частоты

Рис.7 Схема генератора сигнала с выбором частоты

Рис.8 Временная диаграмма генератора сигнала с выбором частоты

На временной диаграмме видны моменты перехода от одной частоты к другой, при подаче на соответствующий вход логического 0.

Вывод:

В ходе данной лабораторной работы были исследованы RS-триггеры на ЛЭ 2ИЛИ-НЕ и 2И-НЕ, D-триггер, счетного триггера на основе D-триггера, генератора сигнала с выбором частоты.

В RS-триггерах, при подаче сигнала Set, на прямом выходе всегда будет 1(0 изменится на 1, 1 останется 1). При подаче сигнала Reset всегда будет 0 (1 изменится на 0, 0 останется 0). При одновременной подаче сигналов Set и Reset триггер будет в метастабильном состоянии, при котором сигнал на прямом и инверсном входе будут одинаковы – что является неправильной работой схемы.

В D-триггере, подача сигнала Set даёт на выходе логическую 1, вне зависимости от того, какой сигнал был до этого. При подаче Reset аналогично для логического 0. При одновременной подаче этих сигналов триггер переходит в нестабильное состояние подобное такому же состоянию в RS-триггеру. При изменении тактового сигнала CLK (по фронту или срезу), изменяется сигнал на выходе Qn+1 в зависимости от сигнала D.

Сигнал на выходе счетного триггера (Т-триггера) изменяется с изменением фронта или среза на тактовом входе СLK, при положительном сигнале на входе E. В данной работе изменение сигнала происходило по фронту. При подаче сигнала с заданной частотой, данный триггер уменьшает эту частоту в 2 раза. Если же подать на вход E логический 0, то переключения на выходе блокируются.

Выбор частоту генератора сигнала происходит подачей логического 0 на один из входов F1 или F2.