Схемота / DgCxT_konspekt_lektsiy_1-14

.pdf

дов, так как при большем количестве разрядов выходные сигналы триггеров стар-

ших разрядов появляются позднее, чем управляющие фронты синхроимпульсов

(поступающих на вход первого триггера).

Для решения проблемы задержки в старших разрядах используются син-

хронные счетчики. По способу подачи синхроимпульсов такие счетчики парал-

лельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно.

Схема синхронного счетчика, реализованного на Т-триггерах, приведена на ри-

сунке.

|

|

|

Q0 |

|

|

Q1 |

|

|

|

|

Q2 |

|

|

|

|

Q3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

«1» |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

C |

|

|

|

|

|

|

C |

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C

Рисунок 67 – Внутренняя структура синхронного счетчика

В этой схеме первый триггер имеет на входе Т логическую 1 и переключа-

ется по любому тактовому импульсу на входе С. Второй триггер (выход Q1) пе-

реключается только тогда, когда на его входе Т имеется логическая 1. Это про-

изойдет, когда первый триггер (выход Q0) переключится в состояние логической

1 (см. тактовую диаграмму). Третий триггер должен переключаться только тогда,

когда оба предыдущих триггера находятся в состоянии логической 1 и для этого используется логический элемент И. Аналогично для четвертого триггера разре-

шение на переключение будет подано только тогда, когда все предыдущие триг-

геры будут находиться в состоянии логической 1 (еще один логический элемент И совместно с предыдущим логическим И и выходом третьего триггера). Таким

образом каждый из триггеров «получает разрешение» на переключение в зависи-

мости от состояния предыдущих триггеров, а переключаются они одновременно,

поскольку тактовые импульсы подаются параллельно на все триггеры.

С |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

Q0 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

t |

|

|

|

|

1 |

|

|

|

Q2 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

t |

Рисунок 68 – Тактовые диаграммы синхронного счетчика

Синхронный счетчик обладает повышенным быстродействием, однако, за счет последовательного формирования управляющих уровней, на входы Т счет-

ных триггеров, быстродействие несколько уменьшается. Поскольку счетчик имеет одну общую линию синхронизации, состояние триггеров меняется син-

хронно, т.е. те триггеры, которые по синхроимпульсу должны изменить свое со-

стояние, делают это одновременно, что существенно повышает быстродействие синхронных счетчиков.

Следует заметить, что практически вся современная цифровая электроника синхронная. Асинхронные счетчики в основном используются только в тех слу-

чаях, когда выходной сигнал счетчика не связан по фазе с любыми другими ча-

стями схемы. Например, при делении частоты генератора 32768 Гц на 215 для по-

лучения секундных импульсов для часов или секундомера, эти импульсу явля-

ются входными для схемы и их фаза не влияет на работу схемы.

Неделя 9

9.1 Логический элемент с Z состоянием

Как известно в цифровой электронике существуют понятия «логическая единица» и «логический ноль». Такие выходы нельзя объединять вместе. Если на одном выходе будет лог. 1, а на другом лог. 0, то между ними образуется короткое замыкание. Результатом такого объединения может быть выход из строя транзисторов, ну или по крайней мере повышенное энергопотребление

(разогрев микросхемы) и некоторое «неопределенное» состояние на выходе между лог. 1 и лог. 0.

В некоторых случаях такое объединение сигналов необходимо. Напри-

мер, для передачи на вход устройства информации от нескольких источников

(хотя, конечно, можно воспользоваться и мультиплексором…) или передачи данных в двух направлениях (память компьютеров работает как на запись, так и на чтение данных). Также в цифровых устройствах часто применяется

«шина» - несколько сигналов одинакового назначения, управляемых как пра-

вило одновременно. Для управления шинами и было введено третье «высо-

коимпедансное состояние», когда дополнительный ключ просто отключает вы-

ход и он соединяется с остальной схемой через высокое сопротивление (импе-

данс) закрытого транзистора. Высокоимпедансное состояние, высокоомное со-

стояние, Z-состояние или состояние «Выключено» — состояние вывода циф-

ровой микросхемы, при котором сопротивление между её внутренней схемой,

подключённой к данному выводу, и внешней схемой очень велико.

Такой выход не влияет на подключённую к нему внешнюю цепь схемы,

следовательно к одной цепи схемы можно подключать несколько выходов мик-

росхем, при условии, что в каждый момент времени только один выход акти-

вен, а все остальные находятся в высокоимпедансном состоянии.

Физически Z-состояние реализуется закрытыми транзисторами, работа-

ющими в ключевом режиме, как показано на рисунке.

|

Uп |

Uп |

VT4 SW2 |

|

|

VT3 |

|

Uвых |

Uвых |

Uвх |

Uвх |

VT2 |

|

EN |

VT1 |

SW1 |

|

||

|

|

Рисунок 69 – Классический и с Z-состоянием КМОП инвертеры

С левой стороны изображен классический КМОП инвертор, имеющий

«нормальные» выходные уровни. С правой стороны инвертор снабжен допол-

нительными транзисторами VT1, VT4. Если уровень сигнала на входе EN логи-

ческая 1, то транзистор VT1 открыт и через него к общему проводу подключен транзистор VT2. Аналогично, через открытый транзистор VT4 к питанию под-

ключен транзистор VT3. В результате КМОП инвертор на транзисторах VT2, VT3 ничем не отличается от инвертора с левой стороны рисунка. Если уровень сигнала на входе EN логический 0, то транзистор VT1 закрыт и отключает тран-

зистор VT2 от общего провода (SW1 открыт). Аналогично, закрытый транзи-

стор VT4 отключает транзистор VT3 от питания (SW2 открыт). В результате через транзисторы VT2, VT3 ток протекать не может и выход инвертора нахо-

дится в Z-состоянии.

Вывод микросхемы, переведённый в Z-состояние, ведёт себя как не под-

ключённый к ней. Внешние устройства, подключенные к этому выводу, могут изменять напряжение на нём в пределах напряжения питания, не влияя на ра-

боту микросхемы. И наоборот — схема не мешает внешним устройствам ме-

нять напряжение на выводе микросхемы.

9.2 Двунаправленный шинный формирователь

На основе элементов с тремя состояниями изготавливаются шинные фор-

мирователи. Шинные формирователи используются в цифровой и вычислитель-

ной технике для подключения к одному проводу нескольких устройств, при со-

блюдении условия, что в любой промежуток времени по этому проводу обмени-

ваться информацией будут только два устройства. Кроме того, шинные формиро-

ватели используются для усиления тока, идущего от источника к приемнику ин-

формации, поскольку таких приемников может быть достаточно много.

Внутренняя структура шинного формирователя показана на рисунке. Логи-

ческие элементы, обозначенные цифрой 1 это элементы с Z-состоянием.

I0 |

|

|

O0 |

|

1 |

|

|||

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I1 |

|

|

|

|

|

|

1 |

|

O1 |

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

1 |

|

|||||||

EN |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

Упр. 1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

||||||||

& |

|

|

|

|

|

|

||||||||

Dir |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

Упр. 2 |

|

|

1 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

& |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 70 – Внутренняя структура шинного формирователя

Вход элемента, обозначенный «X», управляет его состоянием – при лог. 1

передача сигнала с входа на выход разрешена, при лог. 0 запрещена (элемент находится в Z-состоянии). Вход EN управляет разрешением передачи данных.

Если на нем лог. 0, то на выходах логических элементов И будет лог. 0 и все ло-

гические элементы будут находиться в Z-состоянии блокирую передачу сигнала в любых направлениях. При наличии лог. 1 на входе EN передача данных будет разрешена. При лог. 1 на входе Dir логический элемент И выдаст лог.1 на выходе

«упр.1» разрешив тем самым передачу сигналов от входов I (I0, I1) к выходам O (O0, O1). Передача сигналов в обратном направлении будет заблокирована, по-

скольку сигнал Dir подается на вход второго логического элемента И через инвер-

тер, и на его выходе «упр. 2» будет лог.0. При подаче лог. 0 на вход Dir ситуация сменится на противоположную и заблокированы будут логические элементы, пе-

редававшие сигнал в «прямом направлении» (от I к O), а разрешена работа логи-

ческих элементов, передающих сигналы от O к I. Таким образом сигнал Dir опре-

деляет направление передачи сигналов – от входа к выходу (при 1) или от выхода к входу (при 0).

На рисунке приведен пример четырехразрядных шинных формирователей К589АП16 и К589АП26.

Рисунок 71 – Шинные формирователи К589АП16 и К589АП26

9.3 Логические элементы с выходом типа «открытый коллектор»

Выходы некоторых цифровых микросхем выполнены так, что верхний вы-

ходной транзистор отсутствуют. Это так называемые логические элементы с от-

крытым коллектором.

Рисунок 72 – Внутренняя структура элемента с открытым коллектором

На выходе такого логического элемента формируется сигнал, только низ-

кого уровня, поскольку отсутствуют транзисторы, которые могли бы сформиро-

вать уровень логической 1. Для возможности формирования логической единицы коллектор выходного транзистора подключают к источнику питания через внеш-

нюю нагрузку, как правило резистор. Такой резистор называют подтягивающим

(pull-up resistor).

Открытый коллектор в основном используется для:

1. Управления внешними устройствами, работающими при других напряжениях питания. Например, К155ЛА11 имеет предельное выходное напря-

жение до 30 В.

2. Объединения нескольких выходов. Логические элементы с открытым коллектором допускают параллельное соединение нескольких выходов к общей нагрузке. Такое объединение выходов называют монтажное И.

Рисунок 73 – Подключение нескольких логических элементов по схеме монтажное И

В схеме монтажное И каждый компонент схемы действует как элемент об-

щей системы. Если хотя бы на одном из выходов будет низкий потенциал, то низ-

кий потенциал окажется и на выходе всей системы. Чтобы обеспечить логическую

1 на общем выходе, необходимо иметь логические 1 на всех выходах.

9.4 Логические элементы – преобразователи уровней

Цифровые микросхемы, выполненные по разным технологиям (например ТТЛ и КМОП) зачастую имеют различное питание и разные по напряжению ло-

гические уровни. При их совместном применении необходимо преобразовывать уровни сигналов, чтобы обеспечить передачу сигналов без создания «аварийных» ситуаций.

Снижение уровня напряжения, например с 5В до 3В может быть реализо-

вано простейшим резистивным делителем напряжения. Никаких дополнительных элементов при этом не потребуется.

Повышение уровня напряжения может быть легко реализовано с помощью транзисторного ключа, либо логического элемента с открытым коллектором и подтягивающего резистора.

UВХ = 0-5В

R1 2k

UВЫХ = 0-3В

R2 3k |

СПАР |

|

+UПИТ = 5В

|

|

|

R1 |

|

R2 |

|

|

|

|

||

|

+Uпит = 3В |

|

|

|

|

|

UВЫХ = 0-5В |

||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||

|

|

UВХ = 0-3В |

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

СПАР |

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R3 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 74 – Пример реализации понижения и повышения уровня напряжения

Однако необходимо иметь в виду, что в любых схемах имеются паразитные емкости (СПАР) на заряд/разряд которых через резисторы тратится определенное время.

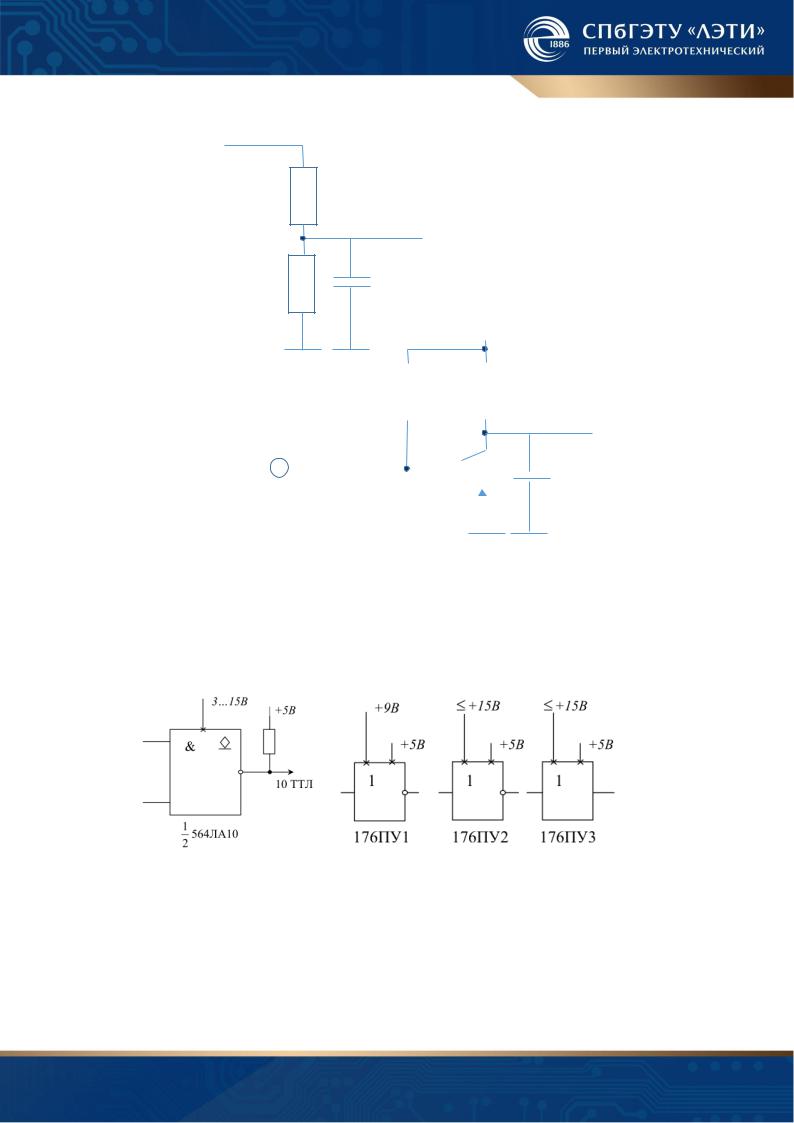

Рисунок 75 – Микросхемы преобразователей уровня

В результате рассмотренные простейшие преобразователи уровней обла-

дают низким быстродействием. Для сохранения необходимой скорости переклю-

чения следует использовать специализированные цифровые микросхемы преоб-

разователей уровня. Примеры микросхем преобразователей уровня представлены

на рисунке.