Схемота / DgCxT_konspekt_lektsiy_1-14

.pdf

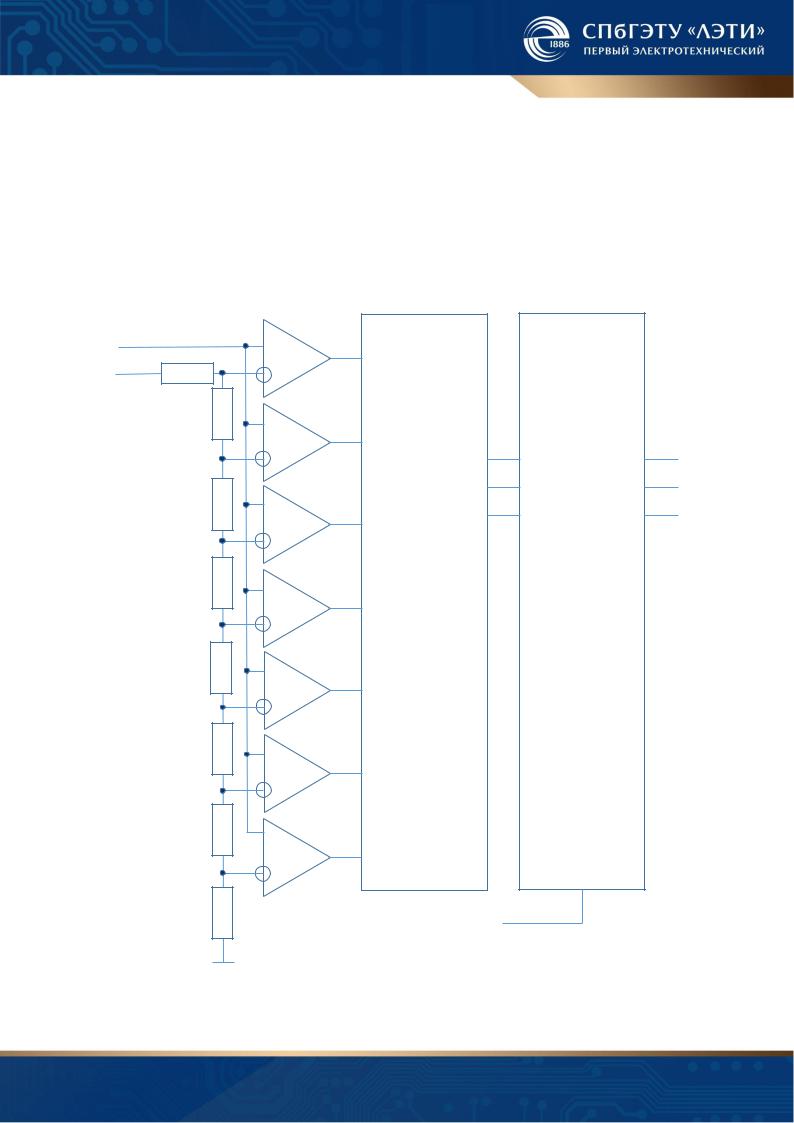

12.2 Параллельный АЦП

АЦП этого типа осуществляют квантование сигнала одновременно с помо-

щью набора компараторов, включенных параллельно источнику входного сиг-

нала. На рисунке показана реализация параллельного метода АЦ-преобразования для 3-разрядного числа.

UВХ |

|

|

|

K7 |

|

|

= = |

|

|

|

R |

|

|

|

UОП |

|

|

|

|

|

|

|

|

|

|

|

R |

|

K6 |

|

|

|

= = |

|

|

|

R |

= = |

K5 |

|

|

|

|

|

|

|

R |

= = |

K4 |

|

|

|

|

|

|

|

R |

|

K3 |

|

|

|

= = |

|

|

|

R |

= = |

K2 |

|

|

|

|

|

|

|

R |

|

K1 |

|

|

|

= = |

R

Приоритетный Регистр шифратор

C

Синхронизация

Q0

Q1

Q2

Рисунок 95 – Структурная схема параллельного АЦП на 3 разряда

С помощью трех двоичных разрядов можно представить восемь различ-

ных чисел, включая нуль. Необходимо, следовательно, семь компараторов. Семь соответствующих эквидистантных опорных напряжений образуются с помощью

резистивного делителя.

В зависимости от входного напряжения на выходах компараторов будет либо лог 0, либо лог. 1. Преобразование состояния компараторов в трехзначное двоичное число выполняет приоритетный шифратор, диаграмма состояний кото-

рого приведена в таблице:

Входное напряжение |

Состояние компараторов |

Выходы |

||||||||

|

|

|

|

|

|

|

|

|

|

|

Uвх/h |

К7 |

К6 |

К5 |

К4 |

К3 |

К2 |

К1 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

4 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

6 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Подключение приоритетного шифратора непосредственно к выходу АЦП может привести к ошибочному результату при считывании выходного кода по-

скольку время срабатывания компараторов не одинаковое и в процессе преобра-

зования могут возникнуть «промежуточные» состояния, когда одни компараторы уже изменили выходной код, а другие еще нет. Для устранения данной проблемы применяют УВХ, в котором «запоминают» аналоговый сигнал на время преобра-

зования и регистр, в который одновременно переписываются все разряды по им-

пульсу синхронизации.

Благодаря одновременной работе компараторов параллельный АЦП яв-

ляется самым быстрым. Недостатком такого АЦП является высокая сложность.

Действительно, N-разрядный параллельный АЦП сдержит 2N-1 компараторов и 2N

согласованных резисторов. Следствием этого является высокая стоимость и зна-

чительная потребляемая мощность.

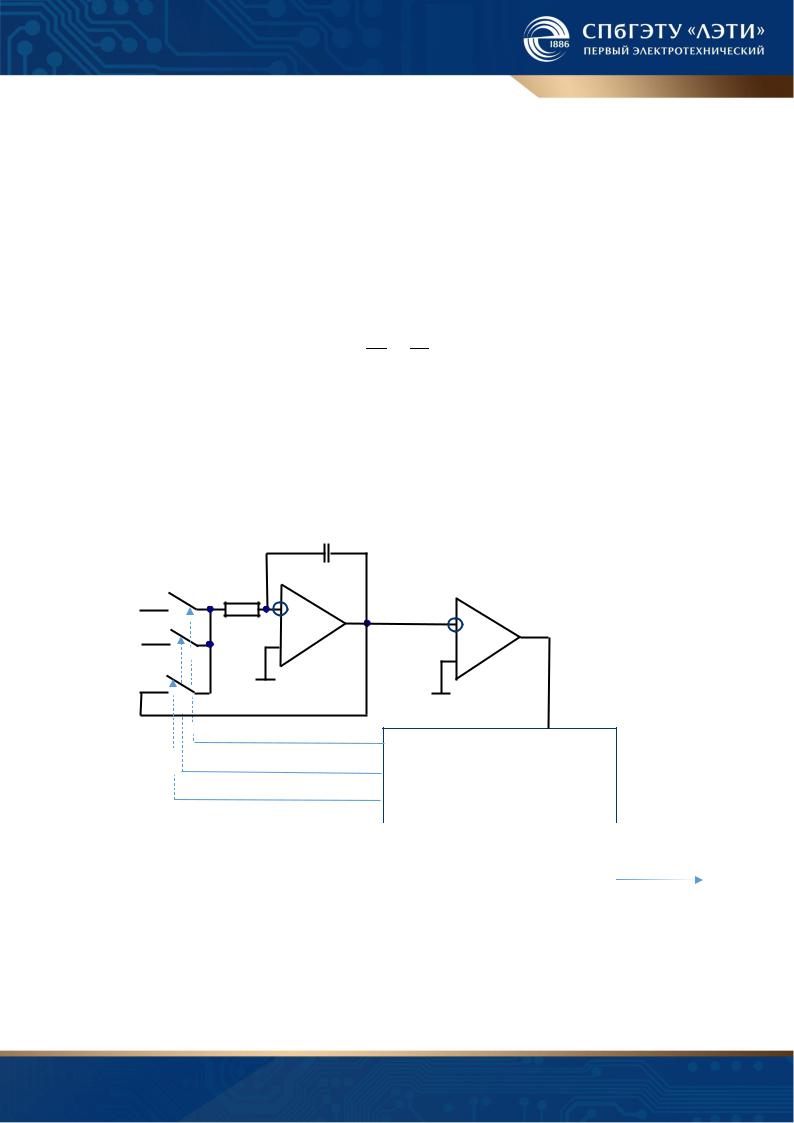

12.3АЦП последовательных приближений

Воснове АЦП данного типа лежит специальный регистр последовательного приближения. В начале цикла преобразования все выходы этого регистра уста-

навливаются в лог. 0, за исключением старшего разряда. Это формирует на вы-

ходе собственного цифро-аналогового преобразователя напряжение, значение ко-

торого равно ½ полной шкалы АЦП. После этого выход компаратора переключа-

ется в состояние, определяющее разницу между сигналом на выходе ЦАП и из-

меряемым входным напряжением. Это состояние записывается в старший разряд n (если напряжение на входе больше ½ полной шкалы, то остается лог. 1, в про-

тивном случае устанавливается лог. 0). Затем в следующий разряд (n-1) принуди-

тельно записывается лог. 1. Это формирует на выходе собственного ЦАП напря-

жение Uвых, значение которого равно либо ¼, либо ¾ входного диапазона АЦП в зависимости от результатов на предыдущем шаге преобразования (¼ или ½ + ¼,

если в старшем разряде осталась лог. 1) . Полученное напряжение Uвых ЦАП сравнивается с Uвх, результат записывается в (n-1) разряд. И так далее.

УВХ |

|

|

|

UВХ |

Регистр |

Выходной код |

|

= = |

|||

последовательных |

|||

С |

|

||

приближений |

|

||

|

|

ЦАП

Рисунок 96 – Структура АЦП последовательных приближений

U |

|

|

|

|

|

|

|

|

11111111 |

|||

UОП |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11000000 |

|||

UОП /2 |

UЦАП |

|

|

|

|

|

10000000 |

|||||

|

|

UВХ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01100000 |

||

UОП /4 |

|

|

|

|

|

|

|

|

01000000 |

|||

10000000 |

|

|

01100000 |

01101000 |

|

|

01100110 |

|

|

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

01000000 |

|

01110000 |

|

01100100 |

01100101 |

|

|||||

t

Рисунок 97 – Работа АЦП последовательных приближений

Рассмотрим работу АЦП на примере 8-разрядного преобразователя. В

начале цикла преобразования все выходы регистра устанавливаются в лог. 0, стар-

ший в 1 (10000000). На выходе внутреннего ЦАП формируется сигнал, значение которого равно половине входного диапазона АЦП (половине опорного напряже-

ния UОП/2). Измеряемое напряжение меньше, значит в старший разряд записыва-

ется 0. Затем в следующий разряд – 7 записывается 1 (UЦАП = ¼ ·UОП). Измеряемое напряжение больше, значит в 7 разряд записывается 1 (01000000). В 6 разряд за-

писывается 1, UЦАП = 3/8 UОП (01100000). Uвх > UЦАП следовательно в 6-м разряде будет 1. Аналогично, в 5-м разряде будет 0, в 4-м 0, в 3-м 1, во 2-м 0, в 1-м 1.

АЦП последовательных приближений имеют среднее быстродействие и среднюю разрядность (наиболее распространенные 10-18 разрядов), но при этом они достаточно просты в изготовлении и потому являются самыми распростра-

ненными. Достаточно сказать, что практически в каждом микроконтроллере име-

ется встроенный АЦП и это АЦП последовательных приближений.

12.4 АЦП с двойным интегрированием

Основным элементом интегрирующего АЦП является интегратор, постро-

енный на основе операционного усилителя.

C

UВХ |

R |

DA1 |

|

UВЫХ |

|||

|

|

Рисунок 98 – Схема интегратора на ОУ

Если считать ОУ идеальным, то выходное напряжение можно определить,

как:

|

ВХ |

|

= − |

ВЫХ |

|

|||

|

|

|

||||||

|

|

|

||||||

|

|

1 |

|

|

|

|

||

ВЫХ = − |

|

∫ ВХ( ) + |

||||||

|

||||||||

|

|

0 |

|

|

||||

|

|

|

|

|

|

|

||

где const – постоянная, учитывающая начальные условия.

UВХ

U1

t

|

U2 |

UВЫХ |

|

T1 |

T2 |

t

Рисунок 99 – Напряжение на входе и выходе интегратора

При последовательном интегрировании постоянных положительного и от-

рицательного напряжений при старте с нулевого напряжения и окончании инте-

грирования при нулевом выходном напряжении будет соблюдаться баланс – от-

ношение амплитуд напряжений обратно пропорционально времени интегрирова-

ния.

1 1 + 2 2 = 0

1 = 22 1

Это свойство интегратора используется в АЦП двойного интегрирования. В

таком АЦП используется интегратор на ОУ, на вход которого через коммутатор подается входное положительное напряжение, опорное отрицательное напряже-

ние, либо выход интегратора замыкается на его вход.

|

C |

S1 |

R |

+UВХ |

U |

S2 |

ВЫХ |

== |

|

-UОП |

|

S3 |

|

Схема управления

|

|

Выходной |

|

Счетчики |

|||

код |

|||

|

|

||

|

|

|

|

Рисунок 100 – Схема АЦП двойного интегрирования

Компаратор определяет момент достижения выходным напряжением ин-

тегратора нуля и в эти моменты времени, в зависимости от текущей фазы измере-

ния, схема управления переключает коммутатор на нужный источник сигнала и запускает счет времени. В стадии интегрирования ключ S1 замкнут, а ключи S2 и

S3 разомкнуты. Интегратор И интегрирует положительное входное напряжение

+Uвх. Время интегрирования входного напряжения ТИНТ постоянно.

UВХ |

U2 |

|

|

|

|

|

U1 |

UВЫХ |

t |

T2 |

|

|

|

TИНТ |

T1 |

U1 |

t |

|

|

||

U2 |

Установка |

|

нуля |

||

|

||

UПОМЕХИ |

|

Рисунок 101 – Тактовые диаграммы работы АЦП двойного интегрирования

К моменту окончания интегрирования напряжение на выходе интегратора будет зависеть от амплитуды входного напряжения – для большего входного U2

выходное напряжение будет очевидно больше.

После окончания стадии интегрирования ключ S1 размыкается, а ключ S2

замыкается, и на вход интегратора поступает отрицательное опорное напряжение

-Uоп. При этом -Uоп противоположно по знаку входному напряжению, что явля-

ется обязательным условием. В стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине. Стадия счета заканчивается, ко-

гда выходное напряжение переходит через ноль. При этом компаратор переклю-

чается и счет останавливается. В процессе счета подсчитывается количество так-

товых импульсов и результирующий выходной код формируется из отношения количества тактов при интегрировании входного напряжения (всегда одинаковое)

к количеству тактов при интегрировании опорного напряжения (зависит от напря-

жения на выходе интегратора к моменту начала интегрирования опорного напря-

жения). Эти величины обратно пропорциональны амплитудам входного и опор-

ного напряжений.

Перед началом следующего цикла измерения ключ S2 размыкается, а ключ

S3 замыкается, и на вход интегратора поступает его выходное напряжение, тем самым производится установка нуля, чтобы устранить смещение.

Отличительной особенностью метода двухтактного интегрирования явля-

ется то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Достаточно, чтобы тактовая частота в течение времени оставалась по-

стоянной. Кроме того, если период интегрирования равен периоду напряжения промышленной сети (20 мс для частоты 50Гц) то помеха от сети будет полностью компенсирована.

Относительным недостатком такого АЦП является малое быстродействие,

не превышающее как правило нескольких измерений в секунду. С другой сто-

роны, основное применение таких АЦП — это измерительные приборы (мульти-

метры), в которых нет необходимости иметь высокое быстродействие.

12.5 Сигма-дельта АЦП

Для проведения измерений часто требуется АЦП c большой разрешающей способностью. Сигма-дельта АЦП могут обеспечивать разрешающую способ-

ность до 24 разрядов, но при этом уступают в скорости преобразования. Так, в

сигма-дельта АЦП при 16 разрядах можно получить частоту дискретизации до

100К отсчетов/сек, а при 24 разрядах эта частота падает до 1К отсчетов/сек и ме-

нее, в зависимости от устройства. Обычно сигма-дельта АЦП применяются в раз-

нообразных системах сбора данных и в измерительном оборудовании, когда не

требуется высокая частота дискретизации и необходимо разрешение более 16 раз-

рядов.

Архитектура сигма-дельта АЦП относится к классу интегрирующих АЦП.

Но основная особенность сигма-дельта АЦП состоит в том, что частота следова-

ния выборок, при которых, собственно, и происходит анализ уровня напряжения измеряемого сигнала, существенно превышает частоту появления отсчетов на вы-

ходе АЦП (частоту дискретизации). Эта частота следования выборок называется частотой передискретизации.

Основные узлы АЦП — это сигма-дельта модулятор и цифровой фильтр.

|

|

|

|

|

|

Выходной |

UВХ |

|

|

Интегратор |

|

АЦП |

код |

+ |

|

|

|

|||

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

ЦАП

Рисунок 102 – Структура сигма-дельта модулятора

Работа сигма-дельта модулятора основана на вычитании из входного сиг-

нала Uвх величины сигнала на выходе ЦАП, полученной на предыдущем такте ра-

боты схемы. Полученная разность интегрируется, а затем преобразуется в код па-

раллельным АЦП невысокой разрядности. Последовательность кодов поступает на цифровой фильтр нижних частот. Чаще всего используются однобитные сигма-

дельта модуляторы, в которых в качестве АЦП используется компаратор, а в ка-

честве ЦАП - аналоговый коммутатор.

|

|

|

|

|

|

Выходной |

UВХ |

+ |

|

Интегратор |

|

Компаратор |

код |

|

|

|

||||

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

|

|

|

+UОП

S

-UОП

Рисунок 103 – Структура однобитного сигма-дельта модулятора

Для формирования выходного кода такого преобразователя необходимо ка- ким-либо образом преобразовать последовательность бит на выходе компаратора в виде унитарного кода в двоичный код. Это можно сделать с помощью двоичного счетчика. В этом случае необходимо сформировать фиксированный цикл преобразования (время подсчета выходных импульсов сигма-дельта модулятора). После его окончания должно производиться считывание результата и обнуление счетчика.

Преобразование Uвх = 0,6 В в цифровой код при Uоп = 1 В (счет идет только тогда, когда на выходе компаратора лог. 1):

№ |

U на входе инт. |

U на выходе инт. |

Компаратор |

U ЦАП |

код |

1 |

0,6 |

0,6 |

1 |

1 |

0001 |

2 |

-0,4 |

0,2 |

1 |

1 |

0010 |

3 |

-0,4 |

-0,2 |

0 |

-1 |

0010 |

4 |

1,6 |

1,4 |

1 |

1 |

0011 |

5 |

-0,4 |

1,0 |

1 |

1 |

0100 |

6 |

-0,4 |

0,6 |

1 |

1 |

0101 |

7 |

-0,4 |

0,2 |

1 |

1 |

0110 |

8 |

-0,4 |

-0,2 |

0 |

-1 |

0110 |

9 |

1,6 |

1,4 |

1 |

1 |

0111 |

10 |

-0,4 |

1,0 |

1 |

1 |

1000 |

11 |

-0,4 |

0,6 |

1 |

1 |

1001 |

12 |

-0,4 |

0,2 |

1 |

1 |

1010 |