DgCXT_Lab_4

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №4

по дисциплине «Цифровая схемотехника»

Тема: «Устройства последовательностной логики на триггерах»

Студентка гр. 7201 |

|

Семирякова А.А. |

Преподаватель |

|

Аристов С. А. |

Санкт-Петербург

2020

Теоретические материалы

Простейшие электронные микросхемы и схемы последовательностной логики, которые можно построить на триггерах – это счетчики и регистры. В предыдущей лабораторной работе был подробно изучен универсальный триггер типа 74HC(HCT)74, который сочетает в себе функциональность D- и RS-триггера, или, как еще говорят, является D-триггером с асинхронными входами установки и сброса.

На этом триггере, в принципе, при помощи вспомогательных ЛЭ можно построить любое устройство последовательностной логики. Остановимся на схемах, которые не слишком сложны в сборке и анализе.

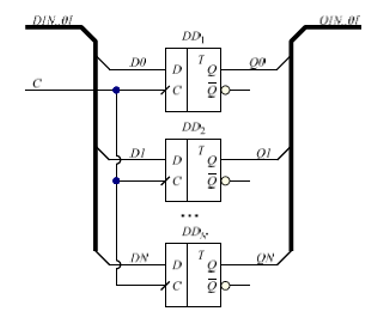

Самая простая схема на универсальных триггерах – это схема параллельного регистра. Параллельный регистр – устройство, способное хранить несколько бит данных, которые можно рассматривать и как комбинацию независимых битов, и как число. Если у N триггеров объединить тактовые входы, объединить входы D и выходы Q триггеров в шины, то по фронту тактового входа вся схема будет запоминать многоразрядную кодовую комбинацию или число. То, что занесено в память регистра, доступно на его выходе – шине такой же разрядности, как и D.

Рис.1. Простейший параллельный регистр

Тактовая диаграмма такой схемы предельно проста: по каждому фронту сигнала C данные, присутствующие на входе D[N..0], записываются в регистр и поступают на выход Q[N..0], т.е. для любого такта справедливо выражение 𝑄[𝑁..0]𝑛+1 = 𝐷[𝑁..0]𝑛. Использованная форма записи имен шин, т.е. групп сигналов, имеющих общий смысл, вида имя_шины[старший_индекс..младший_индекс], является общепринятым во многих современных программных средах для разработки цифровых интегральных схем и конфигураций микросхем программируемой логики.

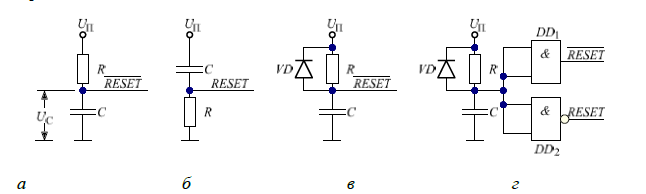

Данные (или число), хранимые параллельным регистром, показанным на Рис. 42, непосредственно после подачи питания на схему не определены, и являются случайным набором битов. В некоторых случаях это не является проблемой с точки зрения функционирования схемы, использующей регистр, в других случаях это совершенно недопустимо. Для того чтобы задать, какое значение будет храниться в том или ином триггере схемы после подачи питания, используют D-триггеры с входами асинхронной установки 𝑆 и сброса 𝑅.

Эти входы подключаются к схеме начальной инициализации, или, как еще говорят, схеме начального сброса. Требования к схеме начального сброса предельно просты: после включения питания схема должна выдать на выход логический ноль в течение времени, достаточного для сброса всех подключенных триггеров. Обычно длительность импульса сброса измеряется временами в несколько мс, что с лихвой перекрывает потребности любой последовательностной логики.

Рис.2. Варианты простых схем начального сброса

Обработка результатов

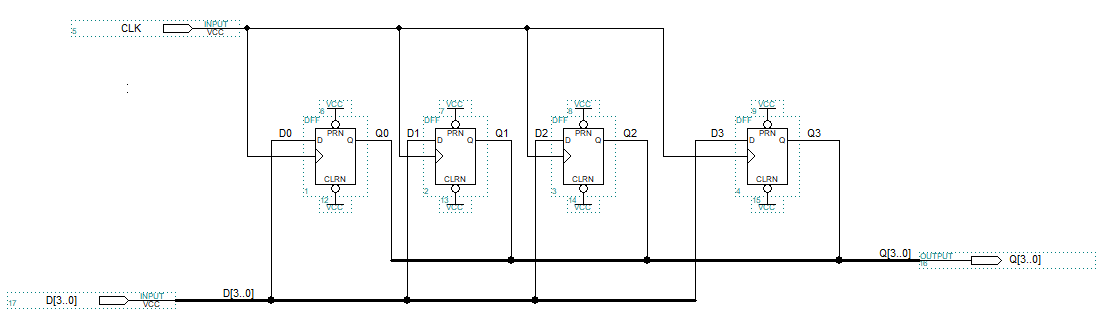

Четырехразрядный параллельный регистр

Рис.3. Схема 4-разрядного параллельного регистра

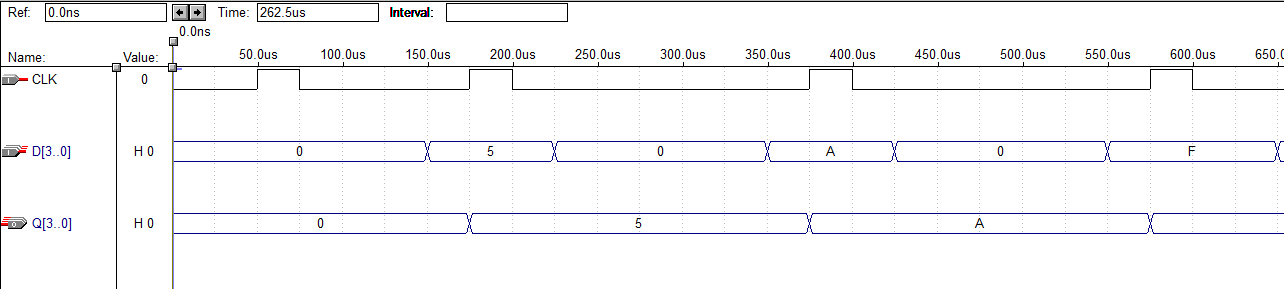

Рис.4. Тактовая диаграмма

Таблица 1. Исследование работы 4-разрядного параллельного регистра

Код

переключателей

|

|

|

0h (0000b) |

0 |

0 |

5h (0101b) |

0 |

5 |

Ah (1010b) |

5 |

A |

Fh (1111b) |

A |

F |

Асинхронный четырехразрядный счетчик

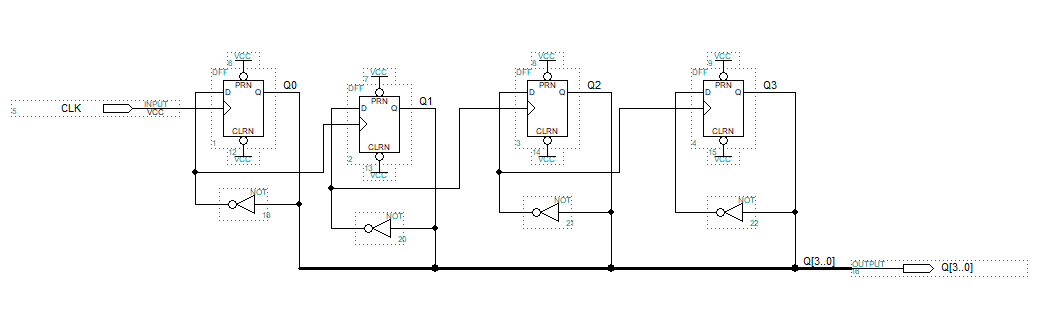

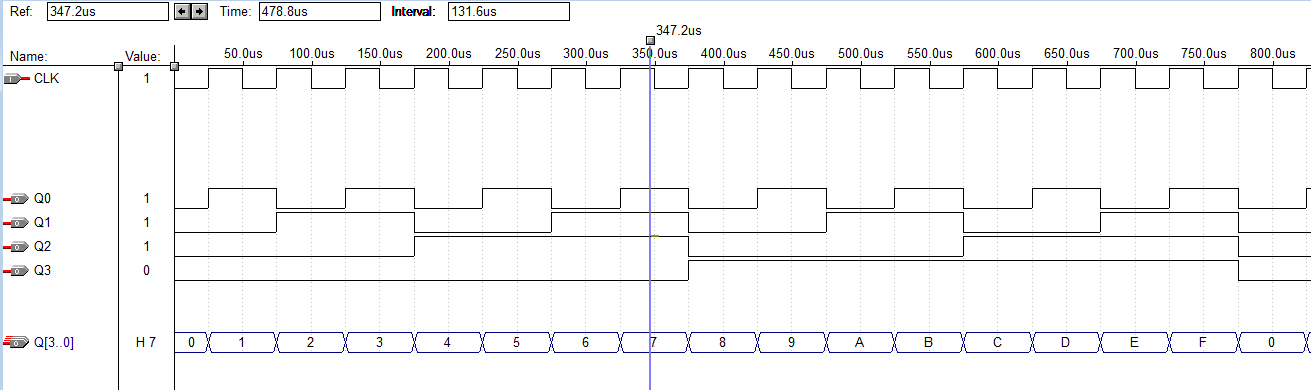

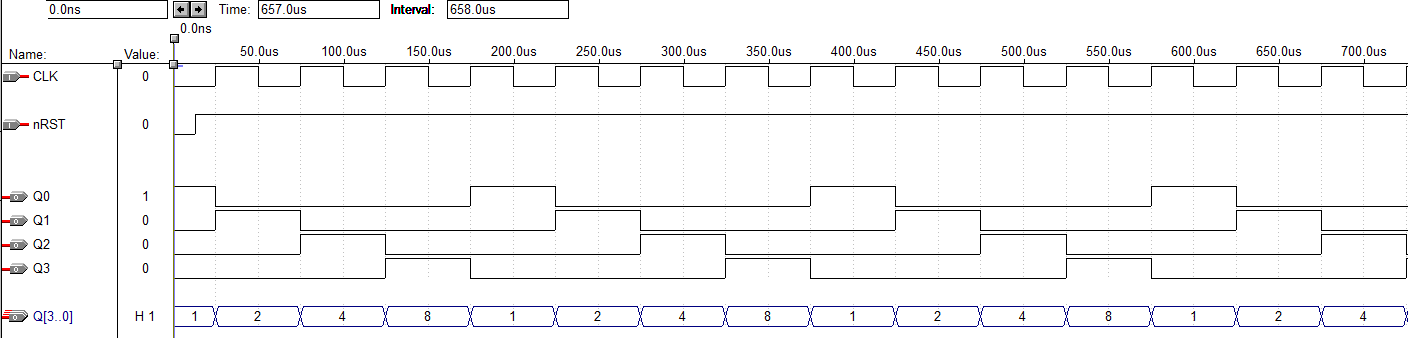

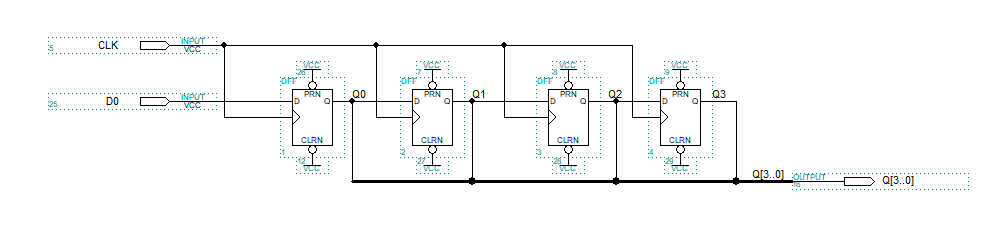

Рис.5.Схема асинхронного четырехразрядного счетчика

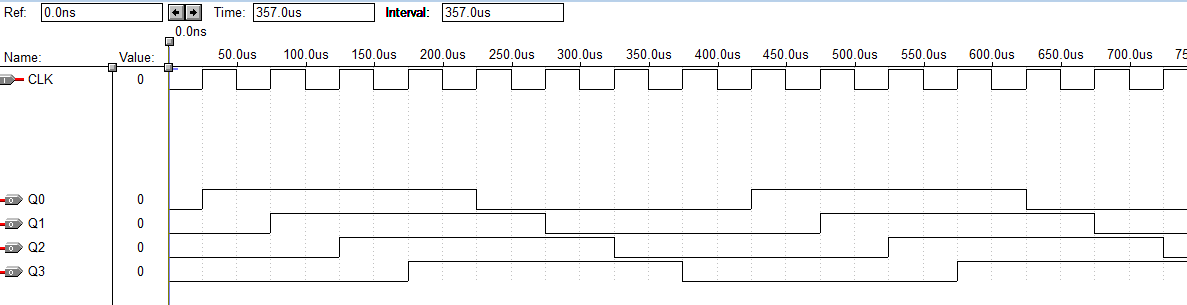

Рис.6. Тактовая диаграмма асинхронного счетчика (на тактовой диаграмме продублирована шина Q[3..0] Для демонстрации в развернутом виде)

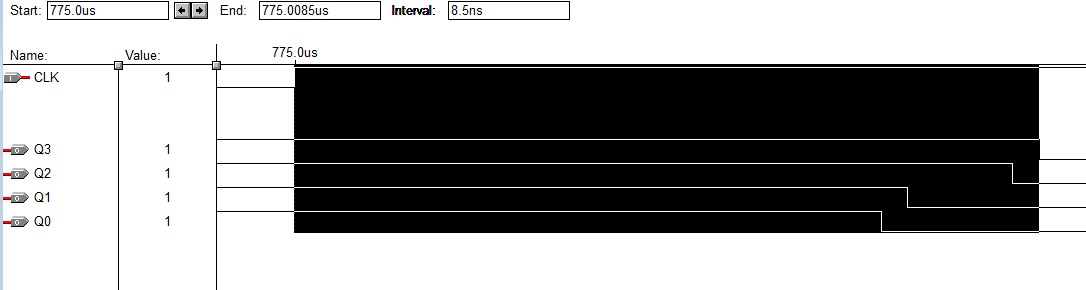

Рис. 7. Время накопленной задержки

Суммарная задержка тактового сигнала от 4-х триггеров τ=12,3 нс.

Таким образом каждый триггер вносит задержку τ1=3,075нс.

Рис.

8. Время задержки после получения

тактового сигнала

Рис.

8. Время задержки после получения

тактового сигнала

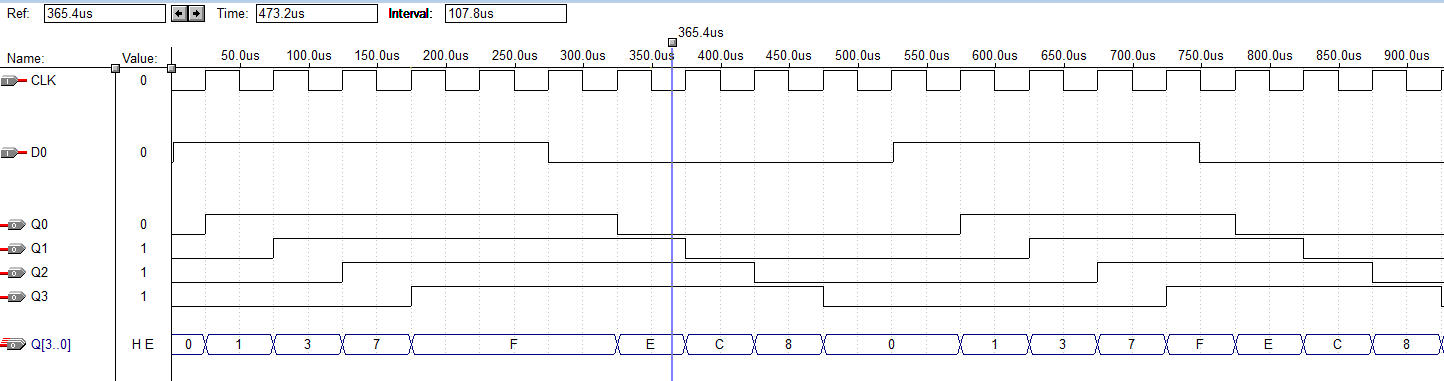

Кольцевой счетчик

Рис.8. Схема кольцевого счетчика

Рис.9. Тактовая диаграмма (выходная шина Q[3..0] продублирована для наглядности)

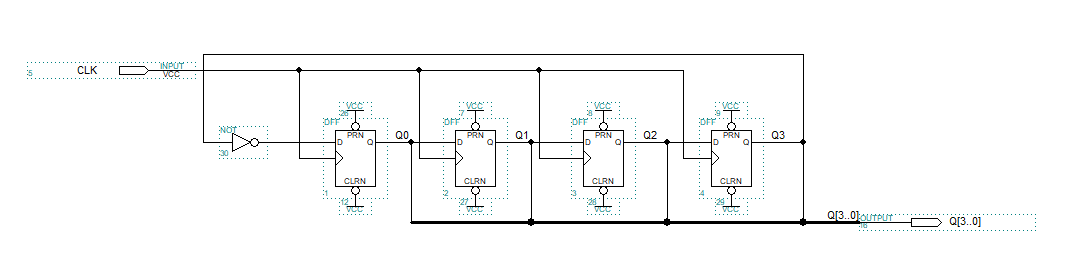

Сдвиговый регистр

Рис.10. Схема сдвигового регистра

Рис.11. Тактовая диаграмма (выходная шина Q[3..0] продублирована для наглядности)

Рис.12. Схема кольцевого сдвигового регистра

Рис.13. Тактовая диаграмма кольцевого сдвигового регистра

Выводы

В данной лабораторной работе были исследованы устройства последовательностной логики на триггерах, составлены их схемы и получены тактовые диаграммы.

Четырехразрядный параллельный регистр.

Принцип работы можно оценить по тактовой диаграмме. Со входа CLK подается тактовый сигнал на каждый триггер, а со входа D подаются либо логический ноль либо единица, таким образом формируется число в двоичном коде. На каждом такте регистр запоминает образовавшееся число со входов D и выдает его на выход Q. Пока не наступит следующий такт регистр не будет перезаписывать число.

Четырехразрядный асинхронный счетчик.

Особенность его схемы в том, что выход Q индексное объединяется со входом D, как это показано на схеме. По фронту тактового сигнала триггер будет выдавать логический уровень противоположный уровню до тактового сигнала. Сигнал с Q-инверсного предыдущего триггера поступает на тактовый вход следующего. На тактовый вход младшего триггера сигнал поступает со входа CLK. По первому такту на младший триггер приходит логическая единица, остальные остаются неизменны, т.е. получается 1000. По следующему такту младший триггер переходит в ноль, а следующий в единицу и в итоге мы получаем 0100. По тактовой диаграмме видно, что по следующим тактам далее будет 1100, потом 0010 и так далее. В итоге мы видим поочередна сменяющиеся числа.

Данный счетчик имеет существенный недостаток, в виде эффекта накопления задержки. Он происходит, если при переходе к следующему числу, достаточно изменить 1 бит. Данный эффект показан на рисунке 7. При переходе с числа F (1111) на число 0 (0000) возникают промежуточные числа, E (1110), С(1100), 8(1000) и только потом уже 0.

Кольцевой счетчик.

Тактовые входы кольцевого счетчика одновременно подключены к одному источнику. Выход Q с одного триггера идет на вход D следующего. С старшего триггера выход Q замыкается на вход D младшего.

Вход nRST сбрасывает старшие триггеры и устанавливает самый младший.

На первом такте на младший триггер подается единица, на остальных нули. Дальше эта единица переходит на следующий триггер, а на предыдущем устанавливается ноль. Таким образом единица проходит все триггеры и с последнего вновб возвращается на первый.

Сдвиговый регистр.

Выход Q предыдущего триггера подключается ко входу следующего.

На вход D младшего регистра подается сигнал из вне. Регистр с каждым последующим тактом начинает записывать эту единицу на остальные триггеры. Когда на вход D младшего триггера подается логический ноль, то происходит аналогичный процесс - на остальные триггеры с каждым тактом по очереди записывается логический ноль.

Также мы переделали схему данного регистра в кольцевой сдвиговый регистр. Как видно по тактовой диаграмме, отличие его лишь в том, что у нас теперь сигнал на вход D младшего триггера, который раньше поступал из вне, теперь поступает с выхода самого старшего триггера и в итоге теперь регистр сам перезаписывает свои уровни.