DgCXT_Lab_3

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ЭПУ

отчет

по лабораторной работе №3

по дисциплине «Цифровая схемотехника»

Тема: «Исследование схем триггеров»

Студентка гр. 7201 |

|

Семирякова А.А. |

Преподаватель |

|

Аристов С. А. |

Санкт-Петербург

2020

Цель работы: исследовать простейшие схемы RS-триггеры на ЛЭ, а также D-триггер с асинхронными входами сброса и установки типа 74HC(HCT)74.

Основные теоретические положения.

Триггер – простейшее устройство последовательностной логики. В отличие от комбинаторной логики уровни выходов зависят еще и от предыдущего состояния системы, имевшего место до последнего изменения уровней входов. Соответственно, последовательностные цифровые схемы имеют способность запоминать свое состояние. Простейшее устройство, способное хранить информацию – триггер: схема на ЛЭ или готовая микросхема, хранящая логический уровень, или один бит данных.

Простейший из триггеров, который можно построить на логических элементах – RS-триггер. Свое название он получил в соответствии с существующими у него входами управления: R (от англ. «reset», сброс) и S (от англ. «set», установка). В RS триггереах на ЛЭ ИЛИ-НЕ вход R называется входом сброса с активным высоким уровнем.

вход S является входом установки с активным высоким уровнем.

В

RS

триггерах на ЛЭ И-Не выходы сброса и

установки у такого RS-триггера имеют

низкий активный уровень, а запрещенной

комбинацией является, соответственно,

=

=

=0.

=0.

Помимо RS триггеров существуют:

JK-триггеры, которые выгодно отличаются от RS-триггеров отсутствием запрещенного состояния входов. Одновременная подача активных уровней на вход установки J и вход сброса K приводит к изменению состояния выхода такого триггера на противоположное.

T-триггеры (от англ. «toggle»). Логический переход на Т-входе (положительный или отрицательный фронт, в зависимости от модификации схемы или компонента) приводит к изменению состояния на противоположное. Фактически, Т-триггер – это JK-триггер, входы которого закорочены.

Триггеры с разрешением. Например, если объединить оба входа R и S схемы с дополнительным входом E через элементы И, то при Е = 0 триггер оказывается нечувствительным к изменениям состояний R и S, а при Е = 1 работает как обычно.

Отдельное внимание следует уделить синхронным триггерам. Термин «синхронный» применительно к триггерам означает, что у схемы или интегральной микросхемы существует отдельный тактовый вход, обычно обозначаемый как С. Все изменения состояния триггера происходят по логическому переходу уровня на тактовом входе, чаще всего – по фронту. сигнала на входе C, если о RS- или JK-триггере, то входы приобретают смысл разрешения установки или сброса триггера по фронту тактового сигнала.

Обработка результатов эксперимента

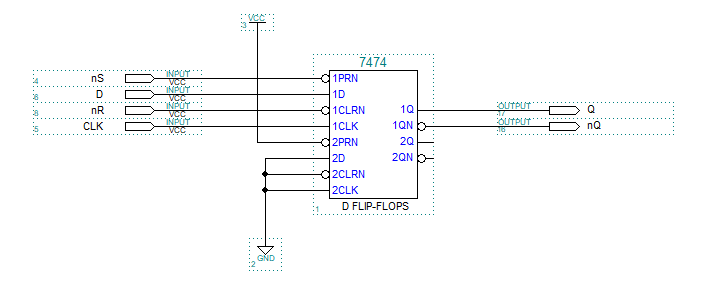

Исследование простейших RS-триггеров на ЛЭ 2ИЛИ-НЕ и 2И-НЕ.

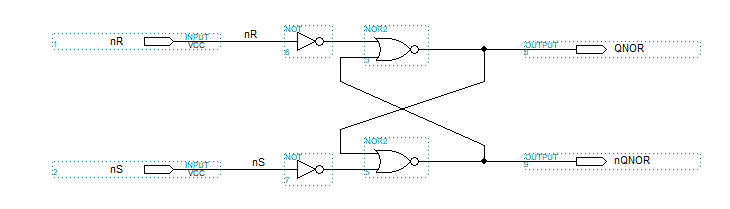

Рис.1 Схема RS-триггера на ЛЭ ИЛИ-НЕ.

Рис.2 Схема RS-триггера на ЛЭ И-НЕ.

Таблица 1 Переходы RS-триггера на ЛЭ 2ИЛИ-НЕ

№ |

Текущее состояние QNOR |

nS |

nR |

Новое состояние QNOR |

инверсное nQNOR |

1 |

0 |

0 |

1 |

0 |

1 |

2 |

0 |

1 |

1 |

0 |

1 |

3 |

0 |

1 |

0 |

1 |

0 |

4 |

1 |

1 |

1 |

1 |

0 |

5 |

1 |

0 |

0 |

0 |

0 |

6 |

0 |

0 |

1 |

0 |

1 |

7 |

0 |

0 |

0 |

0 |

0 |

8 |

0 |

1 |

0 |

1 |

0 |

9 |

1 |

1 |

1 |

1 |

0 |

Таблица 2 Переходы RS-триггера на ЛЭ 2И-НЕ

№ п.п. |

Текущее состояние QNAND |

nS |

nR |

Новое состояние QNAND |

инверсное nQNAND |

1 |

0 |

0 |

1 |

0 |

1 |

2 |

0 |

1 |

1 |

0 |

1 |

3 |

0 |

1 |

0 |

1 |

0 |

4 |

1 |

1 |

1 |

1 |

0 |

5 |

1 |

0 |

0 |

1 |

1 |

6 |

1 |

0 |

1 |

0 |

1 |

7 |

0 |

0 |

0 |

1 |

1 |

8 |

1 |

1 |

0 |

1 |

0 |

9 |

1 |

1 |

1 |

1 |

0 |

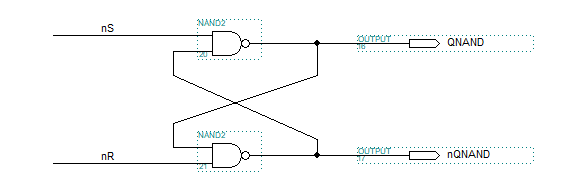

Тактовые диаграммы RS-триггеров на ЛЭ 2ИЛИ-НЕ и 2И-НЕ:

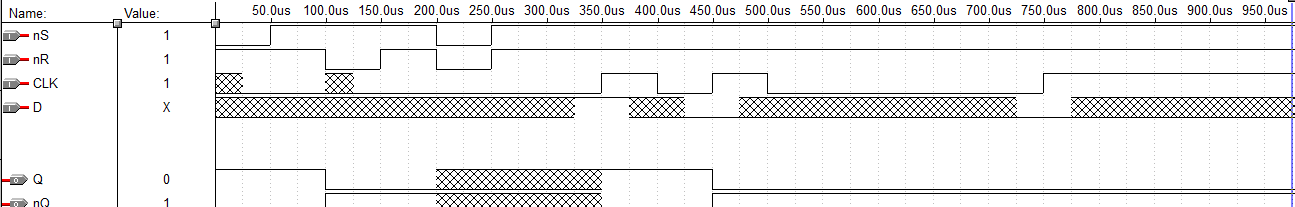

Рис.3 Тактовые диаграммы RS-триггеров на ЛЭ 2ИЛИ-НЕ и 2И-НЕ

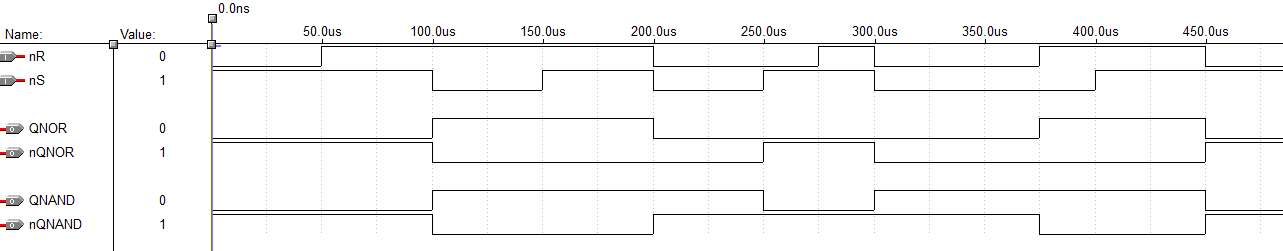

Исследование D-триггера с входами асинхронного сброса и установки.

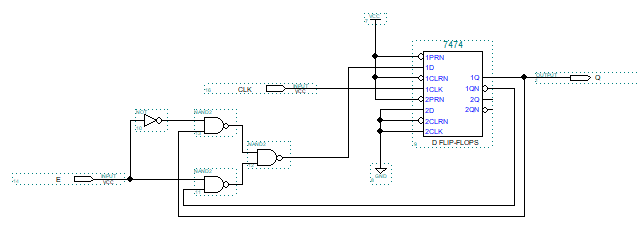

Рис.4 Схема D-триггера

Таблица 3 Переходы D триггера

nC |

nR |

C |

D |

Q |

nQ |

0 |

1 |

x |

x |

1 |

0 |

1 |

0 |

x |

x |

0 |

1 |

0 |

0 |

x |

x |

x |

x |

1 |

1 |

↑ |

1 |

1 |

0 |

1 |

1 |

↑ |

0 |

0 |

1 |

1 |

1 |

0 |

x |

0 |

1 |

1 |

1 |

1 |

x |

0 |

1 |

Тактовая диаграмма D триггера:

Рис.4 Тактовая диаграмма D триггера

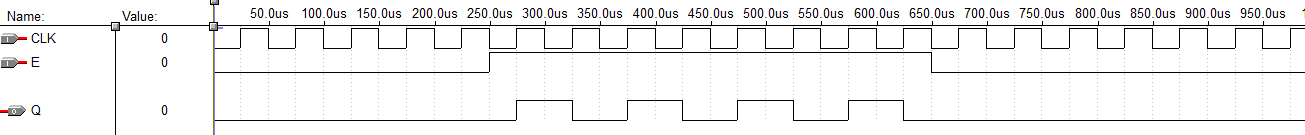

Исследование схемы счетного триггера на основе D-триггера.

Рис.5 Схема счетного триггера.

Тактовая диаграмма счётного триггера:

Рис.6 Тактовая диаграмма счётного триггера

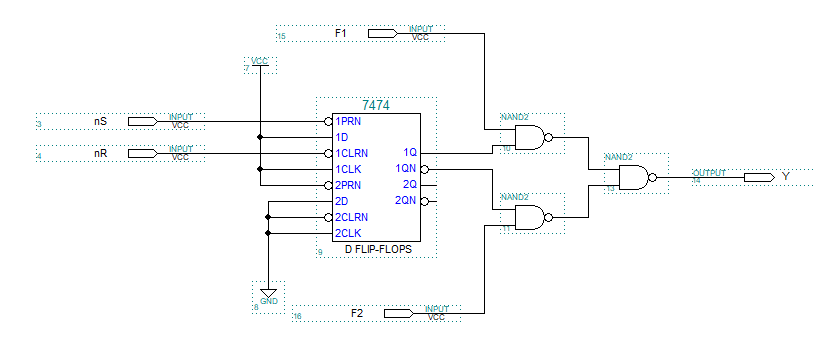

Исследование генератора сигнала с выбором частоты

Рис.7 Схема генератора с выбором одного из двух сигналов

Тактовая диаграмма генератора сигнала с выбором частоты:

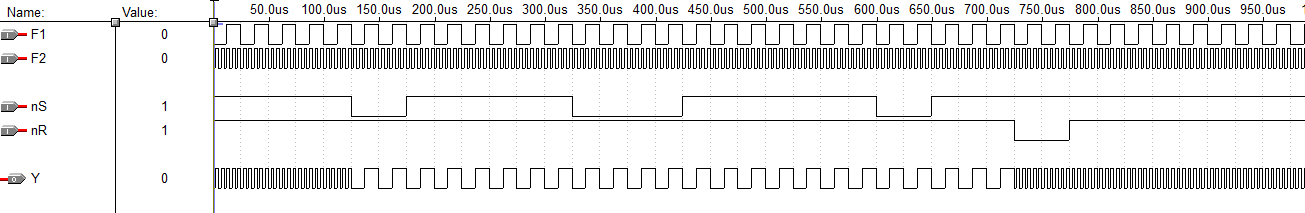

Рис.8 Тактовая диаграмма генератора сигнала с выбором частоты

Выводы:

В ходе выполнения лабораторной работы были исследованы простейшие схемы RS-триггеры на ЛЭ 2ИЛИ-НЕ и RS-триггеры на ЛЭ 2И-НЕ, построена тактовая диаграмма и заполнены таблицы переходов данных триггеров.

При подаче на вход сброса nR нуля – получаем 0 на обоих выходах (подразумевается выходы триггеров на ЛЭ 2ИЛИ-НЕ и 2И-НЕ) и , соответственно 1 на инверсных. Если же подать на вход установки nS активный 0 результат на прямых входах будет единица, соответственно на инверсных -0.

При подаче на входы nS и nR одновременно два активных уровня триггер переходит в метастабильное состояние (QNOR=nQNOR=0; QNAND=nQNAND=1). Это запрещённое состояние для RS триггеров.

Следующим был исследован D триггер, построена его тактовая диаграмма.

Независимо от того, что подается на входы D и CLK, логический 0 на входе nS устанавливает D-триггер в 1 на выходе.

Если подать аналогичного сигнал на вход сброса nR, то это приведет к сбросу триггера (на прямом выходе 0, на инверсном 1). Метастабильное состояние начинается, если подать на оба входа лог. 0.

Запись в память триггера осуществляется в момент формирования фронта сигнала на входе CLK. При фронте первого импульса тактового сигнала в триггер записывается 1 со входа D, при фронте второго – 0.

Также были исследованы схема счетного триггера на основе D-триггера и генератора сигнала с выбором частоты, построены их тактовые диаграммы. Счётный триггер игнорирует тактовые импульсы, пока на входе E установлено значение 0. При подаче на вход Е единицы на выходе Q триггер записывает значение, обратное тому, которое в нем хранится на данный момент.