ФУУМЭ / метода лабы

.pdf∙коэффициент объединения но входу m,

∙средняя задержка передачи сигнала τф ,

∙предельная рабочая частота,

∙помехоустойчивость,

∙потребляемая мощность.

По виду реализуемой функции логические ИС можно разделить на два класса. К первому классу относятся функциональные элементы одноступенчатой логики, реализующие функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. Ко второму классу относятся функциональные элементы двухступенчатой логики, реализующие более сложные функции: И-ИЛИ, И-ИЛИ-НЕ, И-ИЛИ-И и др.

Нагрузочная способность или коэффициент разветвления по выходу n определяет количество входов идентичных элементов (схем), которое может быть подключено к выходу каждого из них. При этом обеспечивается неискаженная передача двоичных символов 0 и 1 в цифровом устройстве по цепи при наличии дестабилизирующих факторов.

Коэффициент объединения по входу m характеризует максимальное число логических входов логического элемента, С увеличением параметра m расширяются логические возможности.

К динамическим параметрам логического элемента, определяющего его быстродействие, относятся:

τф1 − фронт формирования уровня логической единицы,

τф0 − фронт формирования уровня логического нуля,

τ10 − задержка переключения из состояния 1 в состояние 0, τ01 − задержка переключения из состояния 0 в состояние 1, τи − длительность импульса,

fр − рабочая частота. Определение этих параметров обеспечивается при срав-

нении сигналов на входе и выходе логического элемента.

Методику определения этих параметров можно пояснить с помощью рис. 6.4, где показаны входной и выходной импульсные сигналы и уровни отсчёта, соответствующие значениям 0,1 и 0,9 от амплитуды импульсов. Длительности фронтов импульсов определяются как интервалы времени между уровнями 0,1 и 0,9 от амплитуды импульсов. Задержки распространения определяются как интервалы между уровнями 0,5 фронтов входного и выходного сигналов.

41

Средняя задержка τф = (τ10 + τ01) / 2 служит усреднённым параметром быстродействия.

Различают статическую и динамическую помехоустойчивость. Статическая помехоустойчивость определяет значение напряжения, которое может быть подано на вход интегральной схемы относительно уровней 0 или 1, не вызывая ее ложного срабатывания, то есть переход из состояния 1 в состояние 0 или наоборот. Помехоустойчивость ИС определяют относительно уровней логического нуля (

Uп0 ) и логической единицы (U п1 ).

Эти параметры находят из анализа семейств передаточных характеристик (рис. 6.5), представляющих собой зависимости,

Uвых = f (U вх ) . Сначала находят точки А и

Вкак места соприкосновения касательных,

проведенных под углом 45° к верхним и нижним изгибам крайних кривых передаточных характеристик. Затем определяют значения помехоустойчивости.

Динамическая помехоустойчивость – помехоустойчивость в динамическом режиме – зависит от длительности, амплитуды и формы сигнала помехи, а также от уровня статической помехоустойчивости и скорости переключения базового функционального элемента.

Логические схемы также характеризуются средней потребляемой мощностью Pср = (P0 + P1) / 2 , где P1 – потребляемая мощность в состоянии «вклю-

чено», P0 – потребляемая мощность в состоянии «выключено». Кроме того, для некоторых схем необходим дополнительный учет потребляемой мощности в переходном состоянии, потому что во время перехода из одного состояния в другое резко возрастают токи в цепях питания и возрастет потребляемая мощность.

Помимо указанных параметров логические ИС характеризуются предельными значениями входных токов при низком уровне напряжения на входе

и Iвх1 при высоком, а также минимальным выходным напряжением U1вых

42

при логической единице на выходе и максимальным выходным напряжением

Uвых0 при логическом нуле на выходе.

Взависимости от используемых активных и пассивных элементов при схемотехнической реализации логические ИС подразделяются на

-резисторно-транзисторные ИС (РТЛ),

-диодно-транзисторные (ДТЛ),

-транзисторно-транзисторные (ТТЛ),

-инжекционные (ИЛ),

-эмиттерно-связанные (ЭСЛ),

-на МДП-транзисторах р- и n-типов (р-МОП, n-МОП),

-на дополняющих (комплементарных) МДП-транзисторах (К МОП).

Вработе исследуется двухступенчатая логическая схема ТТЛ. ТТЛ - схемы имеют определенные преимущества. Главное достоинство схем ТТЛ – лёгкая реализуемость в интегральном исполнении, особенно при использовании многоэмиттерных транзисторов, что резко сокращает количество активных и пассивных элементов.

6.2.Описание объекта исследования

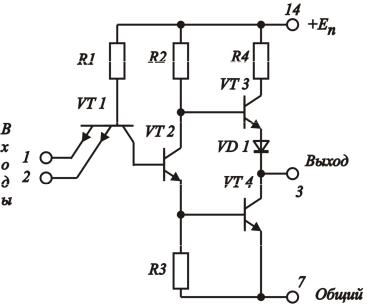

Вработе исследуется микросхема К155ЛА3, содержащая в своём составе четыре двухвходовых элемента, реализующих функцию 2И-НЕ. Принципиальная схема одного элемента приведена на рис. 6.6.

Схема работает следующим образом. При низких логических уровнях на

Рис. 6.6

43

обоих входах ИС (эмиттерах двухэмиттерного транзистора VT1) входные токи максимальны и ограничиваются в основном только сопротивлением в цепи базы двухэмиттерного транзистора R1. При этом входной транзистор VT1 насыщен и потенциал его коллектора, равный потенциалу базы следующего транзистора VT2, близок к потенциалу общей точки схемы – нулю. При этом транзистор VT2 закрывается, так как потенциал его базы не превышает потенциал его эмиттера. Это приводит к повышению потенциала базы верхнего выходного транзистора VT3, отпирая его, и к понижению практически до нуля потенциала базы нижнего выходного транзистора VT4, запирая его. При этом на выходе ИС напряжение высокого уровня. Отметим, что ИС работает таким же образом при подаче напряжения низкого логического уровня хотя бы на один из входов.

При подаче напряжений высокого уровня на оба входа переход эмиттербаза входного двухэмиттерного транзистора закрывается, его коллекторный переход переходит в режим прямого смещения и его коллекторный ток, являющийся базовым током транзистора VT2, резко увеличивается, открывая VT2. Это приводит к повышению потенциала базы нижнего выходного транзистора VT4, переводя его в режим насыщения, и к понижению потенциала базы верхнего выходного транзистора VT3. Управляющее напряжение база-эмиттер транзистора VT3 определяется разностью напряжения насыщения коллекторэмиттер транзистора VT2 и суммы двух напряжений – напряжения коллекторбаза насыщенного нижнего выходного транзистора VT4 и прямого падения напряжения на диоде VD1 в эмиттерной цепи верхнего выходного транзистора VT3. Сумма этих напряжений заведомо превышает напряжение насыщения коллектор-эмиттер предоконечного транзистора, что означает приложение между базой и эмиттером верхнего выходного транзистора VT3 нулевого или малого отрицательного напряжения, запирающего эмиттерный переход и сам транзистор. Таким образом, в рассматриваемых условиях верхний транзистор VT3 закрыт, нижний VT4 открыт и на выходе напряжение низкого логического

Iвх |

уровня. |

||||||

Входная характеристика ИС, изоб- |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

ражена на рис. 6.7. При малых уровнях |

|

|

|

|

|

|

|

входного сигнала, что соответствует за- |

|

|

|

|

|

|

|

||

|

|

|

Uвх.пред. Uвх. |

||||

|

|

|

пертому состоянию нижнего выходного |

||||

(E1-UБЭ)/R1 |

транзистора VT4, выходное напряжение |

||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

практически не меняется. С одновремен- |

|

|

|

|

|

|

|

ным увеличением входного напряжения |

|

|

Рис. 6.7 |

|

|

|

|

||

|

|

на обоих входах начинает открываться |

|||||

|

|

|

|

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

44 |

|

предоконечный транзистор VT2 и появляются токи, текущие через резисторы R2 и R3 в базовых цепях выходных транзисторов. Их сопротивления определяют наклон характеристики. При полном открывании предоконечного транзистора VT2 открывается нижний выходной транзистор VT4 и закрывается верхний VT3. Выходное напряжение ИС стабилизируется на уровне логического нуля. В процессе одновременного открывания нижнего и закрывания верхнего выходного транзисторов и наоборот имеется короткий промежуток времени, в течение которого открыты оба транзистора. При этом возникают так называемые сквозные токи, увеличивающие нагрузку на источник питания. Особенно их влияния существенно, когда микросхема работает в импульсном режиме при большой частоте следования импульсов с малой длительностью.

Рассмотрим входную характеристику микросхемы, представленную на рис. 6.7. При больших значениях U вх , превышающих напряжение на базе, входной транзистор VT1 находится в инверсном режиме. При этом наблюдается небольшой ток, втекающий в эмиттер. С уменьшением U вх входной транзистор переходит в режим насыщения и входной ток меняет направление – становится вытекающим (отрицательным на рис. 6.7) и растёт по абсолютной величине.

Для увеличения быстродействия микросхем ТТЛ применяются диоды Шоттки, имеющие малое прямое напряжение и высокое быстродействие. При подключении такого диода между базой и коллектором предоконечного транзистора VT2, диод будет отпираться раньше, чем коллекторный переход, и транзистор не перейдёт в режим глубокого насыщения, что приведёт к меньшему накоплению заряда в его базе и, следовательно, к повышению быстродействия.

6.3.Описание измерительной установки

Вработе исследуются параметры и характеристики логической интегральной микросхемы ТТЛ типа К155ЛА3. Блок-схема экспериментальной установки приведена на рис. 6.8. Она состоит из исследуемой интегральной схемы

DD1, источника напряжения её питания ИП2, измерителей тока питания Iпит. и нагрузки Iн., вольтметра V1 для измерения выходного напряжения ИС. Ключи K1

иK2 позволяют подавать на входы ИС напряжения низкого логического уровня, соединяя их с общей точкой схемы, или высокого при подключении к измерительной установке источника напряжения ИП1 с помощью K3. В другом положении ключа на входы ИС подаётся импульсное напряжение от генератора

45

прямоугольных импульсов G как показано на рис. 6.8. Для наблюдения формы и амплитуды входных и выходных импульсов ИС, а также – для проведения временных измерений, используется двухлучевой осциллограф.

Рис. 6.8

6.4.Программа работы и указания по её выполнению

1.Уяснить цель и задачи данной работы.

2.Ознакомиться с основными теоретическими положениями, описанием измерительной установки и объекта исследования.

3.Проверить выполнение логических операций исследуемой микросхемой. Для этого включить вольтметр V согласно инструкции по эксплуатации и источник ИП2, предварительно установив его выходное напряжение равным 5 В. Включить источник ИП1 и установить его выходное напряжение равным 5 В.

Ключом K3 подсоединить к измерительной установке вход ИП1. С помощью ключа K1 подать на вход 1 микросхемы напряжение высокого логического уровня (предварительно выставленное напряжение 5В на выходе ИП2). С по-

мощью K2 заземлить вход 2 ИС (низкий логический уровень напряжения). Убедиться, что на выходе наблюдается высокий логический уровень напряжения (с помощью вольтметра V).

4.Подать на вход 2 ИС высокий логический уровень с помощью ключа K2. Убедиться, что на выходе установилось напряжение, соответствующее низкому логическому уровню.

46

5. Снять передаточную характеристику ИС при напряжении её питания равном 5 В. Для этого подключить оба входа ИС к источнику ИП1 с помощью ключей K1, K2 и K3 (все три ключа в верхнем по схеме положении). Изменяя входное напряжение ИС с помощью ИП1 произвести измерения зависимостей входного тока Iвх., тока питания Iпит. и выходного напряжения Uвых от входного напряжения микросхемы U вх . Напряжение изменять от нуля до момента возрастания положительного (втекающего) тока входа ИС (правая часть зависимости на рис. 6.7 вблизи Uвх.пред.). Напряжение изменяется с шагом 0,1 В, при возникновении изменений любой из измеряемых величин – с шагом 0,01 В. После U вх = 5В шаг напряжения 1 В. Предельное значение U вх не должно превышать 9 В.

6.Повторить измерения при напряжении питания 4 В.

7.Снять нагрузочную характеристику при напряжении питания 5 в и высоком логическом уровне выходного напряжения. Для этого регулируя сопротивление R2 измерить не менее пяти значений выходного тока и соответствующих им значений выходных напряжений.

8.Повторить измерения нагрузочных характеристик при низком логичесом уровне выходного напряжения.

9.Определить динамические параметры микросхемы. Для этого ключами

K1, K2 и K3 подключить входы ИС к генератору прямоугольных импульсов G. Наблюдая входные и выходные импульсы ИС на экране двухлучевого осциллографа изменять амплитуду входного импульса от напряжения, при котором появляется импульс на выходе ИС, до 5 В с шагом 0,5 В. Измерить величины задержек τ10 и τ01 для каждого из входных напряжений.

6.5. Содержание отчёта

1.Цель работы.

2.Тип и параметры объекта исследования.

3.Электрическая принципиальная схема исследуемой микросхемы.

4.Схема измерительной установки.

5.Таблицы и графики результатов измерений входных токов, токов питания, выходных напряжения, нагрузочной и временных характеристик микросхемы.

6.Рассчитанные по передаточным характеристикам параметры помехо-

устойчивости Uп0 и Uп1. 7. Выводы по работе.

47

6.6.Контрольные вопросы

1.Назовите преимущества цифровой обработки информации.

2.Назовите основные параметры логических интегральных схем.

3.Укажите схемотехнические особенности исследуемой интегральной схемы, объясните её работу.

4.Укажите назначение основных узлов измерительной установки.

5.Объясните методику измерения динамических параметров и помехоустойчивости интегральных схем.

48

Список рекомендуемой литературы

Титце У., Шенк К. Полупроводниковая схемотехника / 12-е изд. Учебник- справочник-энциклопедия. Пер. с нем. – М.: ДМК Пресс, 2008.

Хоровиц П., Хилл Ч. Искусство схемотехники / Пер. с англ., 6-е изд. – М.: Мир, 2003.

49

СОДЕРЖАНИЕ

1.ИССЛЕДОВАНИЕ ИНТЕГРАЛЬНОГО ГИБРИДНО-ПЛЁНОЧНОГО УСИЛИТЕЛЯ НИЗКОЙ ЧАСТОТЫ……………………………..…..…..….. 3

1.1.Основные понятия, термины, определения……………………......... 3

1.2.Описание исследуемого усилителя………………………………...... 5

1.3.Описание лабораторной установки………………………...………... 7

1.4.Программа работы и указания по её выполнению………………….. 8

1.5.Содержание отчёта………………………………………………….… 9

1.6.Контрольные вопросы…………………………………………….….. 9

2.ИССЛЕДОВАНИЕ ИНТЕГРАЛЬНОГО МОНОЛИТНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ...…...……………...…………….......... 10

2.1.Основные теоретические положения..…..……..…….……..……….. 10

2.2.Описание исследуемого операционного усилителя ……………….. 12

2.3.Описание измерительной установки ………………………………... 14

2.4.Программа работы и указания по её выполнению..……..…….……. 15

2.5.Содержание отчёта……………………………………………………. 16

2.6.Контрольные вопросы…………………………………………….….. 17

3.ИССЛЕДОВАНИЕ ЦИРКУЛЯТОРА

НА ОПЕРАЦИОННЫХ УСИЛИТЕЛЯХ…………………………………… 17

3.1.Основные понятия теоретические положения..…..……..…….……. 17

3.2.Описание исследуемого циркулятора ………………………………. 21

3.3.Описание измерительной установки ………………………………... 21

3.4.Программа работы и порядок её выполнения……...……..…….…... 22

3.5.Содержание отчёта……………………………………………………. 23

3.6.Контрольные вопросы…………………………………………….….. 23

4.ИССЛЕДОВАНИЕ ГИРАТОРА НА ОПЕРАЦИОННЫХ

УСИЛИТЕЛЯХ………………………………………………………………... 24

4.1.Основные теоретические положения...……………………………… 24

4.2.Описание исследуемого гиратора...………………………………..… 28

4.3.Описание измерительной установки ………………………………... 29

4.4.Программа работы и указания по её выполнению..……..…….……. 30

4.5.Содержание отчёта...………………………………….….….….….…. 30

4.6.Контрольные вопросы....…………………………………….….….… 31

5.ИССЛЕДОВАНИЕ АКТИВНЫХ ФИЛЬТРОВ НА ИНТЕГРАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЯХ…………………………….…………... 31

50