рис. 24.3

15.8.2. Логические элементы на комплементарных МДП - транзисторах (КМДП)

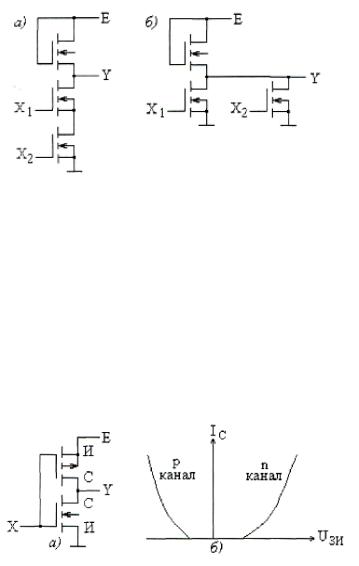

Ключ КМДП (рис. 15.14 а) состоит из пары транзисторов с различной проводимостью канала, при этом затворы p- канального и n-канального транзисторов соединены вместе.

рис. 15.14

В.А.Галочкин |

291 |

Схемотехника телекоммуникационных устройств |

На рис. 15.14 6) показаны характеристики прямой передачи транзисторов с индуцированным p-каналом и с индуцированным n-каналом.

Допустим, на вход подано положительное напряжение, превышающее пороговое. Тогда нижний транзистор открыт. Это же напряжение относительно общей шины приложено к затвору верхнего транзистора, но его исток соединен с плюсом источника питания, поэтому напряжение затвор-исток верхнего (p-канального) транзистора будет меньше порогового и верхний транзистор закрыт. На выходе будет очень низкое остаточное напряжение, т.е. Y = 0. Поскольку верхний транзистор закрыт, тока практически нет, энергия от источника питания не потребляется. Если X = 0, т.е. на входе низкое напряжение, то нижний (n- канальный) транзистор закрыт. На затворе верхнего (р- канального) транзистора будет большое отрицательное (относительно истока) напряжение, верхний транзистор открыт. Выходное напряжение почти равно напряжению питания Е, что соответствует состоянию логической единицы на выходе Y = 1.

Таким образом, ключ КМДП отлично справляется с ролью инвертора, размах логического сигнала почти равен напряжению питания, но при любом логическом состоянии ток равен нулю, ибо один из транзисторов закрыт.

Эта особенность схем КМДП - весьма малая потребляемая мощность - является большим достоинством по сравнению с ранее рассмотренными логическими элементами.

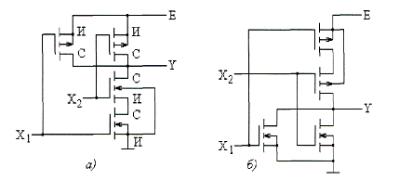

Для выполнения операции И-НЕ используется схема рис. 15.15 а), в которой несколько нижних n-канальных транзисторов соединяются последовательно, а такое же число верхних p-канальных – параллельно( табл.15.5).

Элемент ИЛИ-НЕ получается при параллельном соединении нижних и последовательном верхних транзисторов (рис. 15.15 6). В этом можно убедиться, рассматривая все

292 |

В.А.Галочкин |

Схемотехника телекоммуникационных устройств |

возможные комбинации входных логических сигналов (табл.15.6). Эти схемы сохраняют упомянутое преимущество ключей КМДП.

рис. 15.15

а) И-НЕ |

|

|

табл.15.5 |

||

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

верхний |

|

нижний |

0 |

0 |

1 |

(паралл.) |

|

закр. |

|

|

|

открыт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

верхний |

|

нижний |

1 |

1 |

0 |

закр. |

|

(посл.) |

|

|

|

|

|

откр. |

|

|

|

|

|

|

|

|

|

В.А.Галочкин |

293 |

Схемотехника телекоммуникационных устройств |

б) ИЛИ-НЕ |

табл.15.6 |

|

||

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

верхний |

нижний |

0 |

0 |

1 |

(посл.) |

закр |

|

|

|

открыт |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

верхний |

нижний |

1 |

1 |

0 |

закр. |

(паралл.) |

|

|

|

|

откр. |

|

|

|

|

|

|

|

|

15.8.3. Динамическая логика на МДП-транзисторах

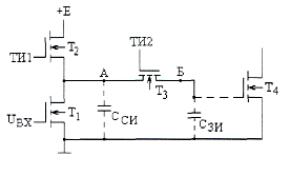

В схемах динамической логики на МДП-транзисторах (ДМДП) выходная емкость Сси логического транзистора и входная емкость Сзи следующего транзистора используются для хранения информации. Это возможно потому, что разряд емкости через большое входное сопротивление следующего МДП-транзистора происходит достаточно медленно. Схема инвертора ДМДП показана на рис.15.6.

|

рис. 15.6 |

294 |

В.А.Галочкин |

Схемотехника телекоммуникационных устройств |

На затворы Т2 и Т3 подаются последовательности тактовых импульсов, причем ТИ1 и ТИ2 сдвинуты по фазе. При наличии тактового импульса ТИ1 пара транзисторов Т1 и Т2 работает как обычный инвертор, т.е. в точке А будет либо небольшое остаточное напряжение, либо напряжение Ua E . В промежутке между импульсами ТИ1 транзистор Т2 закрыт, мощность от источника питания не потребляется, но соответствующий уровень напряжения в точке А сохраняется емкостью Сси.

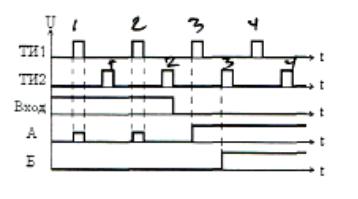

Некоторое различие уровней логического нуля при наличии или отсутствии импульса ТИ1 устраняется ключом Т3. При приходе импульса ТИ2 ключ открывается и на выходе, т.е. на емкости Сзи следующего логического элемента устанавливается напряжение U0 0, либо U1 E . Схемы ДМДП обеспечивают выигрыш в потребляемой мощности, определяемый скважностью импульсов. Работа схемы ДМДП иллюстрируется рисунком 15.7:

рис. 15.7

В.А.Галочкин |

295 |

Схемотехника телекоммуникационных устройств |

15.9. Сравнение параметров основных типов интегральных логических схем

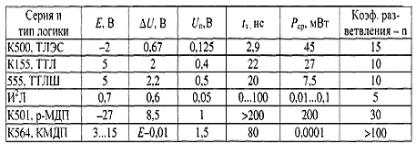

Каждый из рассмотренных типов логических схем имеет свои достоинства и недостатки. Обобщенным параметром является средняя работа переключения Aср Pср tз. При заданной работе переключения хорошее быстродействие связано с большой потребляемой мощностью и наоборот. Параметры некоторых серий цифровых ИС представлены в табл.15.7.

табл.15.7

Выводы по теме

1.Цифровыми интегральными схемами (ЦИС) называют микросхемы, работающие с цифровыми сигналами. Обычно используется двоичный код, т.е. сигнал может принимать одно из двух значений, условно называемых «0» или «1». Основа большинства ЦИС - транзисторный ключ.

2.Винформативной электроникеиспользуются такжеи ключи, имеющие другое назначение. Оно состоит в том, чтобы соединять или рассоединять источник входного, содержащего информацию аналогового сигнала и приемник этого сигнала. Та-

296 |

В.А.Галочкин |

Схемотехника телекоммуникационных устройств |

кие ключи принято называть аналоговыми. Их также называют аналоговымикоммутаторами.

3.Достоинство схем транзисторной логики с непосредственными связями (НСТЛ) - простота и хорошее быстродействие. Большим недостатком НСТЛ является то, что при небольшом разбросе входных характеристик транзисторов ток нагрузки распределяется неравномерно. Это снижает надежность работы таких схем.

4.Схема РТЛ (транзисторная логика с резистивной связью) отличается от НСТЛ только наличием резисторов в базовых цепях. В схемах РТЛ не сказывается разброс входных характеристик, но резко уменьшается быстродействие, так как увеличивается время нарастания. Нагрузочная способность этихсхем мала (п< 4). Эти недостатки привели к отказу от схем с коллек-

торной связью и в современных микросхемах они не применяются.

5.Размах логического сигнала в логических схемах ДТЛ практически не зависит от нагрузки, так как ток нагрузки втекает в коллектор через диоды последующей схемы. На-

грузочная способность ДТЛ n = 10, время задержки t3=10...15 нс. Недостаток – много диодов, которые занимают большую площадь на подложке.

6. Логические схемы ТТЛ принципиально не отличаются от схем ДТЛ. В качестве входных диодов используются эмиттерные переходы, а роль диода смещения выполняет коллекторный переход многоэмиттерного транзистора. Иногда используют транзисторы с диодом Шоттки, что заметно повышает быстродействие. Такие схемы сокращенно называют ТТЛШ.

Нагрузочная способность п > 10, время задержки t3 = 3... 10 нc. Схемы ТТЛ и ТТЛШ широко используются в микроэлектронике.

В.А.Галочкин |

297 |

Схемотехника телекоммуникационных устройств |

7.Схемы ЭСЛ обеспечивают малое время задержки t3 =0,7...З нс. На одном из выходов схемы выполняется логическая операция ИЛИ, а на другом - ИЛИ-НЕ.

8.Транзисторные логические элементы с инжекционным питанием (ТЛИП) называют также инжекционной интегральной логикой, откуда и возникло нелепое, но общепринятое сокращение И2 Л. Элементы ТЛИП в дискретном исполнении неизвестны, весьма специфичная схемотехника и технология ТЛИП реализуются в больших интегральных схемах (БИС). Достоинствами ТЛИП являются: низкое напряжение питания; малая потребляемая мощность; высокая плотность упаковки.

9.В цифровых ключах обычно используют МДПтранзисторы с индуцированным каналом. В последнее время полевые транзисторы все чаще используют в силовой импульсной электронике.

10.Ключи на полевых транзисторах отличаются малым остаточным напряжением. Они могут коммутировать слабые сигналы (в единицы микровольт и меньше).

11.Очень большое входное сопротивление ключей на полевых транзисторах фактически обеспечивает гальваническую развязку входных и выходных цепей. Это позволяет обойтись без трансформаторов в цепях управления.

12.Ключи на полевых транзисторах часто менее быстродействующие в сравнении с ключами на биполярных транзисторах.

13.Поскольку входной ток МДП-транзистора практически равен нулю, логические уровни логических элементов на МДП-транзисторах не зависят от нагрузки. Нагрузочная способность ограничивается только влиянием емкостей затвор-исток, т.е. уменьшением быстродействия.

298 |

В.А.Галочкин |

Схемотехника телекоммуникационных устройств |

14.Особенность схем КМДП - весьма малая потребляемая мощность - является большим достоинством по сравнению с ранее рассмотренными логическими элементами.

15.В схемах динамической логики на МДП-транзисторах (ДМДП) выходная емкость Сси логического транзистора и входная емкость Сзи следующего транзистора используются для хранения информации. Это возможно потому, что разряд емкости через большое входное сопротивление следующего МДП-транзистора происходит достаточно медленно. Схемы ДМДП обеспечивают выигрыш в потребляемой мощности, определяемый скважностью импульсов.

16.Каждый из рассмотренных типов логических схем имеет свои достоинства и недостатки. Обобщенным параметром является средняя работа переключения Aср Pср tз.

При заданной работе переключения хорошее быстродействие связано с большой потребляемой мощностью и наоборот.

Задания и вопросы для самоконтроля по теме

1.Объясните работу ключа на биполярном транзисторе как основного элемента цифровых схем.

2.Какую логическую операцию выполняет схема транзисторной логики с непосредственными связями (НСТЛ)? Объясните работу схемы.

3.Приведите отличия схемы РТЛ (транзисторная логика с резистивной связью) и особенности ее работы.

4.Какую логическую операцию выполняет схема ДТЛ? Приведите особенности ее работы.

5.ТТЛ (транзисторно-транзисторная логика). Приведите схему, ее достоинства и недостатки.

6.Какие логические операции выполняются эмиттерносвязанной логикой (ЭСЛ)? Приведите особенности работы схемы.

В.А.Галочкин |

299 |

Схемотехника телекоммуникационных устройств |

7.Логические элементы с инжекционным питанием (И2Л). Какие логические операции выполняются этой логикой? Приведите особенности работы схемы.

8.Логические элементы на МДП-транзисторах. Приведите особенности их работы.

9.Логические элементы на комплементарных МДП - транзисторах (КМДП). Приведите особенности их работы.

10.Приведите особенности схем динамической логики на МДП-транзисторах (ДМДП).

11.Приведите сравнение параметров основных типов интегральных логических схем.

300 |

В.А.Галочкин |

Схемотехника телекоммуникационных устройств |