- •Внешний генератор

- •Широтно-импульсная модуляция. Понятие широтно-импульсной модуляции. Различные режимы широтно-импульсной модуляции. Режим быстрый шим (Fast pwm). Шим без фазового сдвига (Phase Correct pwm).

- •3. Цифро-аналоговые преобразователи. Структурная схема цап. Параллельная схема суммирования токов. Последовательная схема суммирования токов.

- •Классификация ацп

- •5. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

- •3. Пара adch:adcl

5. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

Параметры АЦП (айтини13):

Только один встроенный 4-канальный АЦП с мультиплексором, который может переключать текущий канал. Один АЦП, но входов несколько, если хотим одновременно оцифровывать несколько входных сигналов, то просто переключаем каналы. При этом получается псевдосинхронное преобразование. Входы мультиплексора могут работать как по отдельности (в несимметричном режиме, измеряя напряжение относительно земли), так и объединяться в пары (только для некоторых моделей микроконтроллеров), измеряя дифференциальное напряжение. Также опционально возможно усиление входного сигнала с фиксированным коэффициентом 10 или 100.

Аналоговое напряжение могут считывать только те выводы, которые имеют метку «ADC» (у нас это с ADC0 до ADC3), а так их обычно от 4 до 16.

Встроенный источник опорного напряжения (в 13 он один, но может быть и несколько). В роли источника опорного напряжения может еще выступать напряжение питания мк.

Максимальное разрешение 10 бит (анисимов сказал, что он дохленький)

Максимальная частота дискретизации (количество тактов, которое ставится на одно АЦП преобразование) – до 1 МГц. Рекомендуемые цифры меньше сотни кГц на один канал.

Также возможно два режима преобразования: непрерывный (free-running mode), когда по завершении одного цикла преобразования сразу же следует другой, и одиночный (single), когда последовательность циклов регулируется вручную. Первый способ не отличается высокой точностью измерений и целесообразен только при необходимости максимальной скорости преобразований.

Рисунок 1 – Блок-схема встроенного АЦП.

Есть 10-битный ЦАП, компаратор (Sample&Hold comparator), устройство выборки и хранения совмещено с компаратором, входом управляет мультиплексор, который выбирает какой канал поступает на вход компаратора, в один момент работает 1 из 4 каналов. Выход компаратора идет на управляющую логику, включающую регистр последовательных преобразований. Результат поступает на двухбайтный регистр, двухбайтный, потому что состоит из двух частей ADCH и ADCL. Есть предделитель, который задает частоту преобразования, и управляющий регистр (ADC CTRL & STATUS…). Мультиплексор управляет источником опорного напряжения, который идет на ЦАП (или внутренний источник на 1.1 В или напряжение питания).

Предделитель

Входной сигнал идет не на прямую с основного тактового генератора, на котором работает мк. А как в таймерах через предделитель. На прямую не можем подавать, минимальный коэффициент деления 2, максимальный – 128. За это отвечают 3 бита в управляющем регистре, это будет дальше.

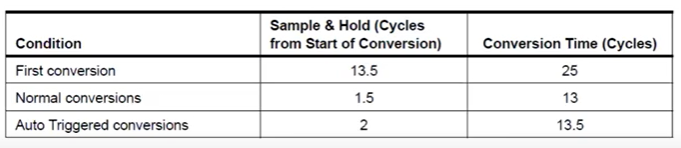

Для выполнения первого преобразования (при первоначальной настройке АЦП) требуется 25 тактов, последующие половину – 13 тактов (первое занимает больше времени из-за необходимости настройки каналов). Тактовая частота преобразования формируется с помощью делителя от опорной частоты микроконтроллера при помощи соответствующего управляющего регистра, рекомендованная частота преобразования – от 50 до 200кГц, в этом диапазоне наиболее вероятно получение наиболее достоверного результата измерения.

Время преобразования

Результат преобразования сохраняется в регистр ADC (ADCL, ADCH)

ADC = (VIN*1024)/VREF

(если 10 бит, Vref – источник опорного напряжения)

Управляющие регистры

ADMUX – управляет мультиплексором.

Мультиплексор управляет выбором источника опорного напряжения и выбором текущего канал откуда берем аналоговый сигнал. Также отвечает за режим хранения данных. В этом регистре нас больше всего интересуют биты, описанные далее.

6 бит – REFS1:0 (Reference Selection Bits) – определяют источник опорного напряжения, относительно которого будет происходить преобразование. Опорное напряжение должно быть как можно более стабильным, без помех и колебаний по напряжению – от этого во многом зависит точность работы АЦП. Все возможные варианты приведены в табл.7.1.

Таблица 7.1. Выбор источника опорного напряжения АЦП

REFS[1:0] |

Источник опорного напряжения |

00 |

Напряжение питания |

01 |

Внутренний ИОН на 1.1В |

10 |

Внутренний ИОН на 2.2В |

11 |

Внутренний ИОН на 4.3В |

Внутренний источник опорного напряжения не очень точный и подходит только для нетребовательных приложений.

MUX4:0 1:0 (Analog Channel and Gain Selection Bits) – данные биты определяют текущий вход (канал), с которого мы будем считывать аналоговый сигнал. Также с помощью этих битов выставляется коэффициент усиления при измерении в дифференциальном режиме. Возможные конфигурации для выбора текущего источника входного сигнала представлены в табл. 7.2.

Таблица 7.2. Выбор текущего канала АЦП

MUX4..0 1..0 |

Номер канала |

00000 |

ADC0 (PB5) |

00001 |

ADC1 (PB2) |

00010 |

ADC2 (PB4) |

00011 |

ADC3 (PB3) |

00100 |

ADC4 |

00101 |

ADC5 |

00110 |

ADC6 |

00111 |

ADC7 |

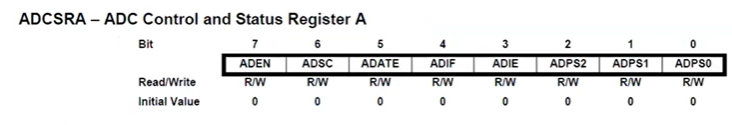

2. ADCSRA (ADC Control and Status Register A) – управляющий регистр, отвечающий за работу АЦП:

ADEN (ADC Enable) – записывая единицу в этот бит, разрешаем использование АЦП.

ADSC – отвечает за начало АЦП преобразования. ADSC (ADC Start Conversion) – записывая единицу в этот бит, мы начинаем очередной цикл преобразования в одиночном режиме работы (или первый цикл при непрерывном), который занимает 13 тактов (первый цикл – 25 тактов, здесь осуществляется первоначальная инициализация АЦП), при условии, что с помощью бита ADEN разрешено использование АЦП. Каждый раз надо ручками ставить 1, так как она сбрасывается после завершения АЦП преобразования.

ADATE (ADC Auto Trigger Enable) – возможность запуска преобразований от внешних источников, таймера и тп.

ADIF (ADC Interrupt Flag) – флаг прерывания по завершению преобразования, когда регистры данных обновились. Автоматически. (вроде как устанавливается в 1 по завершению цикла преобразования)

ADIE (ADC Interrupt Enable) – разрешение прерывания по завершению цикла преобразования.

ADPS2:0 (ADC Prescaler Select Bits) – позволяет выбрать коэффициент делителя тактовых импульсов для установки частоты преобразований (в непрерывном режиме). Значение коэффициента делителя определяется в соответствии с табл. 7.3.

Таблица 7.3. Выбор коэффициента деления

ADPS2 |

ADPS1 |

ADPS0 |

Коэффициент деления |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

4 |

0 |

1 |

1 |

8 |

1 |

0 |

0 |

16 |

1 |

0 |

1 |

32 |

1 |

1 |

0 |

64 |

1 |

1 |

1 |

128 |

ADFR (ADC Free Running Select) – записывая единицу в этот бит, выбираем непрерывный режим преобразования.