- •Внешний генератор

- •Широтно-импульсная модуляция. Понятие широтно-импульсной модуляции. Различные режимы широтно-импульсной модуляции. Режим быстрый шим (Fast pwm). Шим без фазового сдвига (Phase Correct pwm).

- •3. Цифро-аналоговые преобразователи. Структурная схема цап. Параллельная схема суммирования токов. Последовательная схема суммирования токов.

- •Классификация ацп

- •5. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

- •3. Пара adch:adcl

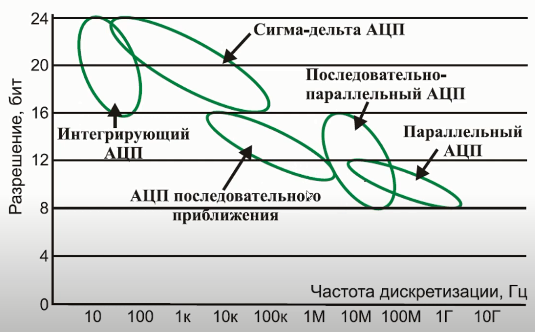

Классификация ацп

По основным параметрам |

Архитектура АЦП |

1. Разрядность 2. Частота преобразования 3. Точность преобразования |

1. Параллельного преобразования 2. Последовательного приближения 3. Двухтактного интегрирования 4. Сигма-дельта АЦП |

АЦП параллельного преобразования (схема и принцип работы, основные преимущества и недостатки)

Схема:

|

Принцип работы: Имеется матрица из компараторов в количестве 2n-1, где n – разряд На один вход подается аналоговый сигнал, на второй вход – опорное напряжение VREF. Это напряжение пропускается через делитель напряжения. На каждый из входов поступает своя часть напряжения в зависимости от текущего разряда. В зависимости от того, что поступает на вход компаратора, на выходе устанавливается: HIGH уровень – входное напряжение превышает опорное LOW уровень – входное напряжение ниже опорного

Дешифратор собирает все данные и преобразовывает в n-битный цифровой код |

+ Высокая скорость преобразования (т.к. сигнал поступает на все компараторы одновременно)

− Низкое разрешение (иначе нужно слишком много компараторов)

− Высокое энергопотребление (каждый компаратор потребляет ток)

# Применяются там, где не требуется аккумуляторного питания: осциллографы

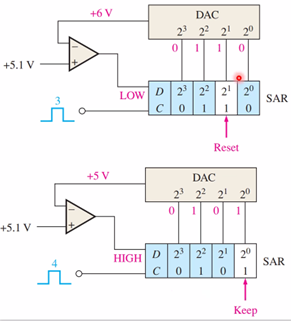

АЦП последовательного приближения (схема и принцип работы, основные преимущества и недостатки)

Схема:

Принцип работы:

Входной аналоговый сигнал поступает на УВХ (устройство выборки-хранения), чтобы зафиксировать данные, так как преобразование занимает время и на выходе могут измениться значения.

Далее сигнал поступает на компаратор, второй вход которого подключен к ЦАП. Компаратор управляет регистром ПП (регистр последовательного приближения), который составляет основу этого АЦП. Код с регистра ПП поступает на N-битный ЦАП и напряжение ЦАПа сравнивается с входным.

Как происходит преобразование?

В начальным момент времени регистр ПП сброшен в ноль. Далее устаналивается «1» в самом старшем разряде при первом такте, это как раз приходится на половину опорного напряжения. Компаратор на выходе указывает больше или меньше напряжение входного сигнала, чем выход ЦАП (на первом такте это половина опорного напряжения).

Выход ЦАП > входного сигнала => выход компаратора LOW => сброс бита в регистре

Выход ЦАП < входного сигнала => выход компаратора HIGH => 1бит сохраняется в регистре

Так перебираются все разряды.

Это из лекции Тимохова (тут объяснено лучше, что происходит)

|

ЦАП: VOUT = 8 В для 23 бит (СЗР) VOUT = 4 В для 22 бит VOUT = 2 В для 21 бит VOUT = 1 В для 20 бит (МЗР)

СЗР = 1: выходной сигнал ЦАП равен 8 В > входного сигнала 5,1 В => выходной сигнал компаратора LOW => СЗР в SAR сброшен до 0

22 бит = 1: выходной сигнал ЦАП равен 4 В < входного сигнала 5,1 В => выходной сигнал компаратора HIGH => 22 бит сохраняется в SAR |

|

|

21 бит = 1: выходной сигнал ЦАП 4+2=6 В > входного сигнала 5,1 В => выходной сигнал компаратора LOW => 21 бит в SAR сброшен до 0

20 бит = 1: выходной сигнал ЦАП 4+1=5 В < входного сигнала 5,1 В => выходной сигнал компаратора HIGH => 20 бит сохраняется в SAR

Двоичный код в регистре 0101~ значению 5,1В.

|

|

|

Алгоритм работы может быть объяснен на примере весов.

|

|

+ Простая архитектура при высоком разрешении

− Требует N сравнений для достижения N-разрядного разрешения (снижает fD и вызывает ограничение по скорости преобразования)

# Применяются во всех микроконтроллерах

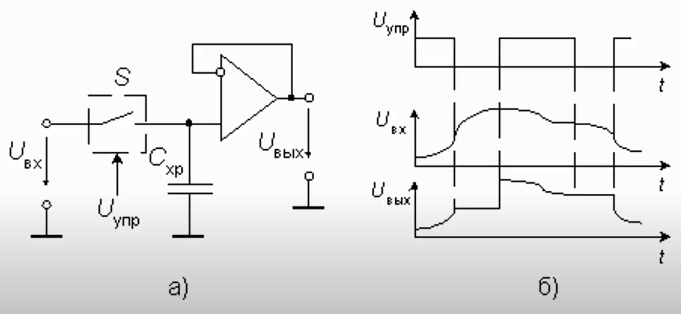

Устройство выборки-хранения (это было в лекции, может попадется и в контрольной)

Через ключ (полевой транзистор) и блок управления заряжаем С.

Пока ключ замнут, СХР заряжается до текущего входного значения. Далее ключ размыкаем, и значение фиксируется до тех пор, пока не завершится АЦП. Чтобы СХР не разряжался, подключаем через буфер на ОУ (мешает разряжаться из-за высокого сопротивления)

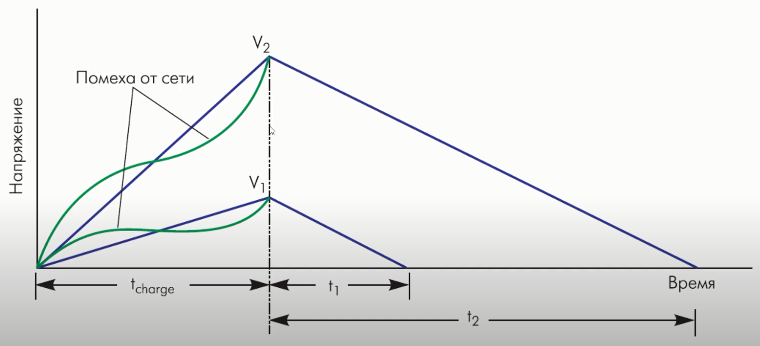

Интегрирующие АЦП (схема и принцип работы, основные преимущества и недостатки)

Схема:

Принцип работы:

На интегратор через ключ подаем входной сигнал.

В начальный момент времени S1 замыкается и заряжается С, далее размыкаем S1 и замыкаем S2, тем самым обеспечиваем разряд конденсатора.

После интегратора идет компаратор для того, чтобы узнать когда С разрядится до нуля. Счетчик считает время за которое разрядится С. Результат будет преобразован в выходной код АЦП (сколько импульсов укладывается во время разрядки).

ГТИ задает работу всей схемы

Время разрядки С будет зависеть от того, до какого уровня мы его заряжали.

Выходной код ~ сколько импульсов укладывается во время разрядки С

+ подавление высокочастотного шума и фиксированных низких частот

(50/60 Гц) – из-за интегрирования

− низкая входная пропускная способность

− ограничение fD

# применяются в измерительных приборах (мультиметры, вольтметры и прочее, там не нужна высокая частота дискретизации)

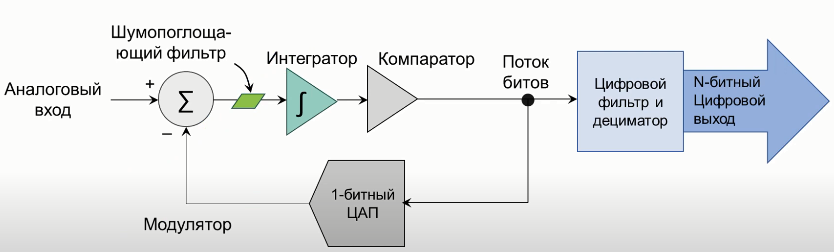

Сигма-дельта АЦП (схема и принцип работы, основные преимущества и недостатки)

Схема:

Принцип работы:

Входное напряжение суммируется с выходным сигналом ЦАП. Интегратор добавляет результат этого суммирования к значению, которое сохраняется с предыдущего шага.

Компаратор выдает «1» если выход интегратора больше нуля и «0» в противном случае.

1-битный ЦАП подает +VREF, если на выходе компаратора «1» и – VREF, если на выходе компаратора «0».

Работа зацикливается.

+ наибольшее разрешение

− медленные

Отношение «сигнал/шум» (SNR)

|

SNR – отношение среднеквадратического значения величины входного сигнала к среднеквадратическому значению величины шума. SNR(dB) = 20lg VSIGNAL(RMS) / VNOISE(RMS) |

Оверсэплинг – значительное повышение частоты дискретизации.

КПД – коэффициент передискретизация