1) Комбинационная логика, основные элементы (И, ИЛИ, НЕ), их схемы на КМОП транзисторах.

Комбинационная схема – логическая схема, сигнал на выходе которой определяется только уровнями сигналов на ее входах. Такой подход построения схем называется комбинационной логикой.

Логические элементы – устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого «1» и низкого «0» уровней).

Основные логические элементы

1) Вентиль И (AND)

|

|

Если хоть на одном входе «0», то на выходе – «0» |

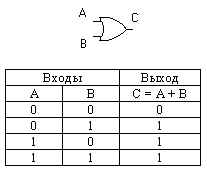

2)

Вентиль

ИЛИ (OR) |

|

Если хоть на одном вентиле «1», то на выходе – «1» |

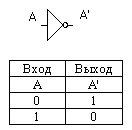

3) Вентиль НЕ (NOT) – инвертор |

|

Сейчас почти все строится с помощью инверторов. Если взять И-НЕ или ИЛИ-НЕ, то соединив входы получим инвертор |

Схемы на КМОП транзисторах

Повторение на тему ПОЛЕВЫЕ ТРАНЗИСТОРЫ

0 – блокирует n-канальный транзистор 1 – открывает n-канальный транзистор

(с р-канальным все наоборот) |

n-канальный – стрелка к затвору p-канальный – стрелка от затвора |

В основе ЛЭ на ПТ лежат инверторы (ключи). Рассмотрим логические элементы И-НЕ и ИЛИ-НЕ, а также инвертор.

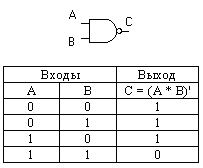

1) Вентиль И-НЕ (и + инвертор) на КМОП-транзисторах (NAND)

|

Пример: На входе А и В «1»: Tр1 –закрыт; Tр2 – закрыт; Tn1 –открыт; Tn2 – открыт, поэтому на выходе «0» Таблица истинности:

|

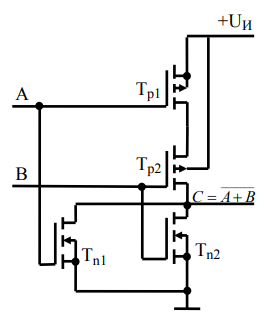

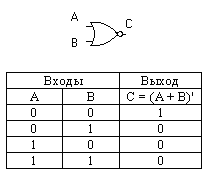

2) Вентиль ИЛИ-НЕ (или + инвертор) на КМОП-транзисторах (NOR)

|

Пример: На входе А и В «1»: Tр1 –закрыт; Tр2 – закрыт; Tn1 –открыт; Tn2 – открыт, поэтому на выходе «0» Таблица истинности:

|

3) Вентиль НЕ на КМОП-транзисторах

|

1. На входе «1», VT1 – закрыт; VT2 – открыт, поэтому на выходе «0»

2. На входе «0», VT1 – открыт; VT2 – закрыт, поэтому на выходе «1» |

Объянение как работает инвертор (картинка В и Г):

2) RS-триггер. Простейший триггер на биполярных транзисторах. RS-триггер на логических элементах И-НЕ, ИЛИ-НЕ. Синхронный RS триггер.

Триггер – устройство, обладающее способностью длительно находиться в одном из 2-х устойчивых состояний и чередовать их под воздействием внешних сигналов.

Свойство «запоминания» двоичной информации – способность оставаться в одном их 2-х состояний (помнит «1» или «0»)

При включении питания триггер непредсказуемо принимает одно из двух состояний.

Триггер на биполярных транзисторах

Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного.

Пусть в начальный момент времени VT2 закрыт. Под действием напряжения на его коллекторе через Rб3 протекает ток, удерживающий VT1 в открытом состоянии. В то же время открытый VT1 закорачивает базовую цепь транзистора VT2 с резистором Rб4. Закрытое состояние VT2 соответствует значению выхода Q=1.

Открытое

состояние

VT1

Напряжение на коллекторе закрытого транзистора (Q=1) равно: UQ=Uп×Rб3/(RК2+Rб3) |

Для того, чтобы сменить состояние триггера на противоположное, необходимо подать сигналы на вход R или S. Входные сигналы обычно являются импульсными. Наличие напряжения на входе S (S=1) устанавливает Q=1, а наличие напряжения на входе R (R=1) устанавливает Q=0. Одновременная подача сигнала на входы S и R запрещена, т.к. триггер при этом перестаёт быть триггером (не будет противоположного состояния Q и ). |

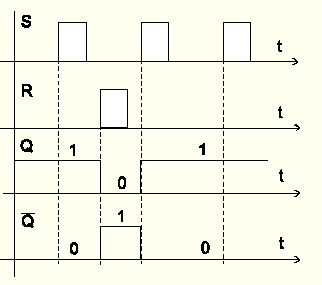

|

Диаграммы работы при наличии входных импульсных сигналов. На интервале между импульсами на входах S и R триггер помнит то состояние, в которое он был установлен по этим входам, т.е. триггер - элемент памяти. |

Триггер на логических элементах

RS триггер получил название по названию своих входов.

Вход S (Set –установка) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset – сброс) позволяет сбрасывать выход триггера Q в нулевое состояние (записывать ноль).

У триггера два выхода Q – прямой и – инверсный. Состояние триггера определяется состоянием прямого выхода.

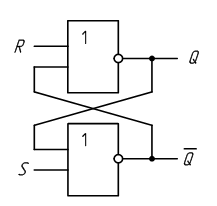

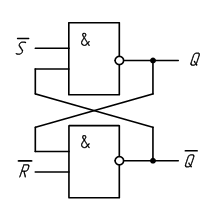

RS-триггер собирается на базе двух логических элементов: ИЛИ-НЕ и И-НЕ. Различие в том, что триггер на элементах И-НЕ переводится в другое состояние потенциалом логического нуля (активный уровень – низкий). Триггер, собранный на элементах ИЛИ-НЕ активируется логической единицей (активный уровень – высокий)

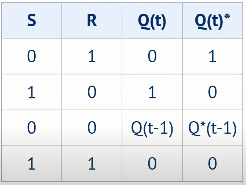

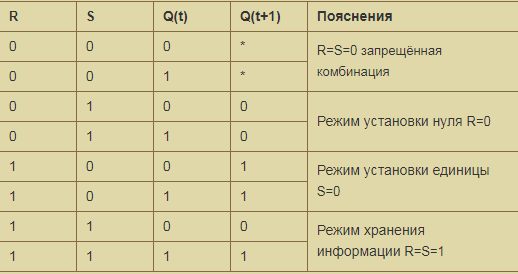

Для описания работы триггера используют таблицу состояний (переходов, истинности).

Опишем принцип работы RS-триггера, собранного на элементах ИЛИ-НЕ.

Если на R подаем активный уровень, то на выходе будет «0»

Если на S подаем активный уровень, то на выходе будет «1»

Состояние 0-0 – хранение предыдущего состояния Состояние 1-1 – неопределенность |

Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S); Q(t+1) – состояние триггера после изменения на входах R и S.

|

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. «1» на любом его входе приводит к тому, что на его выходе будет логический ноль =0. На выходе Q будет «1», т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии.

Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса.

Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

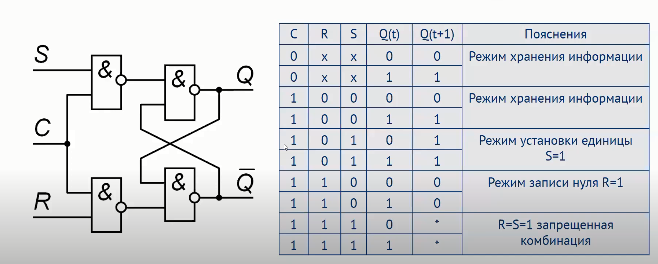

Опишем принцип работы RS-триггера, собранного на элементах И-НЕ.

Входы R и S инверсные (активный уровень "0"). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов "0". Комбинация R=S=0 является запрещённой.

Синхронный RS-триггер

Так как управляющие сигналы могут приходить как им вздумается, был предложен синхронный RS-триггер (добавлена схема синхронизации), т.е. переключение будет только если имеется синхронизированный сигнал.

=0.

=0.