- •Алгебра логики, алгебра Буля. Основные аксиомы.

- •Законы алгебры Буля. Дистрибутивный, коммутативный, ассоциативный.

- •Законы алгебры Буля. Поглощения, двойного отрицания, исключения.

- •Законы алгебры Буля. Де Моргана, идемпотентности.

- •Условное графическое обозначение логических элементов (стандарты).

- •Способы минимизации логических функций. Правило составления карты Карно.

- •Карта Карно для:

- •Для каждого контура выделяем области:

- •Способы минимизации логических функций. Правило составления диаграммы Вейча.

- •Комбинационная схема. Функция дешифратора.

- •Комбинационная схема. Функция шифратора.

- •Комбинационная схема. Функция мультиплексора.

- •Комбинационная схема. Функция демультиплексора.

- •Триггеры. Типы триггеров. Классификация Триггеров.

- •Регистры. Счетчики. Разновидность.

- •Архитектура Микроконтроллера. Структура типовой эвм.

- •Тактовая частота микроконтроллера. Изменения тактовой частоты.

- •Регистры общего назначения (рон) в микроконтроллерах.

- •Регистр признаков. Распиновка битов.

- •Регистры специального назначения. Регистр Программный счетчик.

- •Регистры специального назначения. Регистр указатель Стека.

- •Регистры специального назначения. Таймеры.

- •Регистры специального назначения. Ацп и цап.

- •Виды памяти в микроконтроллерах.

- •Преобразование последовательного кода в параллельный.

- •Преобразование параллельного кода в последовательный.

- •Язык Ассемблера. Синтаксис. Мнемокод.

- •Арифметические команды. Принцип работы.

- •Imul операнд_1[,операнд_2,операнд_3].

- •Логические команды. Принцип работы.

- •Команды вызова подпрограммы, особенности.

- •Команды переходов в программе, особенности.

- •Доказать следующие законы: дистрибутивный, поглощения.

- •1) Доказательство дистрибутивного закона

- •Доказательство закона поглощения

- •Доказать следующие законы: идемпотентности, двойного отрицания.

- •Доказательство закона идемпотентности

- •Доказательство закона двойного отрицания

- •Доказать следующий законы: исключения, коммутативный.

- •Минимизировать произвольную логическую функцию с помощью диаграмм Вейча. Каскадное подключение дешифраторов, увеличение разряда дешифратора на n.

- •Каскадное подключение демультиплексора, увеличение разряда демультиплексора на n.

- •Реализовать rs триггер на элементах или-не.

- •Реализовать rs триггер на элементах и-не.

- •Основные команды по работе с триггерами общего назначения. Основные команды по работе с триггером признаков. Назначение регистра pc. И принцип работы с ним.

- •Назначения регистра sp. И принцип работы с ним.

- •Назначения регистра watchdog. И принцип работы с ним.

- •Работа с Flash-памятью микроконтроллера.

- •Работа с eeprom памятью микроконтроллера. (https://cxem.Net/mc/book.Php )

Триггеры. Типы триггеров. Классификация Триггеров.

Триггер — простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации.

Различие триггеров по функциональным возможностям: с раздельной установкой состояния 0 и 1 (RS-триггеры); универсальные (JK-триггеры); с приемом информации по одному входу D (D-триггеры, или триггеры задержки); cо счетным входом Т (Т-триггеры). Входы триггеров обычно обозначают следующим образом:

S — вход для установки в состояние «1»; R — вход для установки в состояние «0»; J — вход для установки в состояние «1» в универсальном триггере; К — вход для установки в состояние «0» в универсальном триггере; Т — счетный (общий) вход; D — вход для установки в состояние «1» или в состояние «0»; V — дополнительный управляющий вход для разрешения приема информации. Классификация триггеров: по способу приема информации, по принципу построения и по функциональным возможностям.

Различают асинхронные и синхронные триггеры.

Асинхронный триггер — изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры — реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации C (от англ. clock). Этот вход также обозначают терминами «строб», «такт».

RS-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах, и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S выходное состояние становится равным логической единице. А при подаче единицы на вход R выходное состояние становится равным логическому нулю. *Запрещенное состояние: две единицы на входе, т.к. устройство утратит свойство триггера (если на информационные входы поданы переключающие сигналы 1, то на выходах появятся логические нули).

В JK-триггере при подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становиться равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещенных состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем.

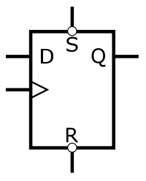

D-триггер

- запоминает состояние входа и выдает

его на выход. D-триггеры имеют, как

минимум, два входа: информационный D

и синхронизации С.

Сохранение информации в D-триггерах

происходит в момент прихода активного

фронта на вход С. Так как информация на

выходе остается неизменной до прихода

очередного импульса синхронизации,

D-триггер называют также триггером с

запоминанием информации.

Т-триггер по каждому такту изменяет свое логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счетным триггером.