Федеральное агенство связи

Ордена Трудового Красного Знамени федеральное государственное

бюджетное образовательное учреждение высшего образования

“Московский технический университет связи и информатики”

Кафедра “Информатика”

Лабораторная работа №7 по дисциплине “Математическая логика и теория алгоритмов (МЛиТА)”

по теме “Структурные схемы микропроцессорных устройств, таблица соответствия: понятие, её построение по имеющейся схеме устройства”

Выполнил студент

вариант №17

Проверил Сёмин В.Г.

г. Москва, 2020

Содержание

1 Ход выполнения лабораторной работы 3

Задание 1 3

Задание 2 6

Задание 3 8

Задание 4 9

Ход выполнения лабораторной работы Задание 1

Получить таблицу соответствия/истинности по заданной структурной схеме микропроцессорного устройства.

Исходная принципиальная схема микропроцессорного устройства представлена на рис. 1. Требуется сформировать таблицу истинности, описывающую процесс его функционирования.

Рисунок 1 - Схема микропроцессорного устройства для задания 1

Ход работы

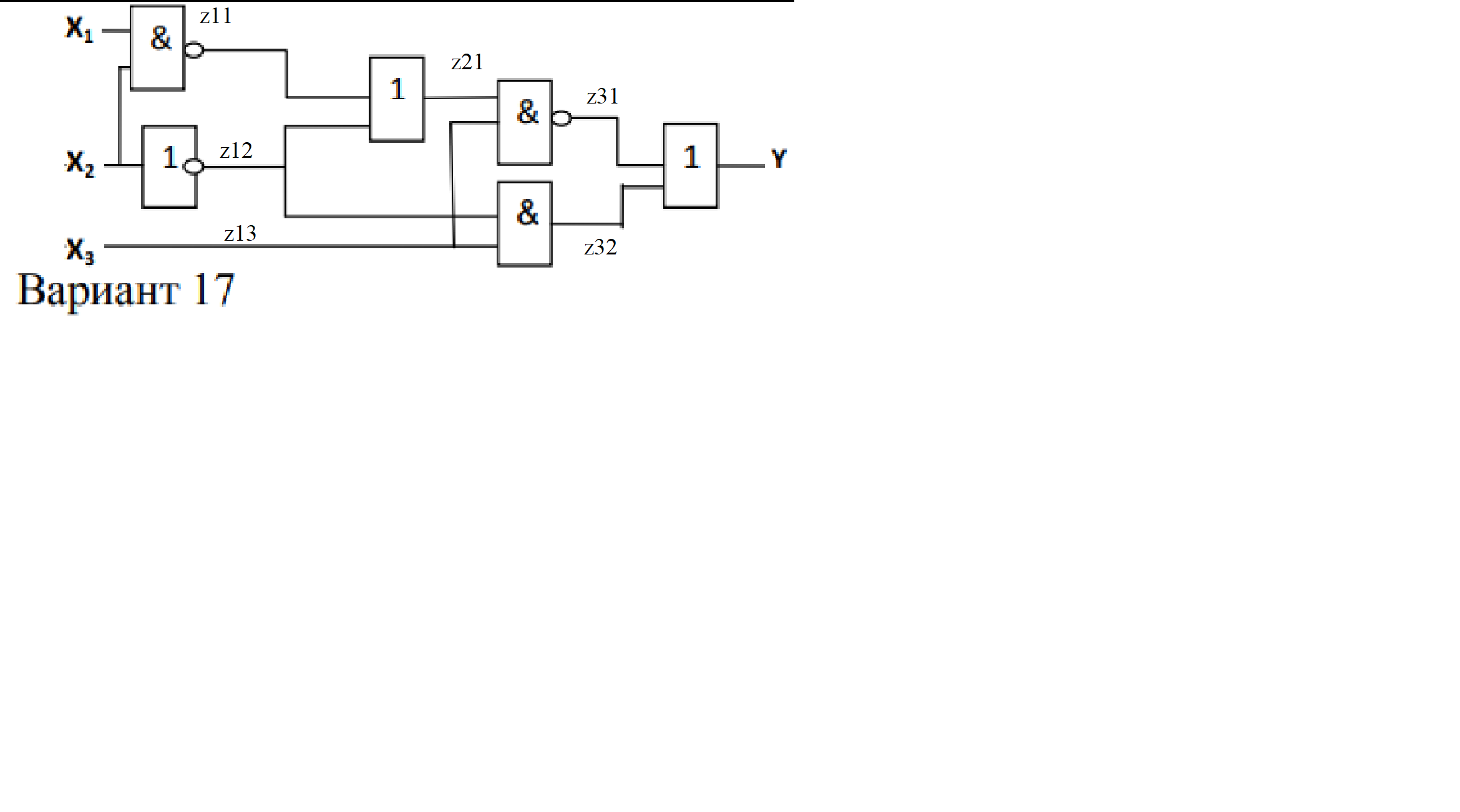

Анализ состава и структуры входных, выходных и промежуточных сигналов. Обозначим на исходной схеме промежуточные сигналы. Результат этих действий показан на рисунке 2.

Рисунок 2 – Схема с промежуточными значениями

Схема на рисунке

1 содержит логические элементы «НЕ»

( ),

выходные сигналы начальный значений

),

выходные сигналы начальный значений

и

и поступают на логический элемент “И-НЕ”

поступают на логический элемент “И-НЕ”

из которого сигналы z11

и z12

с элемента «НЕ» идут на логический

элемент “ИЛИ”(

из которого сигналы z11

и z12

с элемента «НЕ» идут на логический

элемент “ИЛИ”(

).

Также сигналы z12

и z13

подаются на логический элемент “И”(

).

Также сигналы z12

и z13

подаются на логический элемент “И”(

).Далее

сигналы z21

и z13

подаются на логический элемент “И-НЕ”(

).Далее

сигналы z21

и z13

подаются на логический элемент “И-НЕ”(

). После этого сигналы z31

и z32

подаются на логический элемент “ИЛИ”

(

). После этого сигналы z31

и z32

подаются на логический элемент “ИЛИ”

( )

)

Построение логической зависимости y = f(x1,x2,x3). В свою очередь функция y1 выглядит следующим образом:

Y = ( )

Построение пустой традиционной таблицы истинности, размерность которой определяется количеством выделенных входных и выходных сигналов, а затем - пустой расширенной таблицы, размерность которой определяется количеством сечений и промежуточных переменных в них. Результат выполнения данного этапа представлен в таблице 1.

Бланк таблицы для задания 1

№ комбинации входных сигналов

|

Входы |

Промежуточные сигналы по сечениям zij |

Выходы |

|||||||||||||||

|

|

|

Сечение 1 |

Сечение 2 |

Сечение 3 |

|

||||||||||||

|

|

|

z11z12 |

|

z12 z13 |

Y |

||||||||||||

z11 |

z12 |

z13 |

z21 |

z31 |

z32 |

z31 z32 |

||||||||||||

1 |

0 |

0 |

0 |

|

|

|

|

|

||||||||||

… |

|

|

|

|

|

|

|

|

||||||||||

8 |

1 |

1 |

1 |

|

|

|

|

|

||||||||||

Таблица 1

Заполнение указанной расширенной таблицы истинности по сечениям путем последовательного анализа результатов воздействия входных сигналов на рассматриваемое логическое устройство с последующим получением значений выходной величины для всех комбинаций входных. В таблицах 2, 3 и 4 представлено последовательное заполнение столбцов сечений и выходного столбца.

Заполнение сечения 1

№ комбинации входных сигналов

|

Входы |

Промежуточные сигналы по сечениям zij |

Выходы |

||||||||||

|

|

|

Сечение 1 |

Сечение 2 |

Сечение 3 |

|

|||||||

|

|

|

z11z12 |

|

z12 z13 |

Y |

|||||||

z11 |

z12 |

z13 |

z21 |

z31 |

z32 |

z31 z32 |

|||||||

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|||

2 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|||

3 |

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|||

4 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|||

5 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|||

6 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|||

7 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|||

8 |

1 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|||

Таблица 2

Заполнение сечения 2

№ комбинации входных сигналов

|

Входы |

Промежуточные сигналы по сечениям zij |

Выходы |

||||||||||

|

|

|

Сечение 1 |

Сечение 2 |

Сечение 3 |

|

|||||||

|

|

|

z11z12 |

|

z12 z13 |

Y |

|||||||

z11 |

z12 |

z13 |

z21 |

z31 |

z32 |

z31 z32 |

|||||||

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|||

2 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|||

3 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|||

4 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

|

|

|

|||

5 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|||

6 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|||

7 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|||

8 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|||

Таблица 3

Заполнение сечения 3 и выходного столбца

№ комбинации входных сигналов

|

Входы |

Промежуточные сигналы по сечениям zij |

Выходы |

||||||||||

|

|

|

Сечение 1 |

Сечение 2 |

Сечение 3 |

|

|||||||

|

|

|

z11z12 |

|

z12 z13 |

Y |

|||||||

z11 |

z12 |

z13 |

z21 |

z31 |

z32 |

z31 z32 |

|||||||

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|||

2 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|||

3 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|||

4 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|||

5 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|||

6 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|||

7 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|||

8 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|||

Таблица 4

По результатам заполнения расширенной таблицы истинности путем исключения из нее столбцов, соответствующих промежуточным сигналам, и ячеек, содержащих знаки логических операций, получаем итоговую таблицу истинности, описывающую процесс функционирования МП устройства, представленного на рисунке 1, в виде таблицы 5.

Итоговая таблица истинности

-

№ комбинации входов

Входы

Выходы y

Y

1

0

0

0

1

2

0

0

1

1

3

0

1

0

1

4

0

1

1

0

5

1

0

0

1

6

1

0

1

1

7

1

1

0

1

8

1

1

1

1

Таблица 5