Сраный верилог

.pdf

Учебное§ 4. Функциональныепособие модели устройств на языке Verilog на основе потоков данных |

125 |

|||

|

... |

|

|

|

|

|

|

|

|

|

end; |

|

|

|

|

always |

|

|

|

|

begin: block2 |

// блок block2 |

|

|

|

reg A; |

|

|

|

|

A = Ierarchic_Demo.block1.X; |

//Обращение к Х – |

|

|

|

|

|

//локальному сигналу |

|

|

|

|

//блока block1 |

|

|

end |

|

|

|

|

endmodule |

|

|

|

|

|

|

|

|

Вышеприведенный пример иллюстрирует формирование «длинных» имен с указанием модуля и именованного блока в соответствии со следующей формальной записью:

Имя_Модуля.Имя_Блока.Имя_Сигнала

Учебное§ 3. Синтезпособиеструктурных моделей цифровых устройств |

75 |

3.6. Упражнения

1.Опишите с использованием языка Verilog интерфейсную модель управляемого генератора синусоидальных колебаний. 10разрядные значения частоты и амплитуды колебаний задаются внешним источником, одноразрядный выход устройства используется для управления ключом. Кроме того, следует предусмотреть тактирующий вход и вход сброса (перезапуска) устройства.

76 |

Verilog-HDL для моделирования и синтеза цифровых электронных схем |

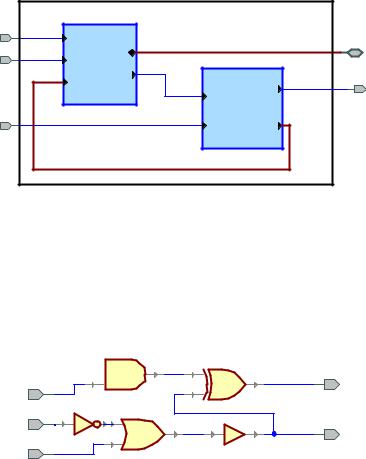

2.Опишите на языке Verilog интерфейсные модели показанных на схеме (рис. 3.14) модулей, а также реализуйте модуль верхнего уровня с включением модулей, описанных ранее. Обратите внимание на согласование типов сигналов при включении модулей. Повсюду, где это возможно, используйте тип сигнала reg.

Модуль_Верхнего_Уровня |

|

|

|

|

|

|

U1 |

|

|

|

|

X1 |

X1 |

|

|

|

Y0(7:0) |

X2 |

Y0(7:0) |

|

U2 |

|

|

X2 |

|

|

|

||

FB(7:0) |

FB(7:0) |

|

|

|

|

|

Data_Out |

|

|

|

|

|

|

NET00 |

NET00 |

Y1 |

Y1 |

|

|

|

|

|

|

|

Inner_Module_01 |

|

|

|

|

X3 |

|

|

X3 |

FB(7:0) |

|

|

|

|

Inner_Module_02 |

|

|

Рис. 3.14. Пример структурной схемы устройства

3.Опишите интерфейсную модель счетчика импульсов с настраиваемым числом разрядов выходного сигнала и временем срабатывания устройства. На вход счетчика подается сигнал подсчитываемых импульсов и сигнал сброса.

4.Используя логический уровень моделирования, опишите устройства, изображенные на рис. 3.15-3.17.

In0

In1 |

Out0 |

|

|

||

In2 |

Out1 |

|

In3 |

||

|

Рис. 3.15. Вариант А

Учебное§ 3. Синтезпособиеструктурных моделей цифровых устройств |

77 |

Sel |

|

In0 |

Out0 |

|

|

In1 |

Out1 |

|

|

Рис. 3.16. Вариант Б |

|

Sel |

|

In0 |

Out0 |

|

|

In1 |

Out1 |

|

|

|

Рис. 3.17. Вариант В |

5.Программы из предыдущего задания преобразуйте таким образом, чтобы описанные устройства обладали настраиваемыми временными характеристиками – задержками возрастания, спада и отключения сигнала для всех типов используемых стандартных логических модулей.

6.Для описанного в упражнении 3 настраиваимого счетчика импульсов разработайте испытательный стенд, включающий испытываемое устройство, генератор тестовых последовательностей и устройство для анализа выходов счетчика. Для перечисленных устройств приведите интерфейсные модели.

130 |

Verilog-HDL для моделирования и синтеза цифровых электронных схем |

4.5. Упражнения

1.На уровне потоков данных опишите на языке Verilog 8- разрядный сумматор с битом переполнения. Обеспечьте выравнивание выхода сумматора по спаду сигнала CLK.

2.На поведенческом уровне опишите языком Verilog 8-разрядный счетчик с входом сброса, срабатывающим по нарастанию входного сигнала.

3.Написать сценарий, генерирующий тестовую последовательность для сумматора, разработанного в упражнении 1. При этом на входы слагаемых следует подавать псевдослучайные числа, а на вход CLK – тактирующий сигнал с периодом, равным четырем интервалам времени срабатывания сумматора.

4.Написать сценарий, генерирующий тестовую последовательность для счетчика, разработанного в упражнении 2, при этом на вход CLK должен поступать тактирующий импульс со случайно изменяющейся частотой.