4

.docxФедеральное агентство связи

ордена Трудового Красного Знамени

Федеральное государственное

бюджетное образовательное учреждение высшего образования

Московский технический университет связи и информатики

Кафедра

«Математическая кибернетика и информационные технологии»

Лабораторная работа №4

«Сумматор»

Выполнила:

Студентка группы БСТ1904

Пантелеева Ксения

Проверил:

асс. каф. Джабраилов Х.А.

Оглавление

1 Цель работы 3

2 Ход работы 3

2.1 Принцип построения. Пример работы 3

Заключение 5

1 Цель работы

Изучить схемы сумматоров и принципы их работы, а именно - сделать трехразрядный последовательный двоичный сумматор, затем объяснить принципы его построения и работы

2 Ход работы

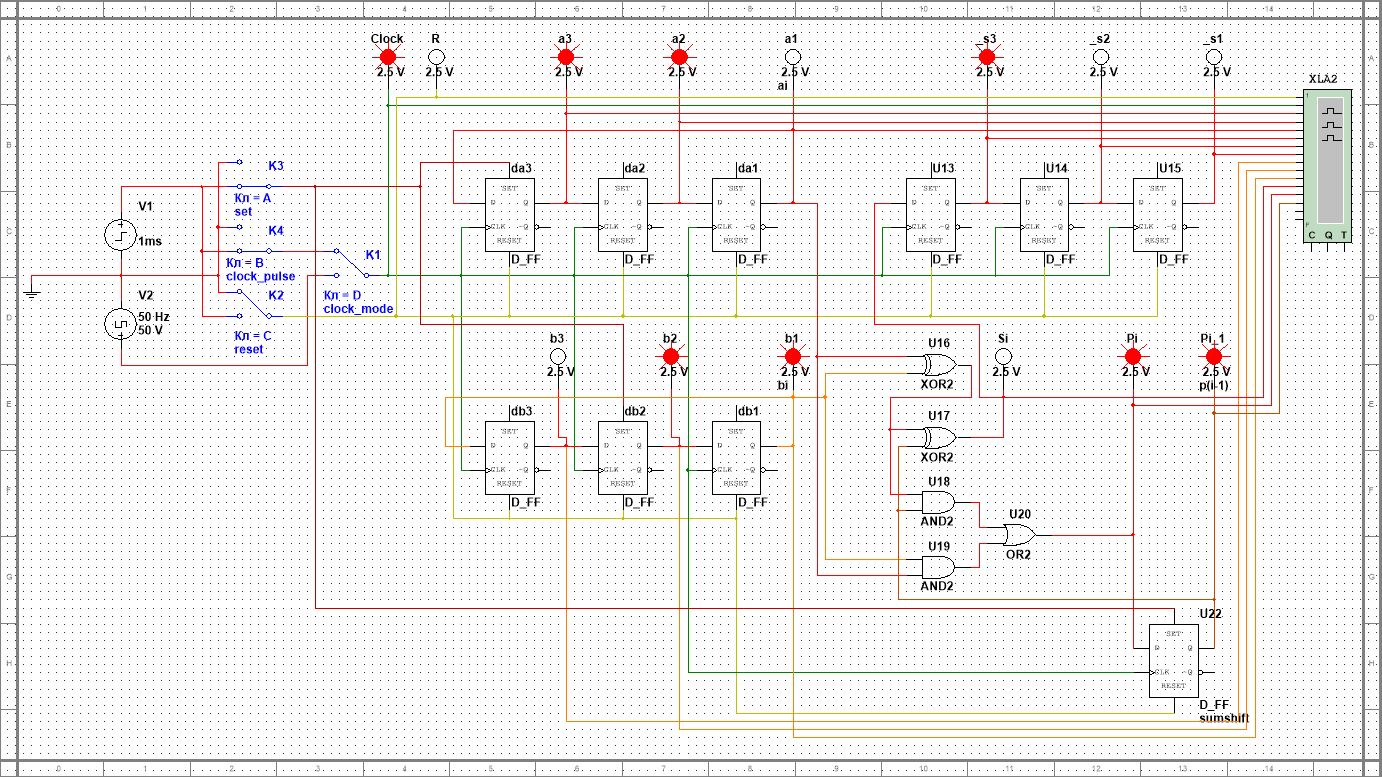

На рисунке 1 представлена схема трехразрядного последовательного двоичного сумматора.

Рисунок 1 - Трехразрядный последовательный двоичный сумматор

2.1 Принцип построения. Пример работы

Схема состоит из десяти D-триггеров (da1, da2, da3, db1, db2, db3, U13, U14, U15, U22), двух логических элементов AND (U18, U19), одного логического элемент NOR (U16) и двух логических элементов XOR (U16, U17), а также из одного логического элемента OR2 (U20), двухпозиционных переключателей, индикаторов и логического анализатора.

Прямой выход D-триггера поступает на логический элемент XOR. Сигнал, поступающий на вход «D» триггера U4, поступает на логический элемент AND. Логические элементы «И» подключены к логическому элементу «НЕ» через логический элемент NOR. Триггер задержки передачи U10 прямого входа подключен к лог. элементу.

Нумерация на концах ножек показывает каким-образом выходит сигнал. В зависимости от нумерации ножек так же зависят и ключи. С помощью SET-ов мы вводим числа.

Схема работы начинается с установки элементов в состояние лог. «0» Затем с помощью переключателя K2 сигнал от генератора одиночных импульсов поступает на входы установки триггеров для определения суммы чисел. Схема на рисунке 2 обеспечивает суммирование чисел 110 и 011. Синхроимпульсы могут подаваться либо с помощью GOI, либо с помощью генератора сигналов (FG). Выбор между FG и GOI осуществляется за счет переключателя K1. При подаче синхроимпульсов на входы CLK происходит поразрядное суммирование чисел.

Рисунок 2 – Сумма 110 и 011

Заключение

В ходе лабораторной работы удалось изучить схемы сумматоров и принципы их работы.