всё о микросхемах / Микросхемы для АЦП и мультимедиа

.pdf

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

|

|

|

AD677 |

|||||||||

ЭЛЕKТРИЧЕСKИЕ ПАРАМЕТРЫ ДЛЯ ПОСТОЯННОГО СИГНАЛА |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

||||||||

Параметр |

|

|

|

AD677J/A |

|

|

|

|

AD667K/B |

|

Единицы |

||

|

|

|

Ìèí. |

|

Òèï. |

|

Ìàêñ. |

|

|

Ìèí. |

Òèï. |

Ìàêñ. |

измерения |

|

|

|

ТЕМПЕРАТУРНЫЙ ДИАПАЗОН |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

Версии J, K |

|

0 |

|

— |

|

+70 |

|

|

0 |

— |

+70 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Версии A, B |

|

–40 |

|

— |

|

+85 |

|

|

–40 |

— |

+85 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ТОЧНОСТЬ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Разрешение |

|

|

16 |

|

— |

|

— |

|

16 |

— |

— |

Разряд |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ 83 kSPS, TMIN...TMAX |

— |

|

±1 |

|

— |

|

— |

±1 |

±1.5 |

ÌÇÐ |

|

Интегральная нелинейность (INL) |

|

@ 100 kSPS, +25°C |

— |

|

±1 |

|

— |

|

— |

±1 |

±1.5 |

ÌÇÐ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ 100 kSPS, TMIN...TMAX |

— |

|

±2 |

|

— |

|

— |

±2 |

— |

ÌÇÐ |

|

Дифференциальная нелинейность (DNL) |

|

|

16 |

|

|

|

|

16 |

|

|

Разряд |

||

– нет пропущенных кодов |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

Биполярная погрешность нуля2 |

|

— |

|

±2 |

|

±4 |

|

|

— |

±1 |

±3 |

ÌÇÐ |

|

Погрешности на положительном, |

|

@ 83 kSPS |

— |

|

±2 |

|

±4 |

|

|

— |

±1 |

±3 |

ÌÇÐ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ 100 kSPS, +25°C |

— |

|

±2 |

|

±4 |

|

|

— |

±1 |

±3 |

ÌÇÐ |

|

отрицательном концах шкалы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ 100 kSPS |

— |

|

±4 |

|

— |

|

— |

±4 |

— |

ÌÇÐ |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

ТЕМПЕРАТУРНЫЙ ДРЕЙФ3 |

|

|

|

|

|

|

||||

Биполярный ноль |

|

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

Положительный конец шкалы |

|

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

Отрицательный конец шкалы |

|

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Диапазон опорных напряжений4 |

|

5 |

|

— |

|

10 |

|

|

5 |

— |

10 |

|

|

|

|

|

|

АНАЛОГОВЫЙ ВХОД5 |

|

|

|

|

|

|

|

||

Входной диапазон (VIN) |

|

— |

|

— |

|

±VREF |

|

— |

— |

±VREF |

|

||

Входное сопротивление |

|

|

— |

|

X5 |

|

— |

|

— |

X5 |

— |

|

|

Время установки входа |

|

— |

|

2 |

|

— |

|

— |

2 |

— |

ìêñ |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

Входная емкость во время выборки |

— |

|

— |

|

505 |

|

|

— |

— |

505 |

ïÔ |

||

Апертурная задержка |

|

— |

|

6 |

|

— |

|

— |

6 |

— |

íñ |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

Апертурная неопределенность (неопределенность момента |

— |

|

100 |

|

— |

|

— |

100 |

— |

ïñ |

|||

выборки) |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ПИТАНИЕ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Режекция по напряжению |

|

VCC = +12 Â ± 5% |

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

|

|

VEE = –12 Â ± 5% |

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

||

6 |

|

|

|

|

|||||||||

питания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD = +5 Â ± 10% |

— |

|

±0.5 |

|

— |

|

— |

±0.5 |

— |

ÌÇÐ |

||

|

|

|

|

|

|||||||||

|

|

ICC |

— |

|

14.5 |

|

18 |

|

|

— |

14.5 |

18 |

ìÀ |

Рабочий ток VREF = +5 Â |

|

IEE |

— |

|

14.5 |

|

18 |

|

|

— |

14.5 |

18 |

–ìÀ |

|

|

IDD |

— |

|

3 |

|

5 |

|

|

— |

3 |

5 |

ìÀ |

|

|

VREF = +10 Â |

— |

|

360 |

|

480 |

|

|

— |

360 |

480 |

ìÂò |

Потребляемая мощность |

|

ICC |

— |

|

18 |

|

24 |

|

|

— |

18 |

24 |

ìÀ |

|

IEE |

— |

|

18 |

|

24 |

|

|

— |

18 |

24 |

–ìÀ |

|

|

|

|

|

|

|

||||||||

|

|

IDD |

— |

|

3 |

|

5 |

|

|

— |

3 |

5 |

ìÀ |

Потребляемая мощность |

|

— |

|

450 |

|

630 |

|

|

— |

450 |

630 |

ìÂò |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Примечания

1.VREF = 10.0 В, частота преобразований = 100 kSPS если не оговорено особо. Вс е значения получены после калибровки.

2.Приведенные значения применимы к любой температуре от T( мин.) до T(макс.) после калибровки при этой температуре при н оминальных напряжениях питания.

3.Приведенные значения получены после калибровки при +25°С без дополнительной калибровки при другой температуре. Пр иведенныеначенияз — типичные отклонения от значений при 25°С.

4.Рекомендуемая схема подачи опорного напряжения приведе на в разделе “Опорное напряжение”, динамические характер истики при других значениях опорного напряжения – см. Ðèñ. 11.

5.Рекомендуемая схема входного буфера см. раздел “Аналого вый вход”.

6.Типичные отклонения биполярного нуля, положительного и от рицательного концов шкалы.

ТИПОНОМИНАЛЫ

Модель |

Температурный диапазон |

S/(N + D) |

INL (ìàêñ.) |

Kорпус |

|

|

|

|

|

AD677JN |

0...+70°C |

89 äÁ |

Тип. только |

Пластмассовый 16-выводной DIP (N-16) |

|

|

|

|

|

AD677KN |

0...+70°C |

90 äÁ |

±1.5 ÌÇÐ |

Пластмассовый 16-выводной DIP (N-16) |

|

|

|

|

|

AD677JD |

0...+70°C |

89 äÁ |

Тип. только |

Kерамический 16-выводной DIP (D-16) |

|

|

|

|

|

AD677KD |

0...+70°C |

90 äÁ |

±1.5 ÌÇÐ |

Kерамический 16-выводной DIP (D-16) |

|

|

|

|

|

AD677JR |

0...+70°C |

89 äÁ |

Тип. только |

Пластмассовый 28-выводной DIP (R-28) |

|

|

|

|

|

AD677KR |

0...+70°C |

90 äÁ |

±1.5 ÌÇÐ |

Пластмассовый 28-выводной DIP (R-28) |

|

|

|

|

|

AD677AD |

–40...+85°C |

89 äÁ |

Тип. только |

Kерамический 16-выводной DIP (D-16) |

|

|

|

|

|

AD677BD |

–40...+85°C |

90 äÁ |

±1.5 ÌÇÐ |

Kерамический 16-выводной DIP (D-16) |

|

|

|

|

|

60 |

Публикуется с разрешения |

|

фирмы Analog Devices |

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

|

|

|

AD677 |

|||

ВРЕМЕННЫЕ ПАРАМЕТРЫ |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Символ |

Параметр |

|

Mèí. |

Tèï. |

Màêñ. |

Единицы |

|

|

измерения |

||||||

|

|

|

|

|

|

|

|

tC |

Период преобразования2,3 |

|

10 |

— |

1000 |

ìêñ |

|

|

|

|

|

|

|

|

|

tCLK |

Период тактового сигнала CLK4 |

|

480 |

— |

— |

íñ |

|

tCT |

Продолжительность калибровки |

|

— |

— |

85532 |

tCLK |

|

|

|

|

|

|

|

|

|

tS |

Длительность приема сигнала и выборки (длительность сигн ала SAMPLE) |

|

2 |

— |

— |

ìêñ |

|

tLCS |

Задержка от прихода последнего импульса CLK до заднего фрон та SAPLE (до следующей выборки) |

|

2.1 |

|

|

ìêñ |

|

tSL |

Время удерживания SAMPLE на низком уровне |

|

100 |

— |

— |

íñ |

|

|

|

|

|

|

|

|

|

tSB |

Задержка от SAMPLE до установки BUSY (занято) |

|

— |

30 |

75 |

íñ |

|

tFCD |

Задержка подачи 1–ого тактового периода CLK |

|

50 |

— |

— |

íñ |

|

|

|

|

|

|

|

|

|

tCL |

Длительность низкого полупериода тактового сигнала |

|

50 |

— |

— |

íñ |

|

tCH |

Длительность высокого полупериода тактового сигнала |

|

50 |

— |

— |

íñ |

|

tCB |

Задержка от прихода последнего тактового импульса CLK до сн ятия сигнала BUSY (занято) |

|

— |

180 |

300 |

íñ |

|

|

|

|

|

|

|

|

|

tCD |

От переднего фронта CLK до установки правильного значения р азряда данных на SDATA |

|

50 |

100 |

175 |

íñ |

|

tCSH |

От переднего фронта CLK до переднего SCLK |

|

100 |

180 |

300 |

íñ |

|

|

|

|

|

|

|

|

|

tSCL |

Длительность низкого уровня в периоде сигнала SCLK |

|

50 |

80 |

— |

íñ |

|

tDSH |

От установки разряд а данных на SDATA до переднего фронта SCLK |

|

50 |

80 |

— |

íñ |

|

|

|

|

|

|

|

|

|

tCALH |

Длительность высокого уровня сигнала калибровки CAL |

|

50 |

— |

— |

íñ |

|

tCALB |

Задержка от переднего фронта сигнала калибровки CAL до уста новки BUSY (занято) |

|

— |

15 |

50 |

íñ |

|

Примечания:

1.См. “Управление преобразованием” и “Автокалибровка” дл я подробных объяснений временных параметров.

2.Зависит от внешней тактовой частоты, включает время прие ма сигнала и время преобразования. Указанный максимальны й период преобразования отражает нежелательный разряд внутренних емкостей. При р аботе на более низких частотах характеристики могут ухуд шиться.

4.Рекомендуется период 580 нс для лучшей точности в рабочем д иапазоне температур (во время цикла калибровки необязате льно).

5.Если SAMPLE перейдет в 1 до прихода 17–го тактового импульса CLK, то ИС начнет прием сигнала примерно через 100 нс после переднего фронта 17–го импульса CLK.

6. tCH + tCL = tCLK и должно быть больше, чем 480 нс.

ОПИСАНИЕ ВЫВОДОВ

Номер |

Номер |

|

|

|

1 |

вывода |

вывода |

Мнемоника |

Òèï |

Описание |

|

â DIP |

â SOIC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Вход, управляющий приемом входного напряжения VIN. Активный ВЫСОКИЙ уровень. Во время преобразования SAMPLE управляет |

|

1 |

1 |

SAMPLE |

DI |

состоянием внутреннего усилителя выборки-хранения, и его задний фронт инициирует преобразование. Во время калибро вки на |

|

SAMPLE должен быть НИЗКИЙ уровень. Если во время калибровки SAMPLE = 1, то на выходе SDATA появит ся диагностическая |

|

||||

|

|

|

|

|

|

|

|

|

|

информация. |

|

|

|

|

|

|

|

2 |

2 |

CLK |

DI |

Вход главного тактового сигнала. Для выполнения преобраз ования AD677 нужно 17 тактовых импульсов. CLK используется также |

|

для получения сигнала SCLK. |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

3 |

3 |

SDATA |

DO |

Последовательный выход данных, управляемый SCLK. |

|

|

|

|

|

|

|

4 |

6, 7 |

DGND |

P |

”Цифровая” земля (для цифровой части ИС). |

|

|

|

|

|

|

|

5 |

8 |

VCC |

P |

Напряжение питания +12 В, для аналоговой части ИС. |

|

8 |

12 |

AGND |

P |

”Аналоговая” земля (для аналоговой части ИС). |

|

|

|

|

|

|

|

9 |

15 |

AGND SENSE |

AI |

”Чистая земля” для аналогового входного каскада. |

|

|

|

|

|

|

|

10 |

16 |

VIN |

AI |

Аналоговое входное напряжение |

|

11 |

17 |

VREF |

AI |

Вход внешнего опорного напряжения |

|

12 |

21 |

VEE |

P |

”Аналоговое” напряжение питания –12 В. |

|

13 |

22, 23 |

VDD |

P |

“Цифровое” напряжение питания +5 В. |

|

14 |

26 |

SCLK |

DO |

Выходной тактовый сигнал для чтения данных из ИС, получае тся из CLK. |

|

|

|

|

|

|

|

15 |

27 |

BUSY |

DO |

Выход статуса АЦП. Активный уровень – ВЫСОКИЙ, он указывает на выполнение преобразования или калибровк и. |

|

|

|

|

|

|

|

16 |

28 |

CAL |

DI |

Вход управления калибровкой. |

|

|

|

|

|

|

|

|

4, 5, 9, 10, |

|

|

|

|

6, 7 |

11, 13, 14, |

NC |

– |

Не подсоединено |

|

18, 19, 20, |

|

||||

|

|

|

|

|

|

|

24, 25 |

|

|

|

|

AI — Аналоговый вход

DI — Цифровой вход

DO — Цифровой выход

P — Питание

Публикуется с разрешения |

61 |

фирмы Analog Devices |

|

|

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD677 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

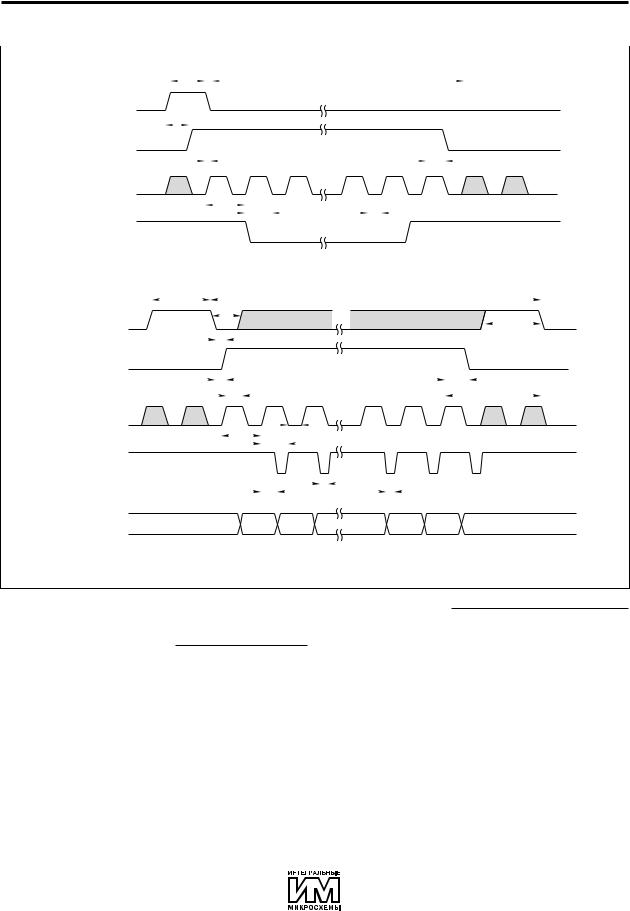

Рис. 1. Временная диаграмма калибровки. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Âõîä |

CAL |

|

|

|

|

tCALH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

tCALB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Выход |

BUSY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

CLK* |

|

|

|

|

|

|

|

|

|

|

|

|

tFCD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Âõîä |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

2 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85530 |

|

85531 |

|

|

85532 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

Выход |

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

tCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1602Z01 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

Рис. 2. Временная диаграмма преобразования. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

tS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

Âõîä SAMPLE* |

|

|

|

|

|

|

|

tSB |

|

|

tSL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tS |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Выход |

BUSY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tFCD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCB |

|

|

|

tLCS |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

CLK* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Âõîä |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

2 |

|

tCL 3 |

|

|

|

15 |

16 |

|

|

|

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Выход |

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCSH |

|

|

|

|

|

|

|

|

|

|

tSCL |

|

|

|

tDSH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Áèò 16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Áèò |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

Выход |

SDATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ÑÇÐ |

|

|

Áèò |

Áèò |

|

Áèò |

Áèò |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

(предыдущий) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

13 |

14 |

|

15 |

16 |

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1602Z02 |

||

* Заштрихованные части входных сигналов произвольны. Для достижения наилучших характеристик рекомендуется, чтоб ы эти сигналы имели НИЗКИЙ уровень в заштрихованных интервалах, если только явно не указан ВЫСОКИЙ уровень.

ПРЕДЕЛЬНО ДОПУСТИМЫЕ ЗНАЧЕНИЯ ПАРАМЕТРОВ И РЕЖИМОВ

VCC...VEE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3...+26.4 Â VDD...DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3...+7 Â VCC...AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3...+18 Â VEE...AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18...+0.3 Â AGND...DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±0.3 Â

Цифровые входы...DGND . . . . . . . . . . . . . . . . . . . . . . . . . . .0...+5.5 В

Аналоговые входы, VREF...AGND . . . . . . . . . .(VCC + 0.3)...(VEE – 0.3) В Температура при пайке (10 с) . . . . . . . . . . . . . . . . . . . . . . . . .+300°C

Температура хранения . . . . . . . . . . . . . . . . . . . . . . . . . .–65...+150°C

Значения, превышающие приведенные здесь цифры, могут вызв ать необратимые повреждения ИС. Эти цифры — только экстремаль ные оценки, и ни в коем случае не подразумевают работу ИС при этих или л юбых других значениях, превышающих номинальные. Воздействие этих мак симальных значений в течение длительного времени может ухудшить на дежность ИС.

ОПИСАНИЕ СХЕМЫ

AD677 — это многоцелевой 16-разрядный АЦП, который имеет схемы, реализующие функции выборки-хранения входного сиг нала, вход ”чистой земли” и автокалибровку. Эти функции разделены между двумя кристаллами — аналоговым процессором сигнал ов (А) и цифровым (D) контроллером. Оба кристалла размещены в одно м корпусе AD677.

Для определения величины аналогового входного напряжен ия AD677 использует метод последовательных приближений. Однако , во внутреннем ЦАП, вместо традиционной резистивной цепоч ки, откалиброванной при помощи лазера, эта ИС использует мето д перераспределения зарядов в массиве конденсаторов. Двоичновзвешенные конденсаторы делят входной отсчет и тем самым выполняют фактическое аналого-цифровое преобразование. Применение массива конденсаторов устраняет изменение линейности АЦП, вызванное несогласованностью сопротивлений резисторов вследствие изменений температуры. Так как для выполнения преобразования используется массив емкостей , то функция выборки-хранения выполняется естественным обра зом, нет необходимости подключать дополнительные внешние сх емы.

62 |

Публикуется с разрешения |

|

фирмы Analog Devices |

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

AD677 |

Начальные погрешности рассогласования емкостей устраняются внутренней схемой автокалибровки AD677. Эта схема использует расположенные на кристалле микроконтроллер и калиброво чный ЦАП для измерения и компенсации погрешностей рассогласования емкостей. По мере того, как определяется значение каждой погрешности, оно записывается во внутреннюю память (ОЗУ). При последующих преобразованиях эти значения из ОЗУ использ уются для улучшения точности преобразования. Программа автокалибровки может быть вызвана в любой момент. Автокалибровка обеспечивает высокое качество АЦП и устр аняет необходимость каких-либо подстроек со стороны пользоват еля, она подробно описана ниже.

Микроконтроллер управляет всеми внутренними схемами AD677. Он управляет собственно алгоритмом последовательных приближений, программой автокалибровки, операцией выбор ки - хранения и внутренним выходным регистром данных.

АВТОKАЛИБРОВKА

Паспортные характеристики AD677 достигаются посредством внутренней автокалибровки АЦП, без необходимости подстр ойки или регулировки со стороны пользователя.

В последовательности автокалибровки сначала смещение с хемы выборки-хранения корректируется путем внутреннего подк лючения входной схемы к цепи ”чистой земли”. Получающееся при это м напряжение смещения измеряется и сохраняется в ОЗУ для дальнейшего использования. Затем конденсатор, соответствующий старшему разряду, заряжается до опорного напряжения. Затем этот заряд переносится на конденсатор р авной емкости, составленный из суммы остальных разрядов с меньш им весом. Результирующее напряжение представляет величину несогласованности емкостей. Kалибровочный ЦАП добавляет соответствующее корректирующее напряжение, чтобы устра нить это рассогласование. Эта корректирующая величина также записывается в ОЗУ. Эта процедура повторяется для каждого из восьми остальных конденсаторов, представляющих старшие 9 разрядов. Записанные в ОЗУ величины используются затем в ходе последующих преобразований для соответствующей корректировки результатов преобразования.

Kак показано на Ðèñ. 1, когда CAL переводится в 1, внутренние схемы AD677 сбрасываются, вывод BUSY переводится в 1, и АЦП готовится к калибровке. Это асинхронный аппаратный сброс , который прерывает любые преобразования или калибровку, идущие в данный момент. Фактически калибровка начинается, когда CAL переводится в 0 и заканчивается через 85532 тактовых периода, на ее завершение указывает переход BUSY в 0. Во время калибровки предпочтительно, чтобы на SAMPLE был низкий уровень. Если же на SAMPLE будет 1, то на выход SDATA будет выводиться диагностическая информация. Пользователю эта информация не нужна.

В большинстве применений достаточно откалибровать AD677 только после включения питания, в этом случае нужно позаб отиться о том, чтобы напряжения питания и опорное напряжение успе ли стабилизироваться. Если калибровка не будет сделана, AD677 может или оказаться в неопределенном состоянии, или его точность может ухудшиться до 10 разрядов.

УПРАВЛЕНИЕ ПРЕОБРАЗОВАНИЕМ

AD677 управляется двумя сигналами: SAMPLE и CLK, как показано на Ðèñ. 2. Предполагается, что ИС уже была откалибрована, и что цифровые входы/выходы имеют уровни, показанные в начале временных диаграмм.

Преобразование состоит из приема входного сигнала, за кот орым следуют 17 тактовых импульсов, которые выполняют процедур у 16разрядного последовательного приближения. Аналоговый в ходной сигнал принимается путем установки на входе SAMPLE логическо й 1 в течение минимального времени выборки tS. Фактическим значением выборки будет напряжение на входе VIN через время одной апертурной задержки после перехода SAMPLE в 0, при условии, что предыдущее преобразование уже завершилось ( на что указывает переход BUSY в 0). В применениях, связанных с переменными сигналами, следует позаботиться о том, чтобы этот спадающий фронт был четко определенным и не было его дрожания, чтобы уменьшить неопределенность (шум) при прие ме сигнала. Kогда SAMPLE переходит в 0, начинается преобразование в AD677 — вход VIN отсоединяется от внутреннего массива конденсаторов, BUSY переходит в 1, и вход SAMPLE будет игнорироваться до тех пор, пока преобразование не заверши тся (когда BUSY перейдет в 0). На SAMPLE должен удерживаться низкий уровень в течение как минимум интервала tSL. Через интервал времени tFCD после перевода SAMPLE в 0 подаются 17 тактовых импульсов CLK; импульсы CLK, начинающиеся до этого момента игнорируются. Через время tSB после перехода SAMPLE в 0 на выходе BUSY устанавливается 1, что означает выполнение преобразования, высокий уровень на BUSY остается до тех пор, пока преобразование не завершится. Kак показано на Ðèñ. 2, выходные данные в двоичном дополнительном коде выводятс я начиная со старшего разряда. Эти данные могут быть считан ы или по передним фронтам SCLK или по задним фронтам CLK, начиная со второго импульса. AD677 игнорирует импульсы CLK после того, как BUSY переходит в 0, и выходы SDATA и SCLK не будут меняться до следующей выборки.

НЕПРЕРЫВНОЕ ПРЕОБРАЗОВАНИЕ

Максимальная производительность достигается, когда AD677 |

1 |

работает в режиме непрерывных преобразований. При этом |

|

используется тот факт, что после того как BUSY переходит в 0, |

сигнал SAMPLE уже не игнорируется, поэтому прием входного сигнала можно начать уже во время высокого уровня 17-го тактового импульса CLK, достигая тем самым максимальной частоты преобразований и предоставляя при этом достаточ ное время для полной установки схемы выборки-хранения. Если в момент прихода переднего фронта 17-го импульса CLK на вход SAMPLE уже подан высокий уровень, то прием сигнала начнется примерно через 100 нс после переднего фронта 17-го тактового импульса.

Следует позаботиться о том, чтобы были выполнены максимальные/минимальные временные ограничения, чтобы точность преобразования была сохранена.

ОБЩИЕ ЗАМЕЧАНИЯ

Во время приема сигнала и преобразования нужно обращать особое внимание на логические входы, чтобы избежать проникновения цифрового шума. В принципе, возможен непрерывный сигнал CLK, даже во время приема входного сигнал а. Однако, фронты CLK во время интервала выборки, и особенно в момент перехода SAMPLE в 0, могут внести шум в процесс выборки. AD677 тестируется без импульсов CLK во время выборки. Можно использовать сигнал BUSY, чтобы остановить тактовый сигнал во время выборки, как показано на Ðèñ. 3. В этой схеме BUSY используется для сброса схемы, которая делит системный тактовый сигнал для получения тактового сигнала CLK AD677. При этом тактовый сигнал останавливается до того момента, когда BUSY перейдет в 1, т.е. до того момента, когда выборка уже будет

Публикуется с разрешения |

63 |

фирмы Analog Devices |

|

|

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

|

|

|

AD677 |

|

|||||||||||||||||

|

сделана. Kогда преобразование завершается и BUSY переходит в 0, |

Таблица 1. Формат сигнала на последовательном выходе |

|||||||||||||||||||||

|

схема Ðèñ. 3 обрезает 17-й импульс CLK по длине, что однако |

|

|

|

|

|

|

||||||||||||||||

|

|

VIN |

|

|

Выходной код (Twos Complement) |

|

|||||||||||||||||

|

допустимо, так как нужен только его передний фронт. |

< Полная шкала |

|

|

|

|

011...11 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Полная шкала |

|

|

|

|

011...11 |

|

|

|

Íà Ðèñ. 3 показано также использование счетчика (74HC393) для |

|

|

|

|

|

|

|

|||||||||||||||

|

Полная шкала – 1 МЗР |

|

|

|

011...10 |

|

|

||||||||||||||||

|

получения импульса SAMPLE AD677 из системного тактового |

|

|

|

|

|

|

|

|

||||||||||||||

|

Середина шкалы + 1 МЗР |

|

|

|

000...01 |

|

|

||||||||||||||||

|

сигнала, когда нужен режим непрерывных преобразований. При |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

Середина шкалы |

|

|

|

|

000...00 |

|

|

|||||||||||||||

|

использовании вывода 9 (2QC) и системного тактового сигнала |

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

Середина щкалы – 1 МЗР |

|

|

|

111...11 |

|

|

||||||||||||||||

|

12.288 МГц частота дискретизации AD677 будет 96 кГц. Можно |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

–Полная шкала + 1 МЗР |

|

|

|

100...01 |

|

|

||||||||||||||||

|

использовать вывод 8 (2QD), что дает частоту дискретизации 48 кГц. |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–Полная шкала |

|

|

|

|

100...00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<–Полная шкала |

|

|

|

|

100...00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

Рис. 3. Схема получения сигнала SAMPLE из тактовых |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

импульсов |

|

ПИТАНИЕ И РАЗВЯЗKИ |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD677 имеет три вывода для подключения питания. Выводы VCC è VEE |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

11 |

3Q |

2Q |

7 |

|

|

|

|

|

служат для запитывания |

аналоговой |

части AD677, |

включая |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

4 |

|

|

12 |

|

|

|

|

|

емкостный ЦАП, входные буферы и компаратор. Через вывод VDD |

|||||||||

|

|

|

|

|

1D |

3D |

|

|

|

|

|

запитывается цифровая часть AD677, включая выходные буферы |

|||||||||||

|

12.288 ÌÃö |

|

|

|

9 |

|

|

1 |

|

|

|

|

|

данных и контроллер автокалибровки. |

|

|

|

||||||

|

Системный |

|

|

|

CLK |

CLR |

|

BUSY |

|

|

|

|

|

|

|||||||||

|

тактовый |

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

сигнал |

|

|

|

|

|

|

|

1Q |

|

CLK |

|

|

|

Kак и в большинстве прецизионных линейных схем, изменения в |

||||||||

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

2D |

|

|

|

|

|

напряжениях питания могут вызвать нежелательные измене ния |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

характеристик |

ÈÑ. |

Следует |

использовать |

хорошо |

|

|||

|

|

|

|

|

|

|

|

74HC175 |

|

|

AD677 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

стабилизированные источники питания с пульсациями мене е 1%. |

||||||||||

|

|

|

|

|

1 |

|

|

9 |

|

|

|

|

|

Выходной импеданс источника питания по переменному току |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

1CLK |

2QC |

|

SAMPLE |

|

|

|

сложным образом зависит от частоты, и в общем |

случае |

|

|||||||||

|

|

|

|

|

13 |

8 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

2CLK |

2QD |

|

|

|

|

|

увеличивается с частотой. Другими словами, высокочастотн ые |

|||||||||||

|

|

|

|

|

6 |

|

|

|

|

A1602P01 |

переключения, |

такие как |

переключения в цифровых |

схемах, |

|

||||||||

|

|

|

|

|

1QD |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

12 |

|

|

|

|

|

|

|

требуют быстрых переходных токов, которые не могут быть п оданы |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

2CLR |

|

|

|

|

|

|

|

большинством источников питания. Это приводит к выбросам |

||||||||||

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

1CLR |

|

|

|

|

|

|

|

напряжения питания. Если эти выбросы превышают допустимы й |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

предел ±5% для питания ±12 В или ±10% для питания +5 В, то |

||||||||

|

|

|

|

|

|

|

|

74HC393 |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

характеристики АЦП ухудшатся. Kроме того, выбросы на часто тах |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

выше 100 кГц также приведут к ухудшению характеристик. Для |

||||||

|

компенсации конечного импеданса источников по переменн ому |

||||||

Если используется непрерывный тактовый сигнал, то пользо ватель |

току необходимо ”запасать” заряд в развязывающих |

||||||

должен избегать фронтов CLK в момент отсоединения VIN, ò.å. íà |

конденсаторах. Эти конденсаторы могут существенно снизи ть |

||||||

заднем фронте SAMPLE (см. спецификации tFCD). Длительности |

импеданс по переменному току, ”подключенный” ко входам питания |

||||||

высокого и низкого уровней в периоде CLK (tCH è tCL) могут меняться, |

AD677, что в свою очередь значительно снизит амплитуду выброс ов |

||||||

но они должны соответствовать значениям, приведенным в |

напряжения. Чтобы эта развязка была эффективной, нужно |

||||||

спецификациях. Внутренний компаратор принимает решения на |

следовать |

определенным |

принципам |

|

проектирования. |

||

передних фронтах CLK. Чтобы задний фронт CLK не вносил |

Развязывающие конденсаторы, обычно 0.1 мкФ, должны |

||||||

искажения в процесс установления компаратора, tCL должно |

размещаться как можно ближе к каждому выводу питания AD677. |

||||||

превышать как минимум половину tCLK. Не рекомендуется менять |

Важно, чтобы эти конденсаторы были расположены физически |

||||||

состояние входа SAMPLE близко к концам периодов CLK, чтобы |

близко к ИС, чтобы снизить до минимума индуктивность доро жки |

||||||

переходные процессы не мешали установке внутреннего |

печатной платы между конденсатором и выводом питания. |

||||||

компаратора. |

Цифровое питание (VDD) должно быть развязано на цифровую |

||||||

Во время преобразования регистрируются внутренние вели чины, |

землю, а аналоговые питания (VCC è VEE) — на аналоговую землю. |

||||||

Вход опорного напряжения |

также рассматривается в этом |

||||||

являющиеся причиной погрешностей по постоянному сигнал у, |

отношении как вход питания и должен быть развязан аналоги чным |

||||||

такие как напряжение смещения компаратора; они сохраняют ся на |

|||||||

образом. Все это показано на Ðèñ. 4. |

|

|

|||||

внутренних конденсаторах и используются для корректиро вки |

|

|

|

|

|

|

|

вызванных ими погрешностей, когда это необходимо. Так как эти |

Рис. 4. Схема развязки выводов питания |

||||||

напряжения хранятся на конденсаторах, то они спадают со |

|||||||

|

|

|

|

|

|

||

временем вследствие утечек, и поэтому необходимо их |

|

|

|

|

|

|

|

периодическое обновление. По этой причине указывается |

+5 Â |

VDD |

|

AD677 |

|

|

|

максимальное время преобразования tC (1000 мкс). С момента |

|

DGND |

AGND |

VCC |

VEE |

VREF |

|

перехода SAMPLE в 1 до завершения 17-го импульса CLK должно |

|

||||||

|

|

|

|

|

|

||

пройти не более 1000 мкс, чтобы точность соответствовала |

0.1 ìêÔ |

|

|

0.1 ìêÔ |

|

|

|

паспортным данным. С другой стороны, максимальное время |

|

|

|

0.1 ìêÔ |

|||

|

|

|

|

||||

между отдельными преобразованиями не ограничено. |

|

|

|

0.1 ìêÔ |

|

A1602P02 |

|

|

|

|

|

|

|||

Выход AD677 кодируется в двоичном дополнительном формате, ка к |

|

|

|

+12 Â |

–12 Â |

||

показано в Òàáë. I. Схемой AD677 предусмотрено ограничение |

|

Системная |

Системная |

|

|

||

выходного кода в случае, когда входной сигнал выходит за пределы |

|

цифровая |

аналоговая |

|

|

||

|

земля |

земля |

|

|

|||

шкалы. |

|

|

|

|

|

|

|

64 |

|

|

|

Публикуется с разрешения |

|||

|

|

|

|

|

фирмы Analog Devices |

||

16-РАЗРЯДНЫЙ АЦП С ЧАСТОТОЙ ДИСKРЕТИЗАЦИИ 100 KSPS |

AD677 |

В дополнение к этому полезно расположить большие емкости (>47 мкФ) в точке подсоединения шин питания к плате и емкости 10 мкФ недалеко от АЦП, чтобы еще сильнее ослабить низкочастотные пульсации. В системах, которые будут работ ать в условиях особо сильных внешних наводок, могут оказаться необходимыми дополнительные развязки. RC-фильтры на каждой шине питания вместе со специальной стабилизацией напряж ения могут существенно снизить влияние пульсаций напряжения питания (подробнее см. Ðèñ. 7).

РАЗВОДKА ПЕЧАТНОЙ ПЛАТЫ

Проектирование преобразователей высокого разрешения тр ебует пристального внимания к разводке печатной платы. Большое значение имеет сопротивление дорожек. При протекании ток а 1.22 мА по дорожке сопротивлением 0.5 Ом возникает падение напряжения 0.6 мВ, что составляет 4 МЗР при разрешении 16 разрядов и полной шкале 10 В. Помимо падения напряжения на заземляющих проводниках (ground drop) следует учитывать индуктивные и емкостные связи, особенно когда прецизионные аналоговые сигналы соседствуют с цифровыми сигналами на одной плате.

Аналоговые и цифровые сигналы не должны иметь общие обрат ные пути. Kаждый сигнал должен иметь соответствующую ”аналого вую” или ”цифровую” обратную дорожку, расположенную рядом с сигнальной дорожкой. Если следовать этой рекомендации, то сигнальные петли будут иметь малую площадь, что уменьшит индуктивные шумовые наводки. Настоятельно рекомендуетс я использовать широкие дорожки на печатных платах, толстые провода и заземляющие плоскости, чтобы сигнальные пути им ели низкий импеданс. Также желательны раздельные ”аналоговая” и ”цифровая” заземляющие плоскости с единственной общей т очкой (пересечением) на ИС ,чтобы минимизировать наводки между аналоговой и цифровой схемами. Аналоговые сигналы должны быть проведены как можно дальше от цифровых и должны пересекать их, если этого не удается избежать, только под п рямыми углами. Сплошной ”аналоговый” заземляющий слой вокруг AD677 изолирует его от больших токов переключения, протекающих по земле. По этим причинам использование соединений накрутк ой проводов при сборке схемы не обеспечивает удовлетворите льных характеристик; предпочтительна тщательно продуманная п ечатная плата.

ЗАЗЕМЛЕНИЕ

При значительной длине проводника эта разность потенциа лов вполне может достигнуть нескольких МЗР (при полной шкале 10 В и разрешении 16 разрядов МЗР примерно равен 0.15 мВ). Это сразу же исказит входной сигнал АЦП, если АЦП измеряет входное напряжение по отношению к земле источника питания (AGND), как показано на Ðèñ. 5à. Чтобы справиться с этой проблемой в AD677 предусмотрен вход ”чистой земли” (AGND SENSE). На Ðèñ. 5b показано, как можно использовать AGND SENSE для устранения погрешности, возникающей в схеме Ðèñ. 5à. Íà Ðèñ. 5b также показано, как следует экранировать сигнальные провода в у словиях внешних наводок, чтобы избежать емкостных связей. Если ожидается, что будут преобладать индуктивные (магнитные) наводки, например, если рядом расположены двигатели, то до лжны использоваться витые пары.

Вывод цифровой земли — это общая точка для всех цифровых сигналов AD677. Этот вывод должен быть подсоединен к цифровой общей точке системы. Kак показано на Ðèñ. 4, цифровая и аналоговая земли, должны быть соединены в системе в одной точке, желательно на самой AD677.

Рис. 5а. Входной сигнал АЦП искажен падением напряжения IR на заземляющем проводнике: VIN = VS + V.

AD677

VIN

VS

V

AGND

AGND

|

|

|

|

|

|

|

|

|

|

|

|

A1602P03 |

|

|

|

|

|

|

|

|

|

|

|

|

Земля |

|

|

|

|

|

|

|

|

|

|

|

|

|

Земляной провод |

|

|

|

|

|

IGROUND > 0 |

|

источника |

||||

|

|

|

|

|

|

питания |

||||||

(дорожка) |

|

|

|

|

|