всё о микросхемах / Микросхемы для АЦП и мультимедиа

.pdf

СИГМА-ДЕЛЬТА АЦП |

AD7710 |

(Временная диаграмма Ðèñ. 11à предполагает, что к линии SCLK подключен нагрузочный резистор.)

Íà Ðèñ. 11b приведена временная диаграмма операции записи в AD7710 для случая, когда TFS переходит в 1 во время операции записи, а затем опять возвращается в 0, чтобы записать оставшуюся часть слова данных. Kак и ранее, подразумеваетс я, что на выходе SCLK подключен нагрузочный резистор. Временные параметры и функции на Ðèñ. 11b аналогичны Ðèñ. 11à, за исключением нескольких дополнительных параметров, показывающих временные соотношения в момент перехода TFS в 1 во время передачи слова.

Kак и ранее, спадающий фронт TFS включает тактовый сигнал SCLK. Записываемые в AD7710 данные должны принимать правильные значения к приходу передних фронтов SCLK. Нарастающий фронт TFS выключает сигнал SCLK. TFS должен переходить в 1 во время низкого уровня на SCLK. Kогда TFS снова возвращается в 0, это снова включает выход SCLK. Kогда все биты данных записаны в ИС, SCLK отключается, согласно Ðèñ. 11à.

Режим внешнего тактирования

Режим внешнего тактирования AD7710 устанавливается низким уровнем на входе MODE. В этом режиме вывод SCLK AD7710 является входом и на него должен подаваться внешний последовательный тактовый сигнал. Режим внешнего тактир ования предназначен для непосредственного интерфейса с систем ами, которые имеют выход последовательного тактового сигнал а, синхронизованный с последовательным выводом данных; это такие микроконтроллеры, как 80C51, 87C51, 68HC11 и 68HC05 и большинство сигнальных (DSP) процессоров.

Операция чтения

Kак и в режиме самотактирования данные могут быть считаны или из выходного регистра, или из управляющего регистра, или и з регистров калибровки. Входной сигнал A0 определяет, из какого регистра будут считываться данные — из управляющего реги стра или из выходного/калибровки (см. биты MD2...MD0). Уровень сигнала A0 должен оставаться неизменным на протяжении все й операции чтения. При A0 = 1 данные считываются или из выходног о регистра, или из регистров калибровки. При А0 = 0 данные считываются из управляющего регистра.

Переключение линии DRDY зависит только от частоты обновления выходных данных ИС и от считывания регистра выходных данн ых. DRDY переходит в 0 когда новое слово данных поступает в регистр выходных данных. DRDY переключается обратно в 1 когда последний бит данных (16-й или 24-й бит) считывается из выходного регистра. Если данные не считываются из выходно го

регистра, то DRDY будет оставаться равным 0. Выходной регистр будет продолжать обновляться (с той же самой частотой), но это не будет отражаться на выходе DRDY. В этом случае чтение из AD7710 даст последнее слово, которое было помещенно в выходной регистр. Если во время считывания данных из выходного рег истра приходит новое слово данных, то DRDY никак на это не прореагирует и это новое слово данных будет для пользоват еля потеряно. Чтение из управляющего регистра или из регистро в калибровки не влияет на статус DRDY.

Данные можно считать из выходного регистра только когда DRDY = 0. Если RFS переходит в 0 когда DRDY = 1, то никакой передачи данных не будет. DRDY никак не влияет на чтение данных из управляющего регистра или из регистров калибровки.

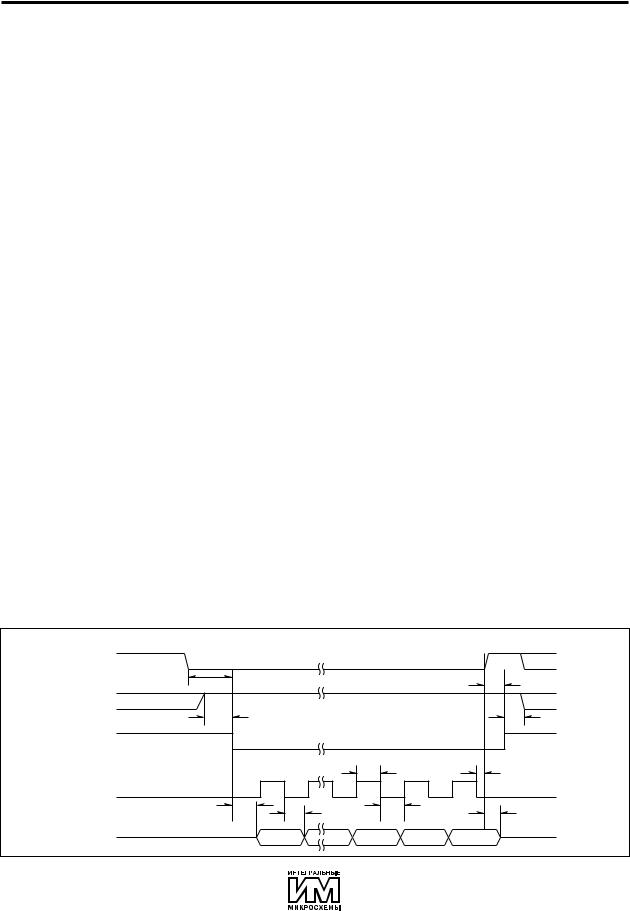

Íà Ðèñ. 12à è 12b приведены временные диаграммы чтения из AD7710 в режиме внешнего тактирования. На Ðèñ. 12à показан случай, когда все данные считываются из AD7710 за одну операцию чтения. Ðèñ. 12b — это случай, когда слово данных считывается из AD7710 за несколько операций чтения. Обе диаграммы показывают чтение из выходного регистра AD7710. Чтение из управляющего регистра или из регистров калибровки аналогично, только в этих случаях сигнал DRDY никак не будет связан с чтением. В зависимости от частоты обновления выходных данных он мож ет перейти в 0 на любой стадии операции чтения управляющего/калибровочного регистра, при этом никак на н ее не влияя, и его статус следует игнорировать. В операции чтени я управляющего/калибровочного регистра всегда должны считываться все 24 бита данных соответствующего регистра.

Íà Ðèñ. 12à приведена операция чтения из AD7710, когда RFS остается равным 0 на протяжении передачи всего слова данн ых. Kогда DRDY равен 0, на входе RFS устанавливается 0. Между операциями чтения и записи на входе SCLK должен быть постоянный 0. Переход RFS в 0 выводит на линию SDATA старший бит (СЗР) считываемого слова. Все последующие биты выводят ся по задним фронтам последовательного тактового сигнала SCL K и принимают правильные значения до прихода следующих пере дних фронтов SCLK. Предпоследний задний фронт SCLK выводит младший бит (MЗР), а последний задний фронт SCLK сбрасывает DRDY в 1. Нарастающий фронт DRDY отключает линию SDATA.

Íà Ðèñ. 12b приведена временная диаграмма операции чтения в которой RFS возвращается в 1 во время передачи слова, а затем опять возвращается в 0, чтобы считать оставшуюся часть сло ва. Временные параметры и функции аналогичны Ðèñ. 12à, íî íà Ðèñ. 12b есть несколько дополнительных временных параметров, относящихся к моменту, когда RFS возвращается в 1 во время передачи слова. RFS должен переходить в 1 во время низкого уровня SCLK. По переднему фронту RFS выходная линия SDATA

|

Рис. 12а. Чтение выходного регистра в режиме внешнего тактир ования |

|

|

DRDY(Î) |

|

|

|

|

t20 |

t21 |

|

AO(Ι) |

|

|

|

|

t22 |

|

t23 |

RFS(Ι) |

|

|

|

|

|

t28 |

|

|

|

t26 |

|

SCLK(Ι) |

t24 |

t27 |

t29 |

|

|||

|

|

t25 |

|

|

|

|

|

SDATA(Î) |

ÑÇÐ |

ÌÇÐ |

3-е состояние |

|

|||

|

|

|

A1801Z05 |

150 |

|

|

Публикуется с разрешения |

|

|

|

фирмы Analog Devices |

СИГМА-ДЕЛЬТА АЦП |

|

|

|

AD7710 |

Рис. 12b. Чтение выходного регистра в режиме внешнего тактир ования(RFS возвращается в 1 во время операции чтения) |

||||

DRDY(Î) |

|

|

|

|

|

t20 |

|

|

|

AO(Ι) |

|

|

|

|

|

t22 |

|

|

|

RFS(Ι) |

|

|

|

|

|

t26 |

t30 |

|

|

|

|

|

|

|

SCLK(Ι) |

t24 |

t27 |

t24 |

|

|

|

|||

|

t25 |

t31 |

t25 |

|

|

|

|||

SDATA(Î) |

ÑÇÐ |

ÁÈÒ N |

3-е состояние |

ÁÈÒ N+1 |

|

||||

|

|

|

|

A1801Z06 |

отключается. DRDY будет оставаться равным 0 до тех пор, пока все биты слова не будут считаны из AD7710, независимо от того, сколько раз RFS изменяет состояние во время операции чтения. В зависимости от интервала между задним фронтом SCLK и нарастающим фронтом RFS, на выходной линии, прежде чем RFS перейдет в 1, может появиться следующий бит (N+1). Kогда RFS снова возвращается в 0, это включает линию SDATA и выводит на SDATA следующий бит слова данных. Kогда все слово будет передано, DRDY перейдет в 1, отключая линию SDATA, согласно

Ðèñ. 12à.

Операция записи

Данные могут быть записаны или в управляющий регистр или в регистры калибровки. В обоих случаях на операцию записи н е влияет статус DRDY, и, в свою очередь, операция записи никак не влияет на статус DRDY. При записи в управляющий/калибровочный регистр должны записываться все 24 бита.

Íà Ðèñ. 13à показана операция записи в AD7710, в которой TFS остается равным 0 на всем ее протяжении. Входной сигнал A0 определяет, куда будут записаны данные – в управляющий регистр или в регистры калибровки. A0 должен оставаться неизменным на протяжении всей операции последовательной записи. Kак обы чно, SCLK должен быть равным 0 между операциями чтения и записи.

Последовательные данные, записываемые в AD7710, должны иметь правильные значения на высоких полупериодах подаваемог о извне тактового сигнала SCLK. Данные записываются в AD7710 во время высокого полупериода SCLK; первым записывается СЗР. На последнем активном высоком полупериоде SCLK в AD7710 записывается младший бит.

Íà Ðèñ. 13b приведена временная диаграмма операции записи в AD7710 для случая, когда TFS переходит в 1 во время операции записи, а затем опять возвращается в 0 чтобы записать остав шуюся часть слова данных. Временные параметры и функции на Ðèñ. 13b аналогичны Ðèñ. 13à, за исключением нескольких дополнительных параметров, показывающих временные соотношения в момент перехода TFS в 1 во время передачи слова.

Записываемые в AD7710 данные должны принимать правильные |

1 |

значения к приходу передних фронтов SCLK. TFS должен |

переходить в 1 во время низкого уровня на SCLK. После того как TFS снова возвратится в 0, следующий бит данных будет записан в AD7710 во время первого же высокого полупериода SCLK. Во время последнего активного высокого полупериода SCLK в AD7710 записывается младший бит.

|

Рис. 13а. Запись в управляющий регистр или в регистры калибр овки в режиме внешнего тактирования |

|

AO(Ι) |

|

|

|

t32 |

t33 |

TFS(Ι) |

|

|

|

t26 |

t34 |

|

|

|

SCLK(Ι) |

|

t27 |

|

|

|

|

|

t35 |

|

|

t36 |

SDATA(Ι) |

ÑÇÐ |

ÌÇÐ |

|

|

A1801Z07 |

Публикуется с разрешения |

151 |

фирмы Analog Devices |

|

СИГМА-ДЕЛЬТА АЦП |

|

|

AD7710 |

|

Рис. 13b. Запись в управляющий регистр или в регистры калибро вки в режиме внешнего тактирования(TFS переходит в 1 |

||||

|

во время операции записи) |

|

||

AO(Ι) |

|

|

|

|

|

t32 |

|

|

|

TFS(Ι) |

|

|

|

|

|

t26 |

t30 |

|

|

SCLK(Ι) |

t27 |

|

t35 |

|

|

|

|||

|

t35 |

t36 |

t36 |

|

|

|

|||

|

|

|

||

SDATA(Ι) |

ÑÇÐ |

ÂÈÒ N |

ÁÈÒ N+1 |

|

|

|

|

A1801Z08 |

|

УПРОЩЕНИЕ ИНТЕРФЕЙСА |

|

Рис. 15. Блок–схема непрерывной операции чтения из |

||

В некоторых применениях пользователю, возможно, будет не нужна |

||||

|

AD7710 |

|||

запись в регистры калибровки ИС. В этом случае можно упрос тить |

|

|||

|

|

|||

последовательный интерфейс с AD7710, если соединить линию TFS |

|

СТАРТ |

||

со входом A0 (см. Ðèñ. 14). Это означает, что при записи в ИС |

|

|

||

данные будут записаны в управляющий регистр (так как в это м |

|

|

||

случае A0 = 0 когда TFS = 0), а при чтении из ИС данные будут |

|

УСТАНОВКА И |

||

считаны из выходного регистра или из регистров калибровк и (так |

|

ИНИЦИАЛИЗАЦИЯ |

||

|

ПОСЛЕДОВАТЕЛЬНОГО |

|||

как A0 = 1 когда RFS = 0). Следует отметить, что в такой схеме нельзя |

|

ПОРТА МИКРОКОНТРОЛЛЕРА/ |

||

читать из управляющего регистра. |

|

|

МИКРОПРОЦЕССОРА |

|

|

|

|

||

Рис. 14. Упрощенный интерфейс, в котором TFS |

УСТАНОВИТЬ |

|

||

|

подключен к A0 |

|

|

|

|

|

RFS; TFS Â "1" |

|

|

|

20 |

|

|

|

|

RFS |

|

|

|

Четыре |

22 |

|

|

|

SDATA |

|

ОПРАШИВАНИЕ DRDY |

||

интерфейсных |

|

|||

1 |

|

|||

линии |

AD7710 |

|

|

|

SCLK |

|

|

||

|

|

|

||

|

19 |

|

|

|

|

TFS |

|

|

|

|

4 |

|

|

|

|

A0 |

|

|

|

|

|

|

DRDY |

|

|

|

A1801P06 |

РАВЕН "0" |

Íåò |

|

|

|

||

Еще один метод упрощения интерфейса состоит в том, чтобы в |

|

|

||

качестве сигнала TFS использовать инвертированный сигнал RFS. |

Äà |

|

||

Отметим однако, что в обратном случае (на RFS подается |

УСТАНОВИТЬ RFS В "0" |

|||

инвертированный TFS) возникнут ошибки при записи. |

|

|

||

ИНТЕРФЕЙС С |

|

|

|

|

|

×3 |

|

|

МИKРОKОМПЬЮТЕРАМИ/МИKРОПРОЦЕССОРАМИ |

|

|

ЧТЕНИЕ |

|

|

|||

Гибкий последовательный интерфейс |

AD7710 позволяет |

|

|

|

||||

|

ПОСЛЕДОВАТЕЛЬНОГО |

|

|

|||||

подключать этот АЦП к большинству микрокомпьютеров и |

|

БУФЕРА |

|

|

||||

|

|

|

|

|

|

|||

микропроцессоров. На Ðèñ. 15 приведена блок-схема типичной |

|

|

|

|

|

|

||

программы чтения данных из AD7710 в микрокомпьютер, а на |

|

|

|

|

|

|

||

|

|

УСТАНОВИТЬ RFS В "1" |

|

|

||||

Ðèñ. 16 — программы записи данных в AD7710. На Ðèñ. 17, 18 è 19 |

|

|

|

|

||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

приведены типичные схемы интерфейсов. |

|

|

|

|

|

|

|

|

Блок-схема Ðèñ. 15 соответствует непрерывной операции чтения |

|

ИЗМЕНЕНИЕ |

|

|

||||

|

ПОРЯДКА СЛЕДОВАНИЯ |

|

|

|||||

из выходного регистра AD7710. В приведенном примере линия |

|

БИТОВ |

|

|

||||

|

|

|

|

|

|

|||

DRDY непрерывно опрашивается. В зависимости от конфигурации |

|

|

|

A1801P07 |

||||

микропроцессора сигнал DRDY может быть подан на вход |

|

|

|

|||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

прерывания — в этом случае DRDY |

будет автоматически |

На блок-схеме также указано изменение порядка битов после того |

||||||

генерировать прерывание (не нужно опрашивание DRDY). ”Чтение |

||||||||

как они считаны из последовательного порта. Это зависит о т того, в |

||||||||

последовательного буфера” — это что угодно от одной опера ции |

||||||||

чтения до трех операций чтения (когда 24 бита данных считываются |

каком порядке микропроцессор ожидает данные — начиная с С ЗР |

|||||||

или начиная с МЗР. AD7710 выводит слово начиная с СЗР. |

||||||||

в 8-разрядный регистр последовательного обмена). Операция |

||||||||

чтения из управляющего/калибровочного регистра аналоги чна, |

Блок-схема Ðèñ. 16 показывает одну операцию записи 24- |

|||||||

разве что в этом случае сигнал DRDY игнорируется. При чтении из |

разрядного слова в управляющий/калибровочный регистр AD7710. |

|||||||

управляющего регистра А0 переключается в 0, когда RFS |

Данные перемещаются из памяти данных в аккумулятор, прежд е |

|||||||

переводится в 0. |

|

|

|

|

|

|

|

|

152 |

Публикуется с разрешения |

|

фирмы Analog Devices |

СИГМА-ДЕЛЬТА АЦП |

|

|

|

|

|

AD7710 |

чем они будут записаны в последовательный буфер. Некоторы е |

8XC51 ожидает первым MЗР. Следовательно, данные, считанные в |

|||||

микропроцессорные системы допускают запись данных |

последовательный буфер, должны быть переупорядочены, что бы |

|||||

непосредственно из памяти данных в последовательный буф ер. |

считанное из AD7710 слово было в аккумуляторе в правильном |

|||||

Запись данных из аккумулятора в последовательный буфер в |

âèäå. |

|

|

|

|

|

общем случае будет состоять из двух или трех операций зап иси, в |

|

|

|

|

|

|

зависимости от размера последовательного буфера. |

Рис. 17. Интерфейс AD7710 – 8051 |

|||||

Рис. 16. Блок-схема одной операции записи в AD7710 |

|

|

|

DVDD |

|

|

|

|

|

|

|

|

|

СТАРТ |

|

|

|

5 |

SYNC |

|

|

|

|

|

|

||

|

|

|

|

20 |

|

|

|

|

P1.0 |

|

RFS |

|

|

|

|

|

19 |

|

||

УСТАНОВКА И |

|

P1.1 |

|

TFS |

|

|

|

|

|

|

|||

ИНИЦИАЛИЗАЦИЯ |

|

|

21 |

|

||

ПОСЛЕДОВАТЕЛЬНОГО |

|

P1.2 |

|

DRDY |

|

|

|

|

|

|

|||

ПОРТА МИКРОКОНТРОЛЛЕРА/ |

|

|

4 |

|

||

МИКРОПРОЦЕССОРА |

8XC51 |

P1.3 |

|

A0 |

AD7710 |

|

|

|

|||||

|

|

|

22 |

|

||

|

|

P3.0 |

|

SDATA |

|

|

|

|

|

1 |

|

||

УСТАНОВИТЬ |

|

P3.1 |

1 |

SCLK |

|

|

|

|

|

||||

RFS; TFS è À0 Â "1" |

|

|

6 |

|

||

|

|

|

|

|

||

|

|

|

|

MODE |

|

|

|

|

|

|

|

|

|

ЗАГРУЗИТЬ ДАННЫЕ |

|

|

A1801P09 |

|

|

|

|

|

|

|

|

|

|

ИЗ ЯЧЕЙКИ ПАМЯТИ |

Таблица VII. Программа 8XC51 для чтения из AD7710 |

|||||

В АККУМУЛЯТОР |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команды |

Пояснения |

|

|

|

|

ИЗМЕНЕНИЕ |

|

|

|

|

|

MOV SCON, |

Kонфигурировать 8XC51 в режим 0 |

|

|

||

|

|

|

|

|

|

|

#000100001B; |

|

|

||||

|

|

ПОРЯДКА СЛЕДОВАНИЯ |

|

|

|

|

|

|

|

||||

|

|

БИТОВ |

|

|

|

|

|

|

MOV IE, |

Маскировать все прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

#00010000B; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SETB 90H |

Установить P1.0, используемый как RFS |

|

|

|

|

УСТАНОВИТЬ TFS и A0 |

"0" |

|

|

|

|

SETB 91H |

Установить P1.1, используемый как TFS |

|

|

||

|

|

|

|

|

|

|

|

|

|

SETB 93H |

Установить P1.3, используемый как A0 |

|

|

|

|

|

|

|

|

|

|

|

|

MOV R1,#003H; |

Устанавливается число байтов, которые должны быть |

|

|

|

|

|

|

|

|

|

× 3 |

|

|

считаны в операции чтения |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

ЗАПИСЬ ДАННЫХ ИЗ |

|

|

|

|

MOV R0,#030H; |

Начальный адрес области памяти, в которую будут |

|

|

|||

|

|

|

|

|

|

помещены байты |

|

|

|||||

|

|

АККУМУЛЯТОРА В |

|

|

|

|

|

|

|

|

|||

|

|

ПОСЛЕДОВАТЕЛЬНЫЙ БУФЕР |

|

|

|

|

MOV R6,#004H; |

Использовать P1.2 как DRDY |

|

|

|||

|

|

|

|

|

|

|

|

|

|

WAIT: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOP; |

|

|

1 |

|

|

УСТАНОВИТЬ TFS и A0 В "1" |

|

|

|

|

MOV A,P1; |

Считать порт 1 |

|

||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

ANL A,R6; |

Маскировать все биты роме DRDY |

|

|

|

|

|

|

|

|

|

|

|

|

JZ READ; |

Если ноль, то читать |

|

|

|

КОНЕЦ |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

SJMP WAIT; |

Иначе продолжать опрос |

|

|

||||

|

|

|

|

|

A1801P08 |

|

|

|

READ: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLR 90H |

Переключить RFS в 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

В программу может также входить обращение порядка битов д о |

CLR 98H |

Сбросить флаг приема |

|

|

|||||||||

записи их в последовательный буфер. Это зависит от того, ка к |

POLL: |

|

|

|

|||||||||

микропроцессор передает данные — начиная с СЗР или начина я с |

JB 98H, READ1 |

Проверяется флаг прерывания при приеме |

|

|

|||||||||

MЗР. AD7710 считает, что данные передаются начиная с СЗР. В |

SJMP POLL |

|

|

|

|||||||||

READ1: |

|

|

|

||||||||||

случае, если данные считываются или записываются побайтн о, и |

|

|

|

||||||||||

MOV A,SBUF; |

Чтение буфера |

|

|

||||||||||

при этом порядок следования битов должен быть обращен, эт о |

|

|

|||||||||||

RLC A; |

Переупорядочивание данных |

|

|

||||||||||

обращение должно делаться для каждого байта. |

|

|

|

|

|||||||||

|

|

MOV B.0,C; |

Обратный порядок битов |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

Интерфейс AD7710 – 8051 |

|

|

|

|

|

|

RLC A; |

|

|

|

|||

|

|

|

|

|

|

MOV B.1,C; RLC A; MOV |

|

|

|

||||

Íà Ðèñ. 17 приведена схема интерфейса между AD7710 и |

B.2,C; |

|

|

|

|||||||||

микроконтроллером 8XC51. |

Äëÿ |

AD7710 |

установлен |

режим |

RLC A; |

|

|

|

|||||

внешнего |

тактирования, а |

äëÿ |

8XC51 |

установлен |

режим |

MOV B.3,C; RLC A; MOV |

|

|

|

||||

B.4,C; |

|

|

|

||||||||||

последовательного интерфейса 0. Выход DRDY AD7710 подключен к |

|

|

|

||||||||||

RLC A;MOV B.5,C;RLC |

|

|

|

||||||||||

входу P1.2 порта 8XC51, так что 8XC51 опрашивает сигнал DRDY. |

|

|

|

||||||||||

Линия DRDY может быть подключена ко входу INT1 8XC51, если |

A;MOV B.6,C; |

|

|

|

|||||||||

|

|

|

|

||||||||||

предпочтительна система, срабатывающая по прерываниям. |

|

|

|

|

|||||||||

RLC A; MOV B.7,C; |

|

|

|

||||||||||

Òàáë. VII приведена типовая программа для 8XC51, используемая |

MOV A,B; |

|

|

|

|||||||||

MOV @R0,A; |

Записать данные в память |

|

|

||||||||||

для однократной операции |

чтения 24-разрядного слова из |

|

|

||||||||||

INC R0 |

Инкрементировать указатель адреса в памяти |

|

|

||||||||||

выходного регистра AD7710. В Òàáë. VIII приведена типичная |

|

|

|||||||||||

DEC R1 |

Декрементировать счетчик байтов |

|

|

||||||||||

программа однократной операции записи в управляющий рег истр |

MOV A,R1 |

|

|

|

|||||||||

AD7710. 8XC51 в операции записи выводит данные начиная с MЗР, |

JZ END |

Прейти, если ноль |

|

|

|||||||||

тогда как AD7710 ожидает первым СЗР, поэтому данные, которые |

JMP WAIT |

Выбрать следующий байт |

|

|

|||||||||

должны быть переданы, должны быть переупорядочены перед |

END: |

|

|

|

|||||||||

записью в |

выходной последовательный |

регистр. Во |

время |

SETB 90H |

Переключить RFS в 0 |

|

|

||||||

операции чтения AD7710 выводит данные начиная с СЗР, тогда как |

FIN: |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

SJMP FIN |

|

|

|

Публикуется с разрешения |

153 |

фирмы Analog Devices |

|

СИГМА-ДЕЛЬТА АЦП |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7710 |

|||||

Таблица VIII. Программа 8XC51 для записи в AD7710 |

|

|

|

|

Рис. 18. Интерфейс AD7710 — 68HC11 |

|||||||||||||||||||

|

Команды |

|

|

|

Пояснения |

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

MOV SCON, |

|

Kонфигурировать 8XC51 в режим 0 и разрешить |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

#00000000B; |

|

|

последовательный прием |

|

|

|

|

|

|

|

|

DVDD |

|

DVDD |

|

|

|

||||||

|

MOV IE, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Разрешить прерывание передачи (transmit interrupt) |

|

|

|

|

|

|

|

|

|

5 |

|

|

|

||||||||||

|

#10010000B; |

|

|

|

|

|

SS |

|

|

|

|

SYNC |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|||||

|

MOV IP, |

Установить прерыванию передачи высший приоритет |

|

|

|

|

|

PC0 |

|

|

|

RFS |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

#00010000B; |

|

|

|

|

|

|

|

|

19 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

SET 91H |

|

|

Перевести TFS в 1 |

|

|

|

|

|

|

|

PC1 |

|

|

|

21 |

TFS |

|

|

|||||

|

SET 90H |

|

|

Перевести RFS в 1 |

|

|

|

|

|

|

|

PC2 |

|

|

|

DRDY |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|||||||||

|

MOV R1,#003H; |

Устанавливается число байтов, которые должны быть |

|

68HC11 |

|

PC3 |

|

|

|

A0 |

AD7710 |

|||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

записаны в операции записи |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|||||

|

MOV R0,#030H |

|

Начальный адрес байтов в памяти (ОЗУ) |

|

|

|

|

|

|

SCK |

|

|

|

SCLK |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|||||||||||

|

MOV A,#00H |

|

|

Очистить аккумулятор |

|

|

|

|

|

|

MISO |

|

|

|

SDATA |

|

|

|||||||

|

MOV SBUF,A; |

|

Инициализировать последовательный порт |

|

|

|

|

|

|

|

6 |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

WAIT: |

|

|

|

|

|

|

|

|

|

|

|

|

MOSI |

|

|

|

|

MODE |

|

|

|||

|

JMP WAIT; |

|

|

Ждать прерывание |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

NOP; |

|

|

Подпрограмма прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1801P10 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

MOV A,R1; |

|

|

Поместить R1 в аккумулятор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

JZ FIN; |

|

|

Если ноль, то перейти на FIN |

|

|

|

Рис. 19. Интерфейс AD7710 — ADSP-2105 |

||||||||||||||||

|

DEC R1; |

|

Декрементировать счетчик байтов R1 |

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

MOV A,@R; |

|

|

Переместить байт в аккумулятор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

INC R0; |

|

|

Инкрементировать адрес |

|

|

|

|

|

|

|

|

|

|

|

DVDD |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

Переупорядочить данные – от упорядочивания, при котором |

|

|

|

|

|

|

|

|

|

6 |

|

|

|||||||||

|

RLC A; |

|

|

|

|

|

|

|

|

|

MODE |

|

||||||||||||

|

первым идет МЗР, переходим к обратному порядку – |

|

|

|

|

|

|

|

|

|

|

20 |

|

|

||||||||||

|

|

|

|

|

|

начиная с СЗР |

|

|

|

|

|

|

|

|

RFS |

|

|

|

|

RFS |

|

|||

|

MOV B.0,C; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

21 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DRDY |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

RLC A; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

MOV B.1,C; RLC A; |

|

|

|

|

|

|

|

|

|

|

|

|

|

TFS |

|

|

|

|

|

|

|

||

|

MOV B.2,C; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74HC74 |

|

|

|

|

||||

|

RLC A; |

|

|

|

|

|

|

|

|

|

ADSP-2105 |

|

|

|

4 |

|

AD7710 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

D |

Q |

|

|

|||||||||

|

MOV B.3,C; RLC A; |

|

|

|

|

|

|

|

|

|

A0 |

|

|

A0 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

MOV B.4,C; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

Q |

|

19 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

DMWR |

|

|

TFS |

|

|

||||||

|

RLC A; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

||

|

MOV B.5,C; RLC A; |

|

|

|

|

|

|

|

|

|

|

|

|

|

DR |

|

|

|

|

SDATA |

|

|||

|

MOV B.6,C; |

|

|

|

|

|

|

|

|

|

|

|

|

|

DT |

|

|

|

|

|

|

|

||

|

RLC A; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

MOV B.7,C;MOV A,B; |

|

|

|

|

|

|

|

|

|

|

|

|

|

SCLK |

|

|

|

|

SCLK |

|

||||

|

CLR 93H; |

|

|

Переключить A0 в 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

CLR 91H; |

|

|

Переключить TFS в 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1801P11 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

MOV SBUF,A; |

|

|

Запись в последовательный порт |

|

|

Kîãäà |

последовательный |

тактовый |

сигнал |

ADSP-2105 |

|||||||||||||

|

RETI; |

|

|

Возврат из подпрограммы |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

конфигурирован как входной сигнал, необходимо два тактов ых |

||||||||||||||||||

|

FIN: |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

SETB 91H; |

|

|

Переключить TFS в 1 |

|

|

|

импульса для его корректной инициализации, прежде чем нач инать |

||||||||||||||||

|

|

|

|

|

|

прием данных. Следовательно, при первом чтении из AD7710 могут |

||||||||||||||||||

|

SETB 93H; |

|

|

Переключить A0 в 1 |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

быть получены неправильные данные. В этой схеме операция |

||||||||||||||||||

|

RETI; |

|

Возврат из подпрограммы прерывания |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

чтения из AD7710 считывает данные или из выходного регистра, ил и |

||||||||||||

Интерфейс AD7710 — 68HC11 |

|

|

|

|

|

|

из регистров калибровки. Данные не могут быть считаны из |

|||||||||||||||||

|

|

|

|

|

|

управляющего регистра. В операции чтения данные записыва ются |

||||||||||||||||||

Íà |

Ðèñ. |

18 |

приведена |

схема |

|

интерфейса |

AD7710 |

è |

||||||||||||||||

|

в управляющий или в калибровочный регистры. |

|

|

|||||||||||||||||||||

микроконтроллера 68HC11. Для AD7710 установлен режим |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

внешнего тактирования; для AD7710 установлен однокристальный |

DRDY используется как импульс синхроназации кадра для операц ии |

|||||||||||||||||||||||

режим и |

используется |

åãî |

ïîðò |

SPI. Выход DRDY |

AD7710 |

чтения из выходного регистра; он декодируется при помощи А0 и |

||||||||||||||||||

подсоединен ко входу |

PC0 |

порта |

68HC11, |

òàê |

÷òî |

68HC11 |

||||||||||||||||||

подается |

íà |

входы |

RFS |

êàê AD7710, òàê è ADSP-2105. |

||||||||||||||||||||

опрашивает сигнал DRDY. Линия DRDY может быть подключена ко |

||||||||||||||||||||||||

Зафиксированное значение на линии А0 подается как на вход ыTFS |

||||||||||||||||||||||||

входу IRQ 68HC11, если предпочтительна система, срабатывающая |

||||||||||||||||||||||||

AD7710 è ADSP-2105, òàê è íà âõîä À0 AD7710. |

|

|

||||||||||||||||||||||

по прерываниям. Линии MOSI и MISO должны быть |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

конфигурированы в монтажное ИЛИ. В зависимости от |

ПРИМЕНЕНИЯ |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

конфигурации |

интерфейса |

могут |

áûòü |

необходимыми |

Íà Ðèñ. 20 приведена схема |

подключения |

тензодатчика |

|||||||||||||||||

двунаправленные буферы между линиями MOSI и MISO 68HC11. |

|

непосредственно к одному из аналоговых входных каналов AD 7710. |

||||||||||||||||||||||

68HC11 кофигурирован в режим “ведущий”, бит CPOL установлен в |

Дифференциальные входы AD7710 подключены непосредственно к |

|||||||||||||||||||||||

мостовой схеме, в одно из плеч которой включен тензодатчи к. В |

||||||||||||||||||||||||

0, а бит CPHA установлен в 1. При главной тактовой частоте AD7710 |

||||||||||||||||||||||||

этой схеме внутренний источник опорного напряжения AD7710 |

||||||||||||||||||||||||

равной 10 MГц интерфейс сможет работать со всеми четырьмя |

||||||||||||||||||||||||

служит как источником напряжения для питания мостовой сх емы, |

||||||||||||||||||||||||

последовательными тактовыми частотами 68HC11. |

|

|

|

|||||||||||||||||||||

|

|

|

так и источником опорного напряжения для AD7710. В другом |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

Интерфейс AD7710 — ADSP-2105 |

|

|

|

|

|

|

варианте (схема Ðèñ. 21) питание AVDD AD7710 запитывает также и |

|||||||||||||||||

|

|

|

|

|

|

мостовую схему, а опорным напряжением для AD7710 служит |

||||||||||||||||||

Íà |

Ðèñ. |

19 |

приведена |

схема |

|

интерфейса |

AD7710 |

è |

||||||||||||||||

|

падение напряжения на резисторе, включенном последовате льно с |

|||||||||||||||||||||||

микропроцессора ADSP-2105. В этой схеме AD7710 работает в |

||||||||||||||||||||||||

мостовой схемой. В этом случае сопротивление этого ”опорн ого” |

||||||||||||||||||||||||

режиме самотактирования, |

а линии |

RFS è |

TFS |

ADSP-2105 |

||||||||||||||||||||

резистора равно отношению требуемого опорного напряжен ия к |

||||||||||||||||||||||||

конфигурированы как входы; линия последовательного такт ового |

||||||||||||||||||||||||

току возбуждения мостовой схемы. |

|

|

|

|

||||||||||||||||||||

сигнала ADSP-2105 также конфигурирована как вход. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

154 |

Публикуется с разрешения |

|

фирмы Analog Devices |

СИГМА-ДЕЛЬТА АЦП |

|

|

|

|

|

|

|

|

|

|

|

|

AD7710 |

Внутренний усилитель PGA AD7710 позволяет АЦП работать со |

позволяют ”сдвигать” этот аналоговый входной диапазон н а любую |

||||||||||||

слабыми входными сигналами — при максимальном усилении |

абсолютную величину между VSS è AVDD. |

||||||||||||

входной диапазон равен 20 мВ. Дифференциальные входы AD7710 |

|

|

|

|

|

|

|

|

|

||||

|

Рис. 20. Схема подключения тензодатчика к AD7710 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

Аналоговое |

|

||

|

|

|

|

|

|

|

|

|

|

питание + 5 В |

|

||

|

|

|

|

REF |

|

|

REF |

|

|

|

|

|

|

|

|

|

|

IN(–) |

|

|

IN(+) |

VBIAS |

AVDD |

DVDD |

|

||

|

|

AD7710 |

14 |

|

|

15 |

13 |

12 |

|

23 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

REF OUT |

16 |

ОПОРНОЕ |

|

|

|

|

|

|

|

|

|

|

Рабочий |

|

НАПРЯЖЕНИЕ |

|

|

|

|

|

|

|

|

|

||

|

|

2.5 Â |

|

АЦП С УРАВНОВЕШИВАНИЕМ |

|

|

|

||||||

элемент |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

ЗАРЯДОВ |

|

|

|

|

||

|

AIN1(+) |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AIN1(–) |

7 |

КОММУТАТОР |

|

|

СИГМА-ДЕЛЬТА |

ЦИФРОВОЙ |

|

|

|

|||

|

8 |

|

|

МОДУЛЯТОР С |

|

5 |

SYNC |

||||||

|

|

PGA |

|

КОРРЕКЦИЕЙ |

ФИЛЬТР |

|

|||||||

|

AIN2(+) |

9 |

|

|

|

ÍÓËß |

|

|

|

|

|

||

Дополнительный |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

элемент |

AIN2(–) |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

Программируемый |

|

|

|

|

2 |

MCLK IN |

||||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

усилитель КÓÑ=1÷128 |

|

ГЕНЕРАТОР |

3 |

MCLK OUT |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС |

|

|

|

|||||

|

|

|

|

|

|

УПРАВЛЯЮЩИЙ |

ВЫХОДНОЙ |

|

|

|

|||

|

|

|

|

|

|

|

РЕГИСТР |

РЕГИСТР |

|

|

|

||

|

|

18 |

24 |

11 |

20 |

19 |

6 |

22 |

1 |

21 |

4 |

A1801P12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AGND |

DGND VSS |

RFS TFS MODE SDATA SCLK DRDY |

A0 |

|

|||||||

1

Рис. 21. Альтернативный вариант получения опорного напряжения AD7710

Аналоговое питание |

|

|

|

Цифровое питание + 5 В |

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Ток возбуждения |

AVDD |

|

|

|

DVDD |

|

|

|

|

|

VBIAS |

|

|

REF OUT |

|||||

|

|

|

12 |

|

|

|

23 |

|

|

13 |

|

16 |

|

|

||||||

|

ΙEXCIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7710 |

|

|

REF IN(+) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

VREF |

|

15 |

|

|

|

|

|

|

ОПОРНОЕ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

R = ΙEXCIT |

REF IN(–) |

|

|

|

|

|

|

НАПРЯЖЕНИЕ 2.5 В |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рабочий |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦП С УРАВНОВЕШИВАНИЕМ |

|

|

|||||

элемент |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

ЗАРЯДОВ |

|

|

|

||

|

AIN1(+) |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AIN1(–) |

7 |

КОММУТАТОР |

|

|

СИГМА-ДЕЛЬТА |

ЦИФРОВОЙ |

|

|

|||

|

8 |

|

|

МОДУЛЯТОР С |

5 |

SYNC |

||||||

|

|

|

PGA |

|

КОРРЕКЦИЕЙ |

|

ФИЛЬТР |

|||||

|

AIN2(+) |

9 |

|

|

|

|

ÍÓËß |

|

|

|

|

|

Дополнительный |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

элемент |

AIN2(–) |

10 |

|

Программируемый |

|

|

|

2 |

MCLK IN |

|||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

усилитель КÓÑ=1÷128 |

|

|

ГЕНЕРАТОР |

MCLK OUT |

||||

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС |

|

|

||||

|

|

|

|

|

|

УПРАВЛЯЮЩИЙ |

ВЫХОДНОЙ |

|

|

|||

|

|

|

|

|

|

|

РЕГИСТР |

|

РЕГИСТР |

|

|

|

|

|

18 |

24 |

11 |

20 |

19 |

6 |

22 |

1 |

21 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

A1801P13 |

|

|

|

AGND |

DGND VSS |

RFS TFS MODE SDATA SCLK DRDY |

A0 |

|

||||||

Публикуется с разрешения |

|

|

|

|

|

|

|

|

|

|

|

155 |

фирмы Analog Devices |

|

|

|

|

|

|

|

|

|

|

|

|

ANALOG DEVICES

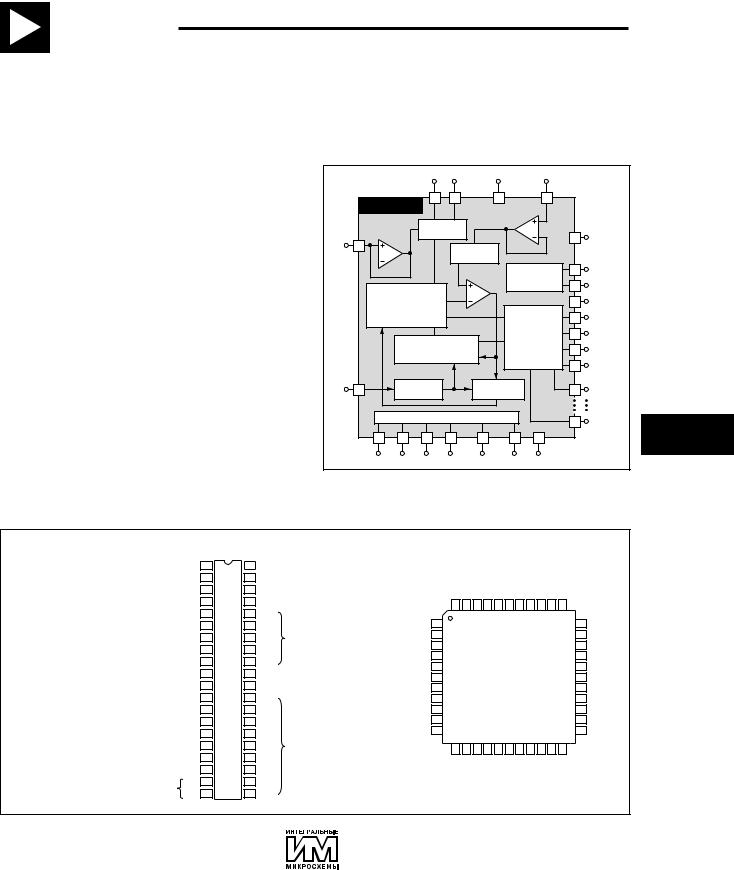

AD7882

16-РАЗРЯДНЫЙ АЦП С ВРЕМЕНЕМ ПРЕОБРАЗОВАНИЯ 2.5 мкс

ОСОБЕННОСТИ __________________________

ω Время преобразования . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . 2.5 ìêñ |

ω Разрешение . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

16 разрядов |

ω Автокалибровка |

|

ω Быстродействующий параллельный интерфейс |

|

ω Отношение Сигнал/Шум (SNR) . . . . . . . . . . . . . . . . . . . . . |

. . . . . 92 äÁ |

ω Низкое энергопотребление . . . . . . . . . . . . . . . . . . . . . . . |

. . . 200 ìÂò |

в дежурном режиме . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . 1 ìÂò |

ω Униполярный или биполярный входной диапазон |

|

ω Встроенный источник опорного напряжения . . . . . . . . . . . . |

. . . . 2.5 Â |

ω Питание . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ±5 Â |

ПРИМЕНЕНИЯ___________________________

Системы регистрации данных Цифровая обработка сигналов Спектральный анализ Сервоуправление на основе DSP

ОБЩЕЕ ОПИСАНИЕ_______________________

AD7882 — это быстродействующий 16-разрядный АЦП с функцией автокалибровки. AD7882 включает устройство выборки-хранения, собственно 16-разрядный АЦП со схемами автокалибровки, ист очник опорного напряжения 2.5 В и схему интерфейса. Автокалибровк а выполняется под управлением внутреннего контроллера; те м самым погрешности линейности, смещения и усиления снижаются до ±0.0015%. В последовательность калибровки можно также включить ко ррекцию системных погрешностей смещения и усиления, возникающих во

СТРУКТУРНАЯ СХЕМА_____________________ |

|||||||

|

|

CREF1 CREF2 |

DVDD |

AIN |

|

|

|

AD7882 |

|

|

|

|

|

||

|

|

КОРРЕКЦИЯ |

|

|

|

|

|

|

|

ОПОРЫ |

|

|

AVDD |

||

VREFIN |

|

|

|

|

|||

|

СДВОЕННОЕ |

|

|

|

|||

|

|

|

ÓÂÕ |

|

|

|

|

|

|

|

|

ОПОРНОЕ |

VREFOUT |

||

|

|

|

|

НАПРЯЖЕНИЕ |

|

|

|

|

16-РАЗРЯДНЫЙ |

|

2.5 Â |

AGND |

|||

|

|

|

|

|

|||

|

ÖÀÏ ÍÀ |

|

|

|

DGND |

||

|

ПЕРЕКЛЮЧАЕМЫХ |

|

|

||||

|

|

|

|

|

|||

|

КОНДЕНСАТОРАХ |

|

|

ADD0 |

|||

С САМОКАЛИБРОВКОЙ |

|

|

|||||

|

|

|

|

||||

|

|

|

ПАРАЛЛЕЛЬНЫЙ |

CS |

|||

|

|

РЕГИСТР |

|

ИНТЕРФЕЙС |

|

|

|

|

ПОСЛЕДОВАТЕЛЬНОГО |

|

RD |

||||

|

ПРИБЛИЖЕНИЯ |

|

|

|

|

||

|

|

|

|

|

WR |

||

LKIN |

ТАКТОВЫЙ |

СХЕМА |

|

DB0 |

|||

ГЕНЕРАТОР |

КАЛИБРОВКИ |

||||||

|

|

|

|||||

|

УПРАВЛЯЮЩАЯ ЛОГИКА |

|

DB15 |

||||

|

|

|

|

|

|||

|

|

|

|

|

A1603B01 |

1 |

|

M/S SLEEP |

CAL BIP/UP CONVST BUSY AVSS |

|

|

||||

внешних цепях формирования сигнала. Благодаря использов анию |

|||||||

сдвоенного устройства выборки-хранения минимальное вре мя между |

|||||||

отсчетами |

удалось |

снизить |

äî 2.5 |

ìêñ. ÀÖÏ |

также |

имеет |

|

ЦОКОЛЕВКА КОРПУСОВ _______________________________________________________________________________

керамический DIP (JL 40)

|

|

вид сверху |

|

||

Запуск блокировки |

CAL |

1 |

|

40 |

ADD0 |

"Занят" |

BUSY 2 |

|

39 |

RD |

|

Старт преобразования |

CONVST 3 |

|

38 |

CS |

|

"Режим синхронизация" |

M/S |

4 |

|

37 |

WR |

ыбор биполярного/униполярного диапазона |

BP/UP 5 |

|

36 |

DB15 |

|

Вход тактового сигнала |

CLKIN |

6 |

|

35 |

DB14 |

Дежурный режим |

SLEEP |

7 |

|

34 |

DB13 |

Аналоговая земля |

AGND1 |

8 |

|

33 |

DB12 |

Аналоговая земля |

AGND2 |

9 |

AD7882 |

32 |

DB11 |

Аналоговая земля |

AGND3 10 |

31 |

DVDD |

||

онденсатор развязки опорного напряжения |

CREF1 11 |

30 |

DGND |

||

онденсатор развязки опорного напряжения |

CREF2 12 |

29 DB10 |

|||

Вход опорного напряжения |

VREFIN 13 |

|

28 |

DB9 |

|

Выход внутреннего опорного напряжения |

VREFOUT 14 |

|

27 |

DB8 |

|

Плюс аналогового питания |

AVDD 15 |

|

26 |

DB7 |

|

Минус аналогового питания |

AVSS 16 |

|

25 |

DB6 |

|

Аналоговый вход |

AIN1 17 |

|

24 |

DB5 |

|

Аналоговый вход |

AIN2 18 |

|

23 |

DB4 |

|

Трехстабильные |

DB0 19 |

|

22 |

DB3 |

|

двунаправленные |

DB1 20 |

|

21 |

DB2 |

|

линии данных |

|

||||

|

|

|

A1603C02 |

|

|

корпус типа PQFP (S - 44)

Адресный вход |

|

BIP/UP |

M/S |

CONVST |

BUSY |

CAL |

ADD0 |

RD |

CS |

WR |

DB15 |

DB14 |

|

Выбор кристалла |

|

|

|||||||||||

Строб чтения |

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб записи |

|

44 |

43 |

42 |

41 |

40 |

39 |

38 |

37 |

38 |

39 |

40 |

|

|

|

|

|||||||||||

Трехстабильные |

CLKIN |

1 |

|

|

|

|

|

|

|

|

|

33 |

DB13 |

двунаправленные |

SLEEP |

2 |

|

|

|

|

|

|

|

|

|

32 |

DB12 |

AGND1 |

|

|

|

|

|

|

|

|

|

|

|

DB11 |

|

линии данных |

3 |

|

|

|

|

|

|

|

|

|

31 |

||

AGND2 |

4 |

|

|

|

|

|

|

|

|

|

30 |

DVDD |

|

|

|

|

|

|

|

|

|

|

|

||||

Плюс цифрового питания |

AGND3 |

5 |

|

|

AD7882 |

|

|

29 |

DVDD |

||||

CREF1 |

6 |

|

|

|

|

28 |

DGND |

||||||

Цифровая земля |

|

|

вид сверху |

|

|

||||||||

CREF2 |

7 |

|

|

|

|

27 |

DGND |

||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||

|

VREFIN |

8 |

|

|

|

|

|

|

|

|

|

26 |

DB10 |

|

VREFOUT |

9 |

|

|

|

|

|

|

|

|

|

25 |

DB9 |

|

AVDD |

10 |

|

|

|

|

|

|

|

|

|

24 |

DB8 |

Трехстабильные |

AVDD |

11 |

|

|

|

|

|

|

|

|

|

23 |

DB7 |

|

|

|

|

|

|

|

|

|

|

A1603C01 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

двунаправленные |

|

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

|

линии данных |

|

|

|||||||||||

|

SS |

SS |

1 |

2 |

DB0 |

DB1 |

DB2 |

DB3 |

DB4 |

DB5 |

DB6 |

|

|

|

|

IN |

IN |

|

|||||||||

|

|

AV |

AV |

A |

A |

|

|||||||

Публикуется с разрешения |

Лицензия на патенты или права Analog Devices |

157 |

фирмы Analog Devices |

не передаются ни косвенным, |

|

ни любым другим способом

16-РАЗРЯДНЫЙ АЦП С ВРЕМЕНЕМ ПРЕОБРАЗОВАНИЯ 2.5 мкс |

AD7882 |

собственный внутренний тактовый генератор, откалиброва нный в процессе изготовления при помощи лазера для гарантии точ ности и стабильности времени преобразования; может также использоваться внешний тактовый сигнал.

Еще одной особенностью AD7882 является режим с пониженным энергопотреблением (”дежурный” режим), в котором рассеив аемая ИС мощность снижается с 200 мВт (при нормальной работе) примерно до 1 мВт.

AD7882 работает от источников питания ±5 В. Диапазон входного аналогового сигнала может быть или униполярным: 0...2.5 В, или биполярным: ±2.5 В. Входная полоса частот для аналогового сигнала равна 200 кГц.

Помимо обычных статических параметров, таких как линейно сть, в спецификациях AD7882 полностью приводятся также и динамические параметры, в том числе THD и SNR.

AD7882 изготовлен по новейшей комбинированной технологии LC2MOS, которая позволяет совмещать на одном кристалле прецизионные биполярные схемы и быстродействующую KМОП-логику с низким энергопотреблением. AD7882 выпускается в 44-выводном корпусе PQFP и в 40-выводном керамическом корпусе типа CerDIP.

РЕЗЮМЕ _______________________________

1.Высокая производительность: минимальный интервал между отсчетами равен 2.5 мкс, что делает AD7882 пригодным для многих приложений, связанных с регистрацией данных.

2.Функция автокалибровки позволяет достичь высокой точно сти. Автокалибровка сводит к минимуму погрешности линейност и, смещения и усиления. В последовательность калибровки мож но также включить коррекцию внешних погрешностей смещения и усиления.

3.Динамические спецификации для DSP-приложений. Помимо традиционных статических параметров для AD7882 приводятся также и динамические параметры, включая SNR и THD. Эти параметры, а также важнейшие временные параметры, тестируются для каждой ИС.

4.Быстродействующий гибкий интерфейс с микропроцессорам и. AD7882 имеет малые времена доступа к шине и освобождения шины, а также стандартные управляющие сигналы, что упроща ет интерфейс AD7882 с микропроцессорами.

5.Исполнение AD7882 в виде монолитной ИС с низким энергопотреблением упрощает ее применение. AD7882 имеет также режим работы с пониженным энергопотреблением.

ЭЛЕKТРИЧЕСKИЕ ПАРАМЕТРЫ ______________________________________________________

ïðè AVDD = +5 Â ±5%, DVDD = +5 Â ±5%, AVSS = –5 Â ±5%, AGND = DGND = 0 Â, VREFIN= +2.5 Â, fCLKIN = 10 ÌÃö, fSAMPLE = 400 кГц, рабочий диапазон температур, если не указано иначе

Параметры |

Версия A, S |

Версия B,T |

Единицы |

|

Режим измерения / Примечания |

измерения |

|

||||

|

|

|

|

|

|

ДИНАМИЧЕСКИЕ ХАРАКТЕРИСТИКИ2 |

|

|

|

|

|

Отношение Сигнал/(Шум + Искажения) |

90 |

90 |

äÁ (ìèí.) |

|

AIN = 10 кГц, типичное SNR = 92 дБ |

|

85 |

85 |

äÁ (ìèí.) |

|

AIN = 100 кГц, типичноe SNR = 87 дБ |

|

|

|

|

|

|

Суммарный коэффициент гармоник (THD) |

–95 |

–95 |

äÁ (ìàêñ.) |

|

AIN = 10 кГц, типичное THD = –100 дБ |

|

|

|

|

|

|

|

–88 |

–88 |

äÁ (ìàêñ.) |

|

AIN = 100 кГц, типичное THD = –90 дБ |

Пиковая гармоника или паразитный шум |

–98 |

–98 |

äÁ (ìèí.) |

AIN |

= 10 кГц, типичная амплимтуда пиковой |

|

|

|

|

|

гармоники = –100 дБ |

|

–90 |

–90 |

äÁ (ìèí.) |

AIN |

= 100 кГц, типичная амплимтуда пиковой |

|

|

|

|

|

гармоники = –92 дБ |

Интермодуляционные искажения (IMD) |

|

|

|

|

|

|

|

|

|

|

|

Члены 2-го порядка |

–88 |

–88 |

äÁ (ìàêñ.) |

|

fA = 98 êÃö, fB = 100 êÃö |

|

|

|

|

|

|

Члены 3-го порядка |

–88 |

–88 |

äÁ (ìàêñ.) |

|

|

|

|

|

|

|

|

Минимальный интервал между отсчетами |

2.5 |

2.5 |

ìêñ (ìàêñ.) |

|

|

|

|

|

|

|

|

Апертурная задержка (от нарастающего фронта CONVST до момента |

10 |

10 |

íñ (òèï.) |

|

|

выборки) |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Апертурное дрожание (вариация апертурной задержки) |

20 |

20 |

ïñ (òèï.) |

|

|

Øóì |

70 |

70 |

ìê rms (òèï.) |

|

|

|

|

|

|

|

|

СТАТИЧЕСКАЯ ТОЧНОСТЬ |

|

|

|

|

|

Разрешение |

16 |

16 |

разряд |

|

|

|

|

|

|

|

|

Минимальное разрешение, для которого гарантируется отсу тствие |

16 |

16 |

разряд |

|

|

пропущенных кодов |

|

|

|||

|

|

|

|

|

|

Интегральная нелинейность |

±1/2 |

±1/2 |

ÌÇÐ (òèï.) |

|

|

|

|

|

|

|

|

Интегральная нелинейность |

|

±1.0 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

Дифференциальная нелинейность |

±0.9 |

±0.5 |

ÌÇÐ (ìàêñ.) |

|

|

Погрешность смещения в униполярном режиме |

±2 |

±2 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

Погрешность усиления в униполярном режиме |

±2 |

±2 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

Погрешность нуля в биполярном |

±2 |

±2 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

Погрешность усиления на верхнем конце шкалы в биполярном режиме |

±2 |

±2 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

Погрешность усиления на нижнем конце шкалы в биполярном р ежиме |

±2 |

±2 |

ÌÇÐ (ìàêñ.) |

|

|

|

|

|

|

|

|

ПОДАВЛЕНИЕ ПОМЕХИ ПО ПИТАНИЮ |

|

|

|

|

|

Только AVDD |

84 |

84 |

äÁ (òèï.) |

|

|

|

|

|

|

|

|

Только AVSS |

84 |

84 |

äÁ (òèï.) |

|

|

158 |

Публикуется с разрешения |

|

фирмы Analog Devices |

16-РАЗРЯДНЫЙ АЦП С ВРЕМЕНЕМ ПРЕОБРАЗОВАНИЯ 2.5 мкс |

AD7882 |

|

|

|||

ЭЛЕKТРИЧЕСKИЕ ПАРАМЕТРЫ (продолжение)__________________________________________ |

|

|||||

|

|

|

|

|

|

|

Параметры |

Версия A, S |

Версия B,T |

Единицы |

Режим измерения/Примечания |

|

|

измерения |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АНАЛОГОВЫЙ ВХОД |

|

|

|

|

|

|

|

|

|

|

|

|

|

Входной ток |

±1 |

±1 |

ìêÀ (ìàêñ.) |

Входной диапазон = 0 В...+2.5 В или ±2.5 В |

|

|

|

|

|

|

|

|

|

Входная емкость3 |

20 |

20 |

ïÔ (ìàêñ.) |

|

|

|

ВЫХОД ИСТОЧНИКА ОПОРНОГО НАПРЯЖЕНИЯ |

|

|

|

|

|

|

|

|

|

|

|

|

|

VREFOUT ïðè +25°Ñ |

2.5 |

2.5 |

|

±1% |

|

|

|

|

|

|

|

|

|

Температурный коэффициент VREFOUT |

20 |

20 |

ppm/°C (òèï.) |

|

|

|

|

|

|

|

|

|

|

ЛОГИЧЕСКИЕ ВХОДЫ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Уровень логической ”1”, VINH |

2.4 |

2.4 |

(ìèí.) |

|

|

|

|

|

|

|

|

|

|

Уровень логического ”0”, VINL |

0.8 |

0.8 |

(ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

Входной ток |

±10 |

±10 |

ìêÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

Входная емкость3 |

10 |

10 |

ïÔ (ìàêñ.) |

|

|

|

ÂÕÎÄ SLEEP |

|

|

|

|

|

|

|

|

|

|

|

|

|

Уровень логической ”1”, VINH |

VDD – 0.2 |

VDD – 0.2 |

(ìèí.) |

|

|

|

|

|

|

|

|

|

|

Уровень логического ”0”, VINL |

0.2 |

0.2 |

(ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

ÂÕÎÄ CLKIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Если на вход CLKIN подается более отрицательное |

|

|

Порог переключения |

–2 |

–2 |

(ìèí.) |

напряжение, то AD7882 переключается на |

|

|

|

|

|

|

внутренний тактовый генератор |

|

|

|

|

|

|

|

|

|

ЛОГИЧЕСКИЕ ВЫХОДЫ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Напряжение, соответствующее логической ”1” на выходе, VOH |

2.4 |

2.4 |

(ìèí.) |

ISOURCE = 200 ìêÀ |

|

|

|

|

|

|

|

|

|

Напряжение, соответствующее логическому ”0” на выходе, VOL |

0.4 |

0.4 |

(ìàêñ.) |

ISINK = 1.6 ìÀ |

|

|

|

|

|

|

|

|

|

DB15 – DB0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Ток утечки в высокоимпедансном состоянии |

±10 |

±10 |

ìêÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

Выходная емкость в высокоимпедансном состоянии |

20 |

20 |

ïÔ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

ПИТАНИЕ |

|

|

|

|

|

|

DVDD |

+5 |

+5 |

|

±5% |

|

1 |

|

|

|

|

|

|

|

AVDD |

+5 |

+5 |

|

±5% |

|

|

AVSS |

–5 |

–5 |

|

±5% |

|

|

|

|

|||||

|

|

|

|

|

|

|

Нормальный режим |

|

|

|

|

|

|

|

|

|

|

|

|

|

DIDD |

1 |

1 |

ìÀ (ìàêñ.) |

|

|

|

AIDD |

29 |

29 |

ìÀ (ìàêñ.) |

|

|

|

AISS |

27 |

27 |

ìÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

Энергопотребление |

300 |

300 |

ìÂò (ìàêñ.) |

Типичное значение 200 мВт, CLKIN остановлен |

|

|

|

|

|

|

|

|

|

Дежурный режим |

|

|

|

|

|

|

|

|

|

|

|

|

|

DIDD |

40 |

40 |

ìêÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

AIDD |

50 |

50 |

ìêÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

AISS |

40 |

40 |

ìêÀ (ìàêñ.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Типичное значение 500 мкВт, напряжения на |

|

|

Энергопотребление |

1 |

1 |

ìÂò (ìàêñ.) |

логических входах 0.2 В и VDD – 0.2 Â, |

|

|

|

|

|

|

CLKIN остановлен |

|

|

|

|

|

|

|

|

|

Примечания:

1.Температурные диапазоны: Модификации A, B: –40...+85°C; модификации S, :T–55...+125°C.

2.Значение после калибровки.