10.2 Исследование динамических характеристик логических элементов

Целью работы: является измерение времени задержки сигнала в логических элементах и определение зависимости тока питания ЛЭ от частоты входного сигнала.

Используемое оборудование и средства: макет, соединительные шнуры, осциллограф, функциональный генератор.

Методическое указание: работа выполняется студентами за два часа аудиторных занятий.

Краткие теоретические сведения

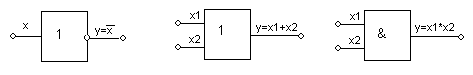

Логическими называют элементы, которые выполняют логические операции НЕ, И, ИЛИ. Обозначения логических элементов и их таблицы истинности приведены на рисунке 10.2.1.

а) б) в)

x1 |

x2 |

y |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

x1 |

x2 |

y |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

x |

y |

0 |

1 |

1 |

0 |

Рис. 10.2.1. Обозначения логических элементов НЕ (а), ИЛИ (б), И (в) и таблицы истинности к ним

Логический элемент И (рис. 10.2.1. в) реализует операцию логического умножения

(конъюнкции) y = x1Ùx2 или у = x1*x2 . Сигнал логической единицы появляется на выходе такой схемы только в том случае, если на все входы поданы сигналы, соответствующие единице.

Логический элемент ИЛИ (рис. 10.2.1. б) реализует функцию логического сложения: y = x1 + x2 или y = x1 Ú x2 .

Логический элемент НЕ (рис. 10.2.1. а) реализует функцию логического отрицания.

Сигнал, соответствующий единице на выходе устройства, появляется тогда, когда на входе подан сигнал логического нуля. В соответствии с выполняемой операцией инверсии элемент НЕ иногда называют инвертором, который реализует функцию

![]() .

.

Логические операции НЕ, И, ИЛИ могут быть выполнены с помощью универсальных логических элементов И-НЕ, ИЛИ-НЕ. Элемент ИЛИ-НЕ (рис. 10.2.2. а) осуществляет логическую операцию у = x1 + x2 =x1¯x2, называемую также стрелкой Пирса. Элемент И-НЕ (рис. 10.2.2. б) осуществляет логическую операцию у = x1*x2 = =x1x2, называемую штрихом Шеффера.

а) б)

x1 |

x2 |

Y |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

x1 |

x2 |

y |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Рис. 10.2.2. Обозначения элементов ИЛИ-НЕ (а) и И-НЕ (б) и таблицы истинности к ним

Конструктивно-технологическая реализация цифровых БИС во многом определяет их основные технические параметры – быстродействие, потребляемую мощность, устойчивость к внешним дестабилизирующим факторам.

Различают следующие основные виды (типы) конструктивно-технологического исполнения БИС: биполярные БИС, БИС на основе МОП транзисторов, БИС на основе комбинированной биполярно-комплементарной (БиКМОП) технологии.

БИС на основе р-МОП обладают самой низкой стоимостью, однако имеют невысокие быстродействие и нагрузочную способность, не сопрягаются со стандартными ТТЛ-микросхемами.

БИС на основе n-МОП характеризуются высокой степенью интеграции и быстродействием, однако обладают низкой нагрузочной способностью при сравнительно высокой потребляемой мощности, хотя могут сопрягаться с ТТЛ-микросхемами. БИС на основе КМОП-транзисторов обладают высоким быстродействием, очень низкой потребляемой мощностью и высокой помехоустойчивостью, сопрягаются со стандартными ТТЛ-микросхемами.

Биполярные БИС отличаются от МОП БИС более высокими быстродействием, потребляемой мощностью и нагрузочной способностью, повышенной устойчивостью к дестабилизирующим факторам.

Цифровые БИС на основе ЭСЛ-технологии (эмиттерно-связанной технологии) отличаются сверхвысоким быстродействием, однако обладают высокой потребляемой мощностью, требуют специальных внешних схем для сопряжения БИС других типов.

Цифровые БИС на основе интегральной инжекционной логики (И2Л) характеризуются самой высокой степенью интеграции, низкой потребляемой мощностью, высоким быстродействием, сопрягаются с другими типами БИС. Цифровые БИС на основе технологии транзисторно-транзисторной логики с диодами Шоттки (ТТЛШ) обладают более низким по сравнению с ЭСЛ БИС быстродействием, однако рассеивают меньшую мощность, обеспечивая высокие характеристики нагрузочной способности, помехоустойчивости.

БиКМОП БИС имеют лучшие черты биполярных (высокое быстродействие и нагрузочную способность) и КМОП БИС (низкая потребляемая мощность и высокая помехоустойчивость).

Различают статические и динамические характеристики ЛЭ. Первые снимаются в установившемся режиме, вторые - в переходном. С помощью снятых характеристик определяют следующие основные параметры элементов: нагрузочную способность, помехоустойчивость, быстродействие, величины U0 и U1, потребляемую мощность и т.п.

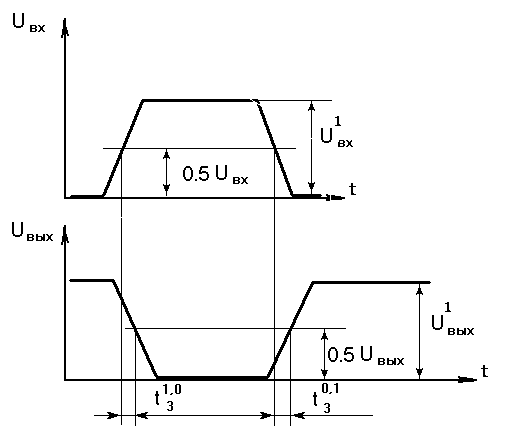

К динамическим характеристикам относятся задержки положительного и отрицательного фронтов выходного сигнала логического элемента относительно входного, а также зависимость тока питания ЛЭ от частоты входного сигнала.

Быстродействие ЛЭ характеризуется скоростью перехода из одного состояния в другое. В общем случае скорость перехода элемента из состояния «О» в состояние «1» не равна скорости перехода в обратное состояние. Длительность задержек и фронтов выходных сигналов зависит от быстродействия элемента. Более быстродействующие элементы имеют меньшую длительность задержек и фронтов.

Для практики наибольшее значение имеет время задержки. Для упрощения расчётов принимают среднее время задержки равным полусумме времён задержек при переходе из «1» в «О» и обратно. Оценка быстродействия производится по осциллограммам входных и выходных сигналов исследуемого элемента.

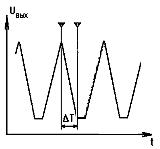

Рис. 10.2.3. Определение длительности задержек инвертора по осциллограммам при переключении элемента из «1» в «О» и обратно

Под временем задержки при включении логического элемента t103 понимают интервал времени между входным и выходным импульсами при переходе выходного напряжения от уровня логической единицы к уровню логического нуля, измеренный на уровне 0.5 амплитуды сигнала.

Временем задержки сигнала при выключении t013 считают интервал времени между входным и выходным импульсами при переходе выходного напряжения от уровня логического нуля к уровню логической единицы, измеренный на уровне 0.5 амплитуды сигнала.

Средним временем задержки сигнала называют интервал времени, равный полусумме времён задержки при включении и выключении логического элемента:

![]()

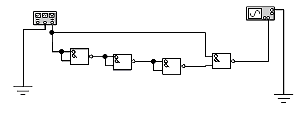

а) б)

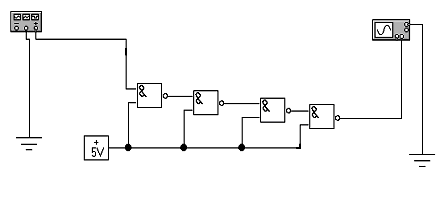

Рис. 10.2.4. Схема (а) и осциллограмма (б) для определения времени задержки последовательно соединенных ЛЭ

Так как это время достаточно мало, то обычно измеряют суммарное время переключения для нескольких одинаковых элементов, а затем пересчитывают его для одного элемента.

Схема для определения времени задержки ЛЭ показана на рис. 10.2.4, а. Эксперимент проводится с четырьмя последовательно соединёнными элементами 2И-НЕ модели К561ЛА7.

Здесь элемент 4 служит для выделения в форме импульса суммарного времени задержки переключения элементов 1, 2 и 3. При подаче на первый вход 4-го элемента прямоугольного импульса в момент появления на входе логической единицы на втором входе элемента 4 за счёт задержек прохождения сигнала по элементам 1-3 некоторое время сохраняется также логическая единица. В этот интервал времени на выходе элемента 4 формируется логический нуль. По окончании переходных процессов на выходе элемента 3 формируется напряжение нуля, а с выхода элемента 4 будем снимать высокий уровень. Длительность выходного отрицательного импульса практически не зависит от задержки, вносимой элементом 4, так как задержки для положительных и отрицательных фронтов примерно одинаковы.

Измеренное с помощью осциллографа суммарное время задержки DT необходимо разделить на удвоенное количество ЛЭ в цепочке. В результате операции деления получим величину задержки одного фронта импульса. Испытание следует проводить во всём диапазоне частот. Вид суммарного времени задержки для трёх ЛЭ в виде отрицательного импульса с экрана осциллографа на частоте 500 кГц изображён на рис. 10.2.4, б.

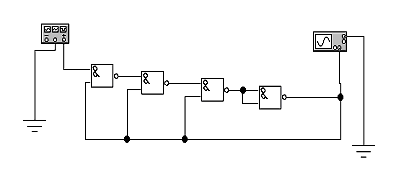

а) б)

Рис. 10.2.5. Схема (а) и осциллограмма (б) для определения времени задержки ЛЭ

а) б)

Рис. 10.2.6. Схема (а) и осциллограмма (б) для определения времени задержки последовательно соединенных ЛЭ

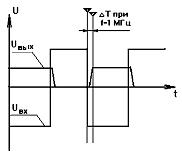

На рис. 10.2.5, а приведён второй вариант схемы для определения времени задержки логического элемента. Схема генерирует импульсы, период которых пропорционален суммарному времени задержки всех фронтов входящих в цепочку ЛЭ. Измерив с помощью осциллографа период колебаний и разделив его на удвоенное число ЛЭ в схеме, получим время задержки одного фронта. График изменения выходного напряжения схемы на экране осциллографа показан на рис. 10.2.5, б. Напряжение по оси ординат указано в вольтах. В качестве ЛЭ здесь так же необходимо использовать элементы модели К561ЛА7.

На рис.6, а приведена схема содержащая п последовательно соединённых элементов 2И-НЕ. На первый вход первого ЛЭ подаётся прямоугольный сигнал с генератора, который затем последовательно проходит через все остальные элементы цепочки. На вторые входы ЛЭ подаётся логическая "1". График выходных напряжений с экрана осциллографа приведён на рис. 10.2.6, б. Разделив временной интервал ∆Т на удвоенное количество ЛЭ в цепочке, получим время задержки одного фронта импульса. В качестве элементов следует брать ЛЭ модели К561ЛА7.

Рис. 10.2.7. Схема КМОП-инвектора

При переключении транзисторов в схемах возникает дополнительное потребление мощности, обусловленное перезарядом внутренних ёмкостей и наличием в промежуточном состоянии сквозных токов. На рис. 10.2.7 приведена схема, позволяющая обнаружить и измерить дополнительный ток по цепям питания КМОП-инвертора, возникающий при повышенной частоте работы управляющего генератора. Обычно снимается зависимость потребляемого по цепям питания тока от частоты переключения, а затем пересчитывают эту зависимость на мощность. В качестве VTI и VT2 используются транзисторы модели К561ЛА7.