- •Матью Мэндл

- •200 Избранных схем электроники Редакция литературы по информатике и электронике

- •© Перевод на русский язык, «Мир», 1985, 1980 предисловие редактора перевода

- •Предисловие

- •Глава 1 усилители звуковой частоты и видеоусилители

- •1.1. Усилители с общим эмиттером и общим истоком

- •1.2. Усилители с общей базой и общим затвором

- •3.3. Усилители с общим коллектором и общим стоком

- •1.4. Классификация усилителей

- •1.5. Типы связи между каскадами

- •1.6. Цепи развязки

- •1.7. Регуляторы тембра

- •1.8. Отрицательная обратная связь

- •1.9. Видеоусилители

- •1.10. Фазоинверторы

- •1.11. Двухтактные усилители

- •Усилители специального назначения

- •2.1. Схема Дарлингтона

- •2.2. Операционные усилители

- •2.3. Дифференциальные усилители

- •2.4. Усилитель сигнала выключения канала цветности

- •2.5. Полосовой усилитель сигналов цветности

- •2.6. Усилитель сигналов цветности

- •2.7. Схема стробирования цветовой вспышки

- •2.8. Магнитные усилители

- •2.9. Магнитный усилитель с самонасыщением

- •2.10. Двухтактный магнитный усилитель

- •2.11. Выходные усилители блоков кадровой и строчной разверток

- •2.12. Усилитель чм-пилот-сигнала

- •Глава 3 усилители промежуточной и высокой частоты

- •3.1. Принципиальная схема упч

- •3.2. Заграждающие фильтры входного каскада упч

- •3.3. Каскады упч на полевых транзисторах

- •3.5. Линейный усилитель класса в

- •3.6. Однотактный усилитель класса с

- •3.7. Двухтактный усилитель класса с

- •3.8. Умножители частоты

- •Глава 4 генераторы

- •4.1. Генератор по схеме Армстронга

- •4.2. Генератор с регулируемой частотой

- •4.3. Генератор по схеме Хартли

- •4.4. Генератор по схеме Колпитса

- •4.5. Кварцованный генератор

- •4.6. Генератор поднесущей с фапч

- •4.7. Мультивибратор

- •4.8. Мультивибратор кадровой развертки

- •4.9. Блокинг-генератор

- •4.10. Блокииг-генератор кадровой развертки

- •4.11. Блокинг-генератор строчной развертки

- •Глава 5 фильтры и аттенюаторы (ослабители)

- •5.1. Общие положения

- •5.2. Фильтры нижних частот типа k

- •5.3. Фильтры нижних частот типа m

- •5.4. Фильтры верхних частот типа k

- •5.5. Фильтры верхних частот типа т

- •5.6. Сбалансированные фильтры

- •5.7. Полосовые фильтры

- •5.8. Заграждающие фильтры

- •5.9. Аттенюаторы (ослабители)

- •5.10. Типы переменных аттенюаторов

- •5.11. Типы постоянных аттенюаторов

- •5.15. Мостовые т- и н-образные аттенюаторы

- •5.16. Фильтр частичного подавления одной боковой полосы

- •Глава 6 модуляционные устройства

- •6.1. Основные виды модуляции

- •6.2. Режим однотактной am

- •6.3. Режим двухтактной am

- •6.4. Ширина полосы чм

- •6.5. Коэффициенты частотной модуляции

- •6.6. Обеспечение стабильности частоты несущей при чм

- •6.7. Балансный модулятор

- •6.8. Предварительная коррекция

- •6.9. Ввод импульсов синхронизации в состав телевизионного сигнала

- •6.10. Ввод кадровых синхроимпульсов

- •6.11. Схемы объединения сигналов

- •Глава 7 демодуляторы и схемы арг, ару и другие

- •7.1. Детектор ам-сигналов

- •7.2. Регенеративный детектор

- •7.3. Фазовый детектор

- •7.4. Дискриминатор чм-сигналов

- •7.5. Детектор отношений чм-сигналов

- •7.6. Схема ослабления звуковых сигналов более высоких частот

- •7.7. Видеодетектор

- •7.8. Автоматическая регулировка громкости

- •7.9. Основная схема ару

- •7.10. Ключевая схема ару

- •7.11. Автоматическая подстройка частоты

- •7.12. Автоматическая регулировка усиления сигналов цветности

- •7.13. Демодулятор цветоразностных сигналов в — y и r — y

- •Глава 8 цифровые схемы

- •8.1. Общие положения

- •8.2. Статический триггер

- •8.3. Схема или

- •8.4. Схемы или-не, и, и-не

- •8.5. Сложные логические схемы

- •8.6. Резисторно-транзисторные и диодно-транзисторные логические схемы

- •8.7. Логика с непосредственными связями

- •6.8. Схема исключающее или

- •8.9. Представление двоичного числа в прямом hi обратном кодах

- •Глава 9 мостовые схемы

- •9.1. Мостик Уитстона

- •9.2. L и с-мостики Уитстона

- •9.3. Мост Овена

- •9.4. Мост Максвелла

- •9.5. Мост Вина

- •9.6. Резонансный мост

- •9.7. Мост Хея

- •9.8. Мост Шеринга

- •9.9. Детектор мостового типа

- •9.10. Мостовой выпрямитель

- •9.11. Мостовой фазовый детектор

- •9.12. Мостовой антенный переключатель

- •Глава 10 источники питания и схемы управления

- •10.1. Общие сведеяшя об источниках питания

- •10.2. Однополупериодный выпрямитель

- •10.3. Двухполупериодный выпрямитель

- •10.4. Удвоитель напряжения

- •10.5. Утроитель напряжения

- •10.6. Высоковольтные схемы

- •10.7. Мостовой выпрямитель

- •10.8. Стабилизаторы напряжения

- •10.9. Прерыватели hi преобразователи

- •10.10. Схемы с регулируемым напряжением

- •10.11. Схема с тиристорами

- •10.12. Фазосдвигающая цепь

- •10.13. Схема с игнитроном

- •10.14. Двухполупериодная схема с игнитронами

- •Глава 11 цепи преобразования формы сигналов

- •11.1. Интегрирующая цепь

- •11.2. Дифференцирующая цепь

- •11.3. Интегрирующе-дифференцирующая цепь

- •11.4. Последовательный диодный ограничитель

- •11.5. Параллельный диодный ограничитель

- •11.6. Двусторонний ограничитель

- •11.7. Выравнивание амплитуд

- •11.8. Схемы фиксации уровня

- •11.9. Формирование пилообразных сигналов

- •11.10 Преобразование пилообразного напряжения в пилообразный ток

- •Глава 12 реактансные схемы

- •12.1. Основная схема с управляемым реактивным сопротивлением

- •12.2. Реактансная схема rс-типа

- •12.3. Реактансная схема rl-типа.

- •12.4. Схема подстройки с двумя варакторами

- •12.5. Схема с одним варактором

- •Глава 13 специальные устройства и системы

- •13.1. Делитель частоты на блокинг-генераторе

- •13.2. Делитель частоты накопительного типа

- •13.3. Удвоитель частоты

- •13.4. Одностабильный мультивибратор

- •13.5. Триггер Шмитта

- •13.6. Селектор синхроимпульсов

- •13.7. Индикатор настройки

- •13.8. Система переключения рода работы магнитофона

- •13.9. Схема гашения

- •13.10 Система переключения am- и чм-сигналов в стереоприемнике

- •13.11. Системы управления

- •13.12 Сельсины

- •13.13. Дифференциальные сельсины

- •13.14. Электромашинный усилитель — амплидин

- •13.15. Схемы с фотоэлементами

- •13.16. Основные измерительные схемы

- •Глава 14 интегральные схемы

- •14.1. Особенности интегральных схем

- •14.2. Применение интегральных схем в модулях

- •14.3. Многоэмиттерные транзисторы в схемах ттл-типа

- •14.4. Интегральные схемы с дополняющими моп-транзисторами

- •14.5. Логические схемы инжекционного типа

- •14.6. Схема вентиля или-не инжекционного типа

- •14.7. Схема фиксации с диодами Шоттки

- •Глава 15 функциональные схемы передающих и приемных устройств

- •15.1. Передатчик ам-сигналов

- •15.2. Одноканальный передатчик с чм

- •15.3. Многоканальный передатчик с чм

- •15.4. Телевизионный передатчик

- •15.5. Приемник ам-сигналов

- •15.6. Одноканальный приемник чм-сигналов

- •15.7. Многоканальный приемник чм-сигналов

- •15.8. Телевизионный приемник

- •Глава 1. Усилители звуковой частоты и видеоусилители

- •Глава 2. Усилители специального назначения

- •Глава 3. Усилители промежуточной и высокой частоты

- •Глава 4. Генераторы

- •Глава 5. Фильтры и аттенюаторы (ослабители)

- •Глава 6. Модуляционные устройства

- •Глава 7. Демодуляторы и схемы арг, ару и другие

- •Глава 8. Цифровые схемы

- •Глава 9. Мостовые схемы

- •Глава 10. Источники питания и схемы управления

- •Глава 11. Цепи преобразования формы сигналов

- •Глава 12. Реактансные схемы

- •Глава 13. Специальные устройства и системы

- •Глава 14. Интегральные схемы

- •Глава 15. Функциональные схемы передающих и приемных устройств

- •200 Избранных схем электроники

8.7. Логика с непосредственными связями

Для упрощения логической схемы с многими входами транзисторы иногда включают непосредственным образом (рис. 8.7, а). Такую логику называют непосредственно-связанной диодно-транзисторной логики (ДТЛ).

Обратите внимание на параллельное включение транзисторов. Схема с такой параллельной конфигурацией выполняет функцию ИЛИ-НЕ (рис. 8.7,6). Сигнал на входе одной или нескольких баз транзисторов левой группы отпирает соответствующие транзисторы, поскольку импульс положительной полярности создает прямое смещение n — р — n-транзистора. Когда один (или несколько) из этих транзисторов отпирается и входит в насыщенное состояние, на выходе образуется практически короткое замыкание вследствие очень малого полного сопротивления насыщенного транзистора. В этом случае падение напряжения на резисторе R1 равно напряжению источника, а коллекторы оказываются под потенциалом земли. Поэтому к базам последующих транзисторов двух раздельных схем ИЛИ прикладывается нулевое напряжение, вследствие чего эти транзисторы не отпираются. При отсутствии положительных сигналов на базах всех остальных транзисторов эти транзисторы оказываются запертыми. В этом случае падения напряжений на резисторах R2 и Rз практически равны нулю и напряжения сигналов на выходах 1 и 2 равны напряжениям источников питания, причем их полярность совпадает с полярностью входного сигнала. Это объясняется инвертированием сигналов схемами ИЛИ, поскольку здесь используются транзисторы, включенные по схеме с общим эмиттером. Поэтому, как показано на рис. 8.7,6, выходной импульс первой схемы ИЛИ имеет отрицательную полярность (точнее, его величина почти равна нулю). Когда этот сигнал поступает на входы последующих схем ИЛИ, он вновь инвертируется, так что полярность и форма сигналов на выходе соответствуют полярности и форме исходного сигнала.

Рис. 8.7. Логическая схема с непосредственными связями.

Если хотя бы на один из других входов схем ИЛИ, расположенных справа на рисунке, подать сигналы положительной полярности, то на выходах этих схем сигналы будут иметь обратную полярность (точнее, выходные сигналы будут практически равны нулю), поскольку они повторно не инвертируются.

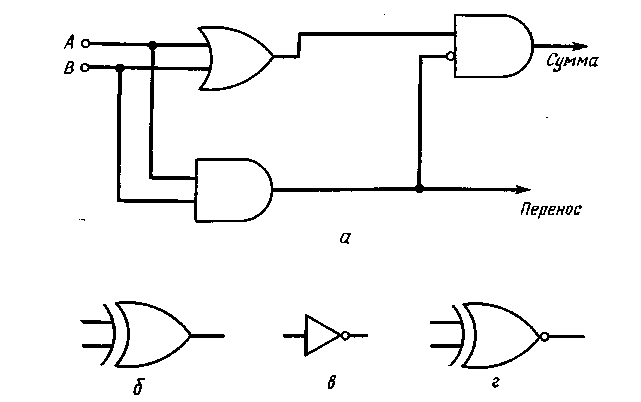

6.8. Схема исключающее или

Для вентилей И, И-НЕ и др. удобно использовать символы, поскольку они позволяют более наглядно представлять входные и выходные логические сигналы и рабочие характеристики таких вентилей. Поэтому, хотя и известны различные способы реализации схемы ИЛИ (на диодах, резисторах и диодах, на транзисторах), для их обозначения используется один символ.

Иногда используемую комбинацию логических схем можно представить одним символом, определяющим все свойства комбинированной сложной схемы, что делает ненужным изображение четырех, пяти или даже большего числа символических обозначений отдельных схем, применяемых для реализации некоторой операции. Примером может служить полусумматор, схема которого показана на рис. 8.8. По существу полусумматор состоит из схемы ИЛИ и двух схем И, одна из которых имеет инвертированный вход. Последняя схема является схемой ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (ЗАПРЕТ). Эти три логические схемы связаны между собой, как показано на рис. 8.8, а, хотя для индикации комбинации схем И и ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, но без выхода для цифры переноса часто используют один символ, изображенный на рис. 8.8, б. Этот символ соответствует схеме ИСКЛЮЧАЮЩЕЕ ИЛИ [Эта логическая схема известна под названием схемы неравнозначности или двухвходовой суммы суммирования по модулю 2. — Прим. ред.]. Если после схемы, показанной на рис. 8.8,6, следует инвертор (рис. 8.8, в), то получаем схему ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (схема эквивалентности или равнозначности), символ которой изображен на рис.8.8,г.

Полные сумматоры (последовательного типа) могут быть получены путем использования двух полусумматоров, показанных на рис. 8.8, а. Полусумматоры применяются также для целей переключений и для преобразования кодов.

Рис. 8.8. Полусумматор (а) и условные обозначения схем ИСКЛЮЧАЮЩЕЕ ИЛИ (б), НЕ (в) и ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (г).

Если на .входы схемы ИЛИ поступают два импульса, то они одновременно появятся и на схеме И. Тогда на выходе этой схемы И возникает импульс, который поступает на вход схемы ЗАПРЕТ и закрывает эту схему, препятствуя вводу сигналов от схемы ИЛИ. Следовательно, логика работы данной схемы такова: когда на обоих входах схемы ИЛИ действуют 1, то на выходе «Сумма» появляется 0, а на выходе «Перенос» — 1.

Таблица 8.5

А |

в |

Сумма |

Перенос |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

При подаче импульса только на один какой-нибудь вход схемы ИЛИ импульс запрета не формируется. В этом случае импульс, соответствующий 1, образуется только на выходе «Сумма». Выполняемая логическая операция соответствует правилу двоичного сложения 1 + 1 = 10 (двоичное число два). Поэтому, если на входах А и В действуют единичные сигналы, то выходной сигнал на выходе «Сумма» соответствует 0 (импульс отсутствует), но возникает импульс переноса на выходе «Перенос» представляемый 1 старшего разряда в двоичном числе 10.

Рис. 8.9. Преобразователь кода Грея в двоичный код.

На основе описания данной логической схемы может быть составлена таблица истинности (табл. 8.5), иллюстрирующая операции, выполняемые схемой (полусумматором).

Комбинацию схем ИСКЛЮЧАЮЩЕЕ ИЛИ можно использовать для преобразования кода Грея в двоичный код (рис. 8.9). Код Грея называют также циклическим кодом или кодом с минимальными ошибками. Код Грея широко применяется в вычислительных и управляющих системах, поскольку при этом уменьшаются случайные ошибки в дроцессе работы. Это объясняется тем, что по мере возрастания чисел в коде Грея в некоторый момент времени изменяется только одна цифра. В двоичном коде это не так (табл. 8.6).

В преобразователе, показанном на рис. 8.9, количество логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ равно количеству разрядов преобразуемых чисел. Предположим, что слева в схему вводится число в коде Грея 1010 (01010). [Заметим, что на выходах схем сигнала переноса не образуется (1 + 1=0).] Нуль, цо-ступающий на верхний вход схемы А, передается и на выход, поскольку вход непосредственно соединен с выходом. При подаче 1 на нижний вход схемы А на выходе этой схемы также формируется 1. Но выход этой схемы связан с входом схемы В. Поскольку на нижний вход схемы В сигнал не поступает (подается сигнал, соответствующий нулю), на выходе формируется 1. Эта 1 подается на верхний вход схемы С и так как на нижний вход этой схемы также поступает 1, то на ее выходе получаем 0. Аналогично этому, поскольку на входы схемы D сигналы не поступают (подаются нули) , то на выходе также получается 0. Таким образом, число 1010 в коде Грея преобразуется в двоичное число 1100 (табл. 8.6).

Таблица 8.6

Десятичное число |

Двоичный код |

Код Грея |

0 |

0000 |

0000 |

1 |

0001 |

0001 |

2 |

0010 |

0011 |

3 |

0011 |

0010 |

4 |

0100 |

0110 |

5 |

0101 |

0111 |

6 |

0110 |

0101 |

7 |

0111 |

0100 |

8 |

1000 |

1100 |

9 |

1001 |

1101 |

10 |

1010 |

1111 |

11 |

1011 |

1110 |

12 |

1100 |

1010 |

Рис. 8.10. Схема считывания двоичного числа в прямом и обратном кодах.