- •Матью Мэндл

- •200 Избранных схем электроники Редакция литературы по информатике и электронике

- •© Перевод на русский язык, «Мир», 1985, 1980 предисловие редактора перевода

- •Предисловие

- •Глава 1 усилители звуковой частоты и видеоусилители

- •1.1. Усилители с общим эмиттером и общим истоком

- •1.2. Усилители с общей базой и общим затвором

- •3.3. Усилители с общим коллектором и общим стоком

- •1.4. Классификация усилителей

- •1.5. Типы связи между каскадами

- •1.6. Цепи развязки

- •1.7. Регуляторы тембра

- •1.8. Отрицательная обратная связь

- •1.9. Видеоусилители

- •1.10. Фазоинверторы

- •1.11. Двухтактные усилители

- •Усилители специального назначения

- •2.1. Схема Дарлингтона

- •2.2. Операционные усилители

- •2.3. Дифференциальные усилители

- •2.4. Усилитель сигнала выключения канала цветности

- •2.5. Полосовой усилитель сигналов цветности

- •2.6. Усилитель сигналов цветности

- •2.7. Схема стробирования цветовой вспышки

- •2.8. Магнитные усилители

- •2.9. Магнитный усилитель с самонасыщением

- •2.10. Двухтактный магнитный усилитель

- •2.11. Выходные усилители блоков кадровой и строчной разверток

- •2.12. Усилитель чм-пилот-сигнала

- •Глава 3 усилители промежуточной и высокой частоты

- •3.1. Принципиальная схема упч

- •3.2. Заграждающие фильтры входного каскада упч

- •3.3. Каскады упч на полевых транзисторах

- •3.5. Линейный усилитель класса в

- •3.6. Однотактный усилитель класса с

- •3.7. Двухтактный усилитель класса с

- •3.8. Умножители частоты

- •Глава 4 генераторы

- •4.1. Генератор по схеме Армстронга

- •4.2. Генератор с регулируемой частотой

- •4.3. Генератор по схеме Хартли

- •4.4. Генератор по схеме Колпитса

- •4.5. Кварцованный генератор

- •4.6. Генератор поднесущей с фапч

- •4.7. Мультивибратор

- •4.8. Мультивибратор кадровой развертки

- •4.9. Блокинг-генератор

- •4.10. Блокииг-генератор кадровой развертки

- •4.11. Блокинг-генератор строчной развертки

- •Глава 5 фильтры и аттенюаторы (ослабители)

- •5.1. Общие положения

- •5.2. Фильтры нижних частот типа k

- •5.3. Фильтры нижних частот типа m

- •5.4. Фильтры верхних частот типа k

- •5.5. Фильтры верхних частот типа т

- •5.6. Сбалансированные фильтры

- •5.7. Полосовые фильтры

- •5.8. Заграждающие фильтры

- •5.9. Аттенюаторы (ослабители)

- •5.10. Типы переменных аттенюаторов

- •5.11. Типы постоянных аттенюаторов

- •5.15. Мостовые т- и н-образные аттенюаторы

- •5.16. Фильтр частичного подавления одной боковой полосы

- •Глава 6 модуляционные устройства

- •6.1. Основные виды модуляции

- •6.2. Режим однотактной am

- •6.3. Режим двухтактной am

- •6.4. Ширина полосы чм

- •6.5. Коэффициенты частотной модуляции

- •6.6. Обеспечение стабильности частоты несущей при чм

- •6.7. Балансный модулятор

- •6.8. Предварительная коррекция

- •6.9. Ввод импульсов синхронизации в состав телевизионного сигнала

- •6.10. Ввод кадровых синхроимпульсов

- •6.11. Схемы объединения сигналов

- •Глава 7 демодуляторы и схемы арг, ару и другие

- •7.1. Детектор ам-сигналов

- •7.2. Регенеративный детектор

- •7.3. Фазовый детектор

- •7.4. Дискриминатор чм-сигналов

- •7.5. Детектор отношений чм-сигналов

- •7.6. Схема ослабления звуковых сигналов более высоких частот

- •7.7. Видеодетектор

- •7.8. Автоматическая регулировка громкости

- •7.9. Основная схема ару

- •7.10. Ключевая схема ару

- •7.11. Автоматическая подстройка частоты

- •7.12. Автоматическая регулировка усиления сигналов цветности

- •7.13. Демодулятор цветоразностных сигналов в — y и r — y

- •Глава 8 цифровые схемы

- •8.1. Общие положения

- •8.2. Статический триггер

- •8.3. Схема или

- •8.4. Схемы или-не, и, и-не

- •8.5. Сложные логические схемы

- •8.6. Резисторно-транзисторные и диодно-транзисторные логические схемы

- •8.7. Логика с непосредственными связями

- •6.8. Схема исключающее или

- •8.9. Представление двоичного числа в прямом hi обратном кодах

- •Глава 9 мостовые схемы

- •9.1. Мостик Уитстона

- •9.2. L и с-мостики Уитстона

- •9.3. Мост Овена

- •9.4. Мост Максвелла

- •9.5. Мост Вина

- •9.6. Резонансный мост

- •9.7. Мост Хея

- •9.8. Мост Шеринга

- •9.9. Детектор мостового типа

- •9.10. Мостовой выпрямитель

- •9.11. Мостовой фазовый детектор

- •9.12. Мостовой антенный переключатель

- •Глава 10 источники питания и схемы управления

- •10.1. Общие сведеяшя об источниках питания

- •10.2. Однополупериодный выпрямитель

- •10.3. Двухполупериодный выпрямитель

- •10.4. Удвоитель напряжения

- •10.5. Утроитель напряжения

- •10.6. Высоковольтные схемы

- •10.7. Мостовой выпрямитель

- •10.8. Стабилизаторы напряжения

- •10.9. Прерыватели hi преобразователи

- •10.10. Схемы с регулируемым напряжением

- •10.11. Схема с тиристорами

- •10.12. Фазосдвигающая цепь

- •10.13. Схема с игнитроном

- •10.14. Двухполупериодная схема с игнитронами

- •Глава 11 цепи преобразования формы сигналов

- •11.1. Интегрирующая цепь

- •11.2. Дифференцирующая цепь

- •11.3. Интегрирующе-дифференцирующая цепь

- •11.4. Последовательный диодный ограничитель

- •11.5. Параллельный диодный ограничитель

- •11.6. Двусторонний ограничитель

- •11.7. Выравнивание амплитуд

- •11.8. Схемы фиксации уровня

- •11.9. Формирование пилообразных сигналов

- •11.10 Преобразование пилообразного напряжения в пилообразный ток

- •Глава 12 реактансные схемы

- •12.1. Основная схема с управляемым реактивным сопротивлением

- •12.2. Реактансная схема rс-типа

- •12.3. Реактансная схема rl-типа.

- •12.4. Схема подстройки с двумя варакторами

- •12.5. Схема с одним варактором

- •Глава 13 специальные устройства и системы

- •13.1. Делитель частоты на блокинг-генераторе

- •13.2. Делитель частоты накопительного типа

- •13.3. Удвоитель частоты

- •13.4. Одностабильный мультивибратор

- •13.5. Триггер Шмитта

- •13.6. Селектор синхроимпульсов

- •13.7. Индикатор настройки

- •13.8. Система переключения рода работы магнитофона

- •13.9. Схема гашения

- •13.10 Система переключения am- и чм-сигналов в стереоприемнике

- •13.11. Системы управления

- •13.12 Сельсины

- •13.13. Дифференциальные сельсины

- •13.14. Электромашинный усилитель — амплидин

- •13.15. Схемы с фотоэлементами

- •13.16. Основные измерительные схемы

- •Глава 14 интегральные схемы

- •14.1. Особенности интегральных схем

- •14.2. Применение интегральных схем в модулях

- •14.3. Многоэмиттерные транзисторы в схемах ттл-типа

- •14.4. Интегральные схемы с дополняющими моп-транзисторами

- •14.5. Логические схемы инжекционного типа

- •14.6. Схема вентиля или-не инжекционного типа

- •14.7. Схема фиксации с диодами Шоттки

- •Глава 15 функциональные схемы передающих и приемных устройств

- •15.1. Передатчик ам-сигналов

- •15.2. Одноканальный передатчик с чм

- •15.3. Многоканальный передатчик с чм

- •15.4. Телевизионный передатчик

- •15.5. Приемник ам-сигналов

- •15.6. Одноканальный приемник чм-сигналов

- •15.7. Многоканальный приемник чм-сигналов

- •15.8. Телевизионный приемник

- •Глава 1. Усилители звуковой частоты и видеоусилители

- •Глава 2. Усилители специального назначения

- •Глава 3. Усилители промежуточной и высокой частоты

- •Глава 4. Генераторы

- •Глава 5. Фильтры и аттенюаторы (ослабители)

- •Глава 6. Модуляционные устройства

- •Глава 7. Демодуляторы и схемы арг, ару и другие

- •Глава 8. Цифровые схемы

- •Глава 9. Мостовые схемы

- •Глава 10. Источники питания и схемы управления

- •Глава 11. Цепи преобразования формы сигналов

- •Глава 12. Реактансные схемы

- •Глава 13. Специальные устройства и системы

- •Глава 14. Интегральные схемы

- •Глава 15. Функциональные схемы передающих и приемных устройств

- •200 Избранных схем электроники

8.3. Схема или

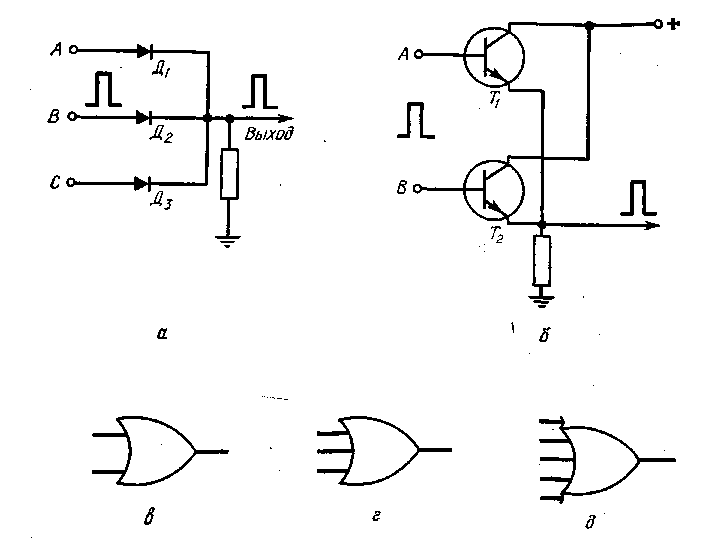

Логической схемой ИЛИ называется схема с одним выходом и любым числом входов, когда выходной сигнал образуется в результате .воздействия входного сигнала иа один или несколько входов схемы. На рис. 8.2, а показана типичная схема (вентиль) ИЛИ, выполненная на диодах. На схеме изображены три входа, хотя можно использовать только два входа или же добавить другие входы. Такой вентиль ИЛИ не нуждается в источнике питания, поскольку для обеспечения проводимости диодов подаются входные сигналы соответствующей полярности.

Когда к входу A прикладывается положительное (по отношению к земле) напряжение или импульс, диод Д] становится проводящим. Возникающий при этом ток создает на резисторе падение напряжения, представляющее выходной сигнал. Таким образом, при подаче импульса на вход А возникает выходной-импульс. Такой же результат получается при подаче импульса на вход В или С. Если импульсы напряжения; одинаковой высоты приложены к двум или трем входам одновременно, выходной сигнал практически не отличается от рассмотренного. Таким образом, один и тот же выходной сигнал образуется при воздействии сигнала на вход Л, ИЛИ на вход В, ИЛИ на вход С, ИЛИ на два, ИЛИ на все три входа. Вместо использования положительного сигнала (импульса), соответствующего логической единице, или логическому высказыванию ИСТИНА, может использоваться импульс отрицательной полярности. В этом случае диоды, показанные на рис. 8.2, а, должны быть включены в обратном направлении. (Если для представления логической 1 выбраны положительные сигналы, то сигналы отрицательной полярности, а также состояние отсутствия сигнала представляются 0. Аналогично этому использование логической 1 для отрицательных сигналов означает соответствие 0 положительных сигналов, а также состояния отсутствия сигнала.)

Рис. 8.2. Схемы ИЛИ и их условные обозначения.

На рис. 8.2,6 показана схема ИЛИ, реализованная на транзисторах, включенных с объединенным эмиттером. Для увеличения числа входов можно использовать три или более транзистора. На оба коллектора подается положительное напряжение, создающее обратное смещение коллекторных переходов. При отсутствии входных сигналов транзисторы практически заперты и выходной сигнал отсутствует. Однако, когда к входу А прикладывается импульс положительной полярности, транзистор Т1 отпирается. Возникает ток эмиттера, который протекает через резистор в цепи эмиттера и создает на этом резисторе падение напряжения, являющееся выходным сигналом. Аналогично импульс положительной полярности на входе В также приводит к появлению выходного сигнала, поскольку в этом случае отпирается транзистор Т2. Как и в случае схемы, показанной на рис. 8.2, а, при одновременном воздействии сигналов на оба входа также возникает выходной сигнал, что соответствует логической функции ИЛИ.

На рис. 8.2,в — д показаны условные обозначения схемы ИЛИ с различным числом входов (2, 3 и 5) [В отечественной научно-технической литературе используются другие обозначения схемы ИЛИ. — Прим. ред.]. Булева алгебра, упомянутая в разд. 8.1, является разделом математики; она описывает поведение переключающих логических схем и в символическом виде выражает соотношения между состояниями таких схем. В булевой алгебре знак + используется для обозначения функции ИЛИ — логического сложения. Поэтому выражение А + В в действительности обозначает А ИЛИ В, а вовсе не указывает на арифметическое сложение. Можно производить логическое сложение нескольких величин, например А + В + + С + D [Чтобы отличать логическую схему от арифметической, используется специальный символ логического сложения V- Тогда приведенное здесь выражение будет выглядеть следующим образом: A\/B\/C\/D. — Прим. ред.].

Как отмечалось выше, логическим состояниям ИСТИНА (И) и ЛОЖЬ (Л) соответствуют два значения логической величины. Логическая сумма двух логических величин может принимать значения, указанные в табл. 8.1 — 8.3.

Таблица 8.1

0 + 0 = 0

A + 0 = 1

0 + B = 1

A + B = 1

Таблица 8.2

Л + Л = Л

И + Л = И

Л + И = Л

И + И = И

Таблица 8.3

0 + 0 = 0

1 + 0 = 1

0 + 1 =1

1 + 1 = 1

При большем числе логических слагаемых возможны соотношения:

0+0 + 0 = 0; 0 + 1+0=1 и т. д.