Лр3 / 9492_Скотаренко_ЛР3_ЦЭ_отчёт_В-23

.pdfМИНОБРНАУКИ РОССИИ САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ «ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА) Кафедра РС

ОТЧЕТ по лабораторной работе №3

по дисциплине «Цифровая электроника» ТЕМА: «Основы построения схем в пакете Quartus II»

|

|

|

Скотаренко |

Студент гр. 9492 |

|

Д.Д. |

|

Преподаватель |

|

Мамчур Р.М. |

|

|

|||

|

|

|

|

Санкт-Петербург

2021

Цель работы:

Изучить событийную конструкцию always создать RS и DL-триггеры на языке Verilog с её помощью.

Задание:

Вариант-23

1.Собрать схему асинхронного RS-триггера в текстовом редакторе. Для этого воспользоваться кодом из приложения.

Изучить схему, реализованную в RTL-Viewer.

Построить временные диаграммы, иллюстрирующие работу устройства. Запрограммировать в отладочную плату. Тип ПЛИС – Altera Cyclone IV E EP4CE22F17C6. Указать входные сигналы на SW1(set),

SW2(reset), выходной – на LED1.

2.Собрать схему асинхронного DL-триггера в текстовом редакторе. Для этого воспользоваться кодом из приложения.

Изучить схему, реализованную в RTL-Viewer.

Построить временные диаграммы, иллюстрирующие работу устройства. Запрограммировать в отладочную плату. Указать входные сигналы на

SW1(data), SW2(load), выходной – на LED1.

Пример фрагмента кода на Verilog

RSтриггер |

DLтриггер |

module s_r_ff (set, reset, q); |

module d_l_ff (data, load, q); |

input set, reset; |

input data, load; |

output q; |

output q; |

reg q; |

reg q; |

always @ (posedge set or posedge |

always @ (load or data) |

reset) |

begin |

begin |

if (load) |

if (set) |

q <= data; |

q <= 1'b1; |

end |

else if (reset) |

endmodule |

q <= 1'b0; |

|

end |

|

endmodule |

|

|

|

В отчете должно быть: текст программы, скриншоты из RTL-Viewer, PinPlanner, временные диаграммы при наличии задержек.

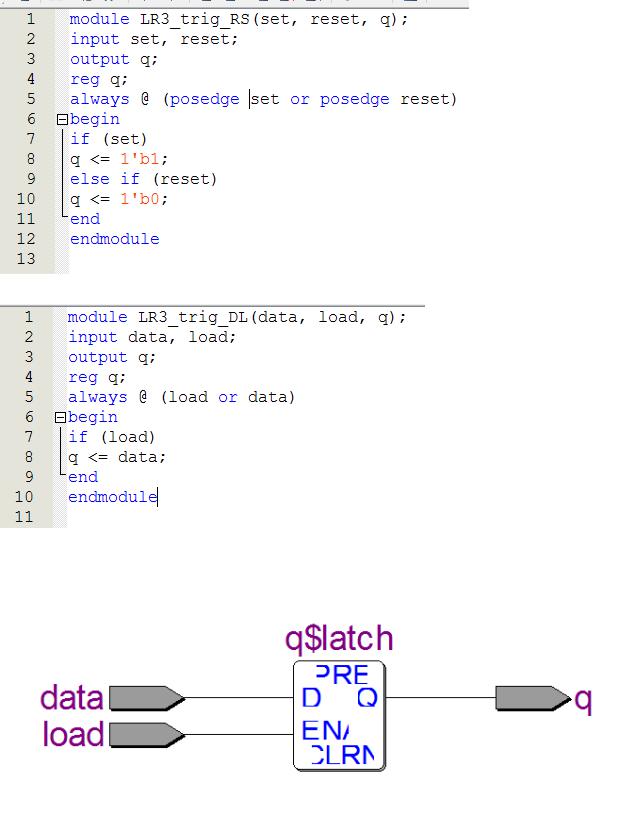

1) Текст программ RS и DL-триггеров: а) RS-триггер:

б) DL-триггер:

2) Представление обоих триггеров в RTL-viewer: а) DL-триггер:

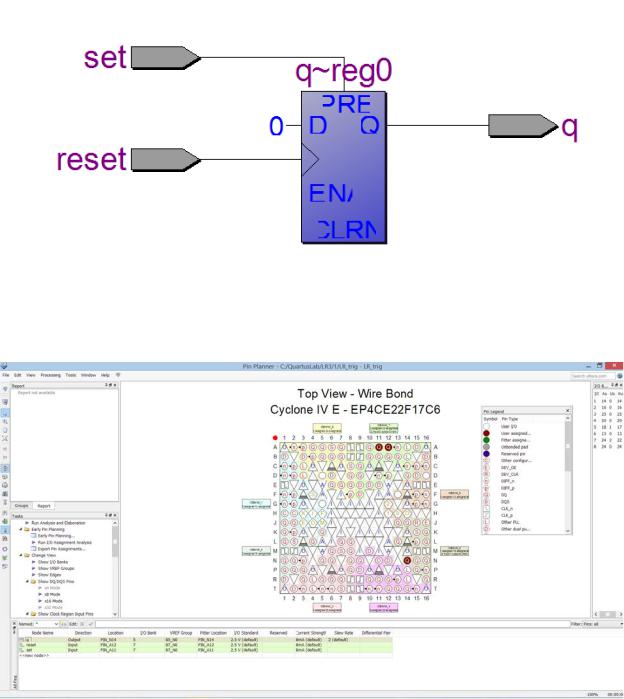

б) RS-триггер:

3) Pin planner:

а) RS-триггер:

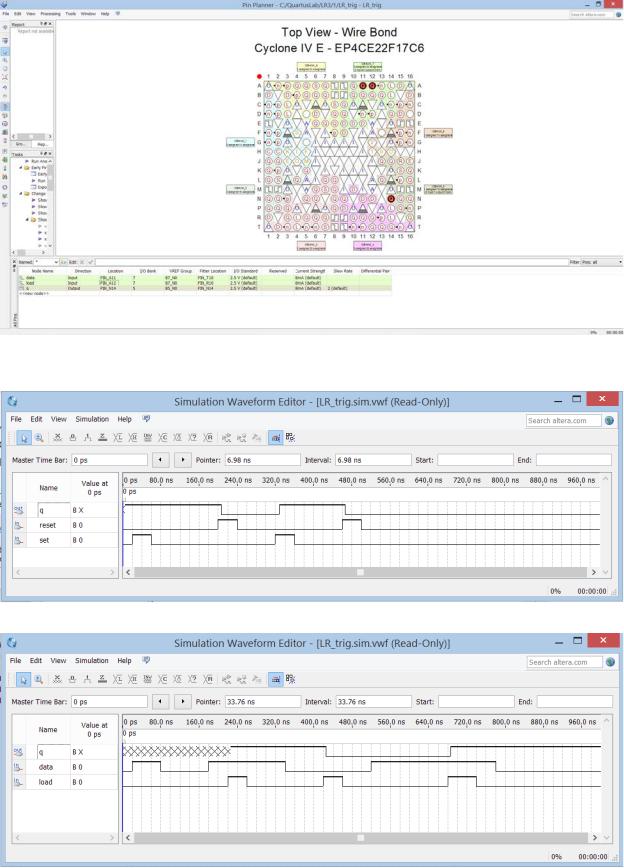

б) DL-триггер:

4) Осциллограммы работы триггеров с учётом задержек: а) RS-триггер:

б) DL-триггер:

Вывод:

В данной лабораторной работе мы познакомились с событийной конструкцией always и научились создавать простейшие ячейки памяти – RS и DL-триггеры на языке Verilog.