ЛР2 / 9492_Скотаренко_ЦЭ_ЛР2_отчёт_В3

.pdfМИНОБРНАУКИ РОССИИ САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ «ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА) Кафедра РС

ОТЧЕТ по лабораторной работе №2

по дисциплине «Цифровая электроника» ТЕМА: «Основы построения схем в пакете Quartus II»

|

|

|

Скотаренко |

Студент гр. 9492 |

|

Д.Д. |

|

Преподаватель |

|

Мамчур Р.М. |

|

|

|||

|

|

|

|

Санкт-Петербург

2021

Цель работы:

Изучить минимизацию ПФ с помощью диаграмм Вейча и представить полученную минимизированную функцию в виде схемы Quartus II с помощью блок-диаграмм и на языке Verilog.

Задание:

Вариант 3 1. Собрать схему (в графическом и текстовом редакторе), заданную

диаграммой Вейча

Найти МДНФ переключательной функции. Построить таблицу истинности для заданной функции.

Построить временные диаграммы при наличии и отсутствии задержек. Показать результат работы компонента RTL Viewer.

Обработка:

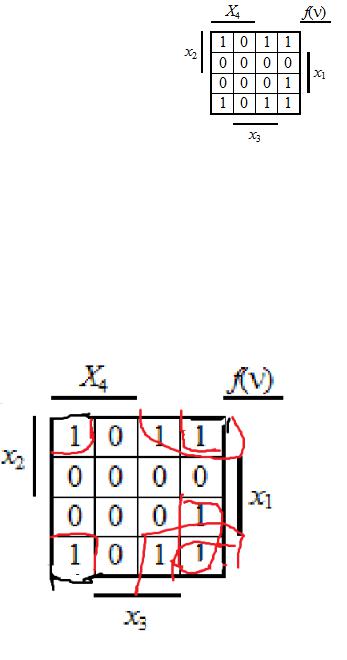

1) Минимизация:

МДНФ: ( 1, 2, 3, 4) = 1 3V 1 4V 2 3 4

Таблица истинности:

x1 |

x2 |

x3 |

x4 |

f |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

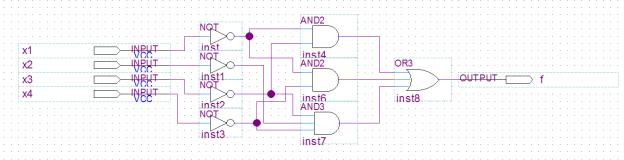

3) Схемы из блок-диаграмм и на Verilog: а) Блок-диаграмма:

б) Представление схемы из блок-диаграмм в RTL Viewer:

4) Осциллограмма работы схемы из блок-диаграмм без задержек и с задержками:

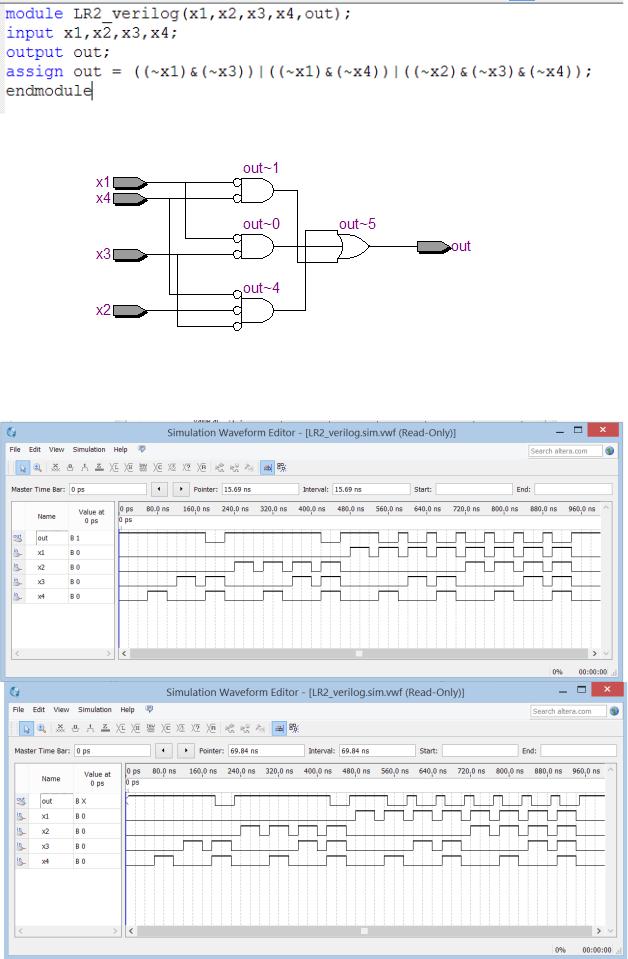

5) Схема на Verilog:

6) Схема на Verilog в RTL

7) Осциллограмма работы схемы на Verilog с учётом задержек и

без:

Вывод:

В данной лабораторной работе мы укрепили наши практические навыки минимизирования переключательных функций по диаграммам Вейча, а также укрепили опыт создания схем в среде Quartus II.