эбвсис ЛР1

.docxОТЧЕТ О ЛАБОРАТОРНОЙ РАБОТЕ № 1

Освоение среды разработки цифровых схем Quartus II

Цель:

Знакомство с особенностями работы приложения Quartus II 9.0 в процессе синтеза цифровых устройств на ПЛИС.

Задачи:

Изучение языка Verilog;

Проектирование простейших цифровых устройств с использованием языка Verilog;

Ознакомление со средой цифрового моделирования ModelSim, средствами САПР Quartus для синтеза и временного анализа цифровых схем.

Порядок выполнения работы:

По материалам лекций и вспомогательной литературы изучить основы языка Verilog. Ознакомиться с работой в САПР Quartus и среде моделирования Modelsim.

Спроектировать структурную схему устройства, реализующего заданную функциональность. Схема должна быть построена по принципу FSMD: тракт данных + управляющий автомат.

Описать схему на языке Verilog.

Создать тестовое окружение (testbench), полностью покрывающее заданную функциональность. Провести моделирование в среде Modelsim. Результаты представить на временных диаграммах и в виде текстового лога тестрования.

В пакете Quartus провести синтез схемы на основе Verilog-описания. Оценить соответствие полученной после синтеза схемы с ранее составленной структурной схемой устройства. 6. В пакете Quartus провести временной анализ полученной схемы. Определить максимально допустимую частоту работы схемы. Определить критический путь.

Вариант задания:

-

x1 x2 x3

y

0 0 0

0

0 0 1

0

0 1 0

0

0 1 1

0

1 0 0

0

1 0 1

1

1 1 0

0

1 1 1

1

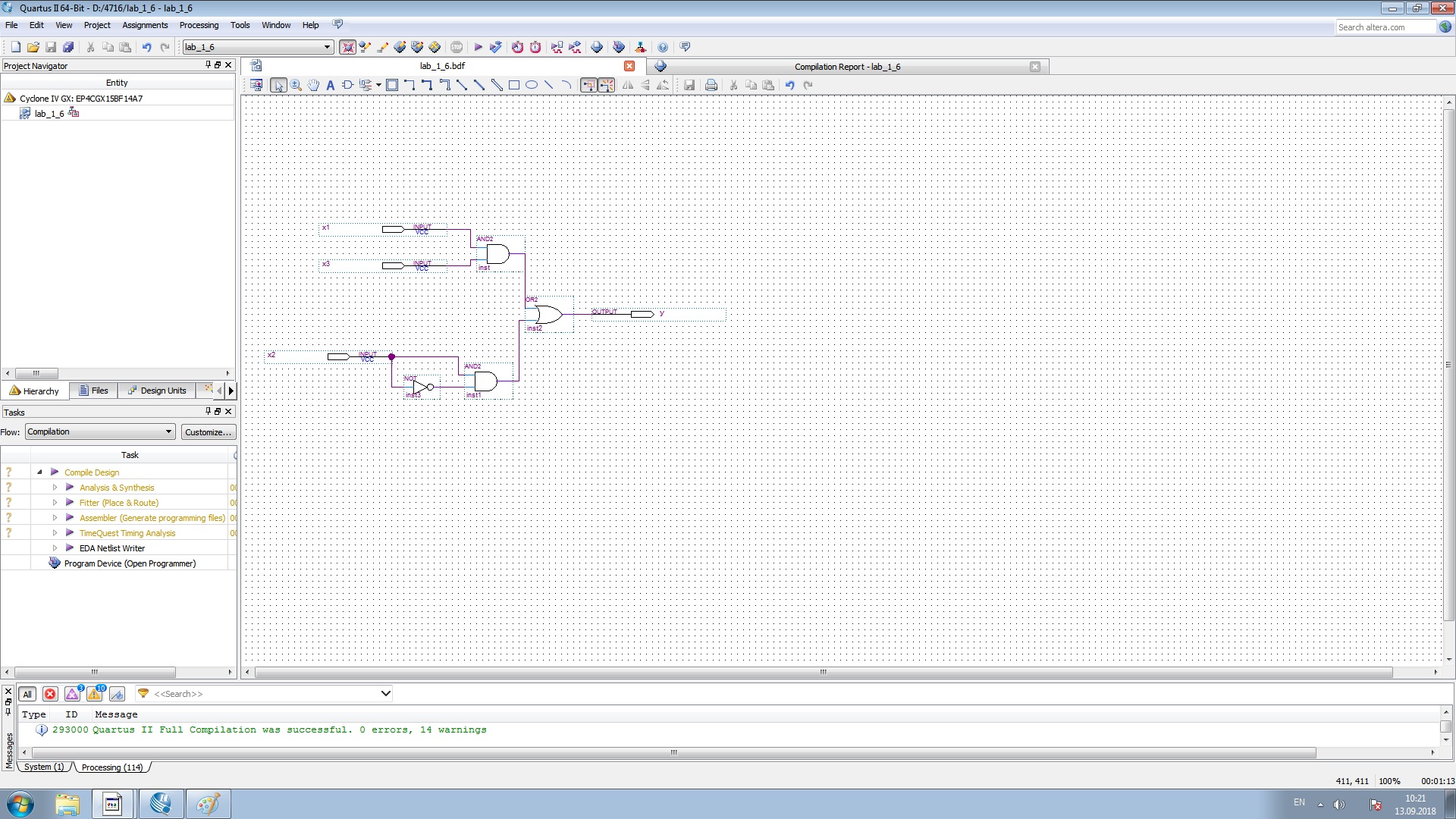

Рисунок

1

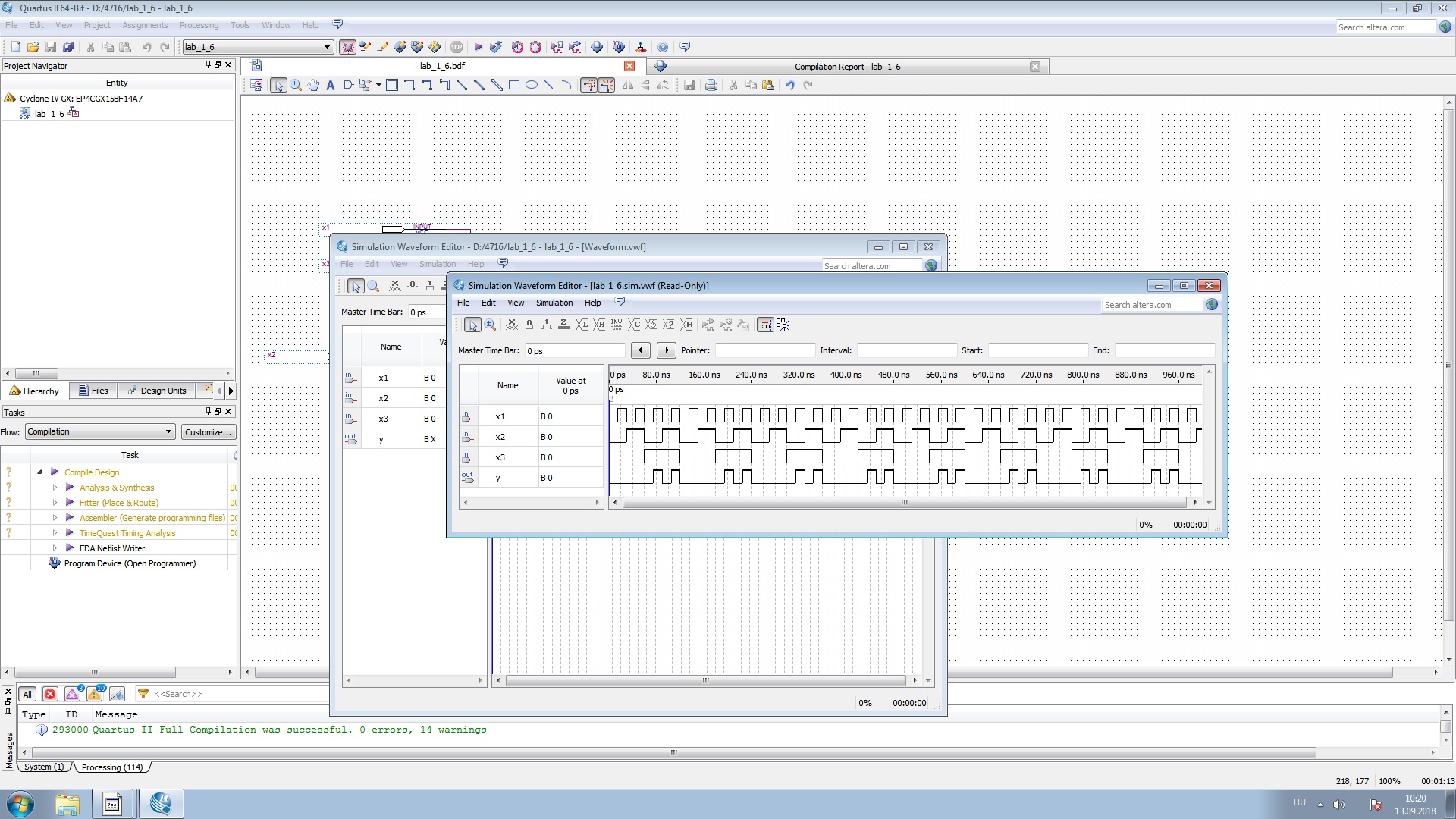

Рисунок

1

Вывод:

Я познакомилась с особенностями работы приложения Quartus II 9.0 в процессе синтеза цифровых устройств на ПЛИС. Научилась решать простейшие задачи.