- •Минобрнауки россии

- •I sbn х-хххх-хххх-х ©сПбГэту «лэти», 2011 Техническое задание

- •1. Постановка задачи

- •1.1. Имитатор подвижного сигнала

- •1.2. Микропроцессор 1821вм85

- •2. Выбор и обоснование структурной схемы имитатора

- •2.1. Структурная схема имитатора

- •2.2. Расчет основных параметров имитатора

- •3. Выбор элементов принципиальной схемы

- •3.1. Выбор элементной базы

- •3.2. Синтез счетчика с тремя модулями пересчета

- •3.3. Синтез счетчика по mod м0

- •3.4. Синтез счетчика по mod м1i

- •3.5. Синтез счетчика по mod Мj

- •3.6. Контроллер клавиатуры

- •3.7. Приемопередатчик, обслуживающий внешние устройства схемы

- •3.8. Дешифратор адресов

- •3.9. Организация памяти

- •3.10. Дисплей

- •4. Создание макроэлементов в символьном редакторе

- •5. Инициализация микроконтроллера

- •6. Выполнение принципиальной схемы

- •7. Перечень элементов принципиальной схемы

- •Список литературы

- •Минобрнауки россии

- •«Санкт-Петербургский государственный электротехнический университет

- •(СПбГэту)

- •Санкт-Петербург

- •201_ Г. Оглавление

- •Имитатор сигналов, отраженных от движущейся цели на бис Altera

- •197376, Санкт-Петербург, ул. Проф. Попова, д. 5

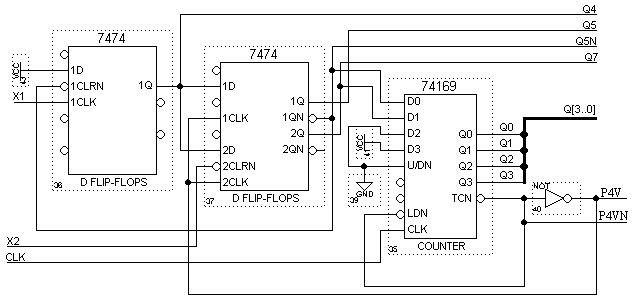

3.2. Синтез счетчика с тремя модулями пересчета

Для реализации такого счетчика можно использовать макроэлементы 74161 (4-разрядный счетчик) и 7474 (два D-триггера с прямыми и инверсными выходными сигналами). Синхронная загрузка данных позволяет менять модуль пересчета изменением загружаемых данных dM = D3D2D1D0. Модуль пересчета двоичного 4-разрядного счетчика с такой загрузкой данных определяется соотношениями: M = 16 – dM, 0 dM 14, из которых следует, что dM = 16 – M, 2 M 16.

Рассмотрим синтез

счетчика с переключением сигналами y1

и y2

трех модулей

пересчета Mv

= M0

– 1, M0,

M0

+1 при M0

= 5 на двоичном 4-разрядном счетчике.

Тогда загружаемые числа dM

= 16 – Mv

= 12,

11,

10. Из табл.

3.2 следует, что D3

= 1,

![]() ,

D1

=

,

D1

=

![]() ,D0

=

,D0

=

![]() .

.

Управляющие сигналы

y1

и y2

формируются

с помощью двух схем временной привязки

(СВП) входного сигнала управления

![]() к тактовому сигналуH,

что

необходимо для надежной работы синхронного

автомата, каким и является счетчик с

тремя

модулями пересчета.

Для

увеличения быстродействия счетчика

операция

к тактовому сигналуH,

что

необходимо для надежной работы синхронного

автомата, каким и является счетчик с

тремя

модулями пересчета.

Для

увеличения быстродействия счетчика

операция

![]() реализована с помощью одной из СВП без

использования дополнительного ЛЭ.

Длительность значений сигналов

реализована с помощью одной из СВП без

использования дополнительного ЛЭ.

Длительность значений сигналов![]() и

и![]() равнаMvT0.

Каждая из СВП реализована на двух

D-триггерах

(рис. 3.1), преобразующих

переходы сигнала

равнаMvT0.

Каждая из СВП реализована на двух

D-триггерах

(рис. 3.1), преобразующих

переходы сигнала

![]() с

0 на 1 (

с

0 на 1 (![]() =

1) в потенциальный сигнал

=

1) в потенциальный сигнал

|

Таблица 3.2 | |||||||

|

|

|

|

|

|

|

|

|

|

y1 |

y2 |

D3 |

D2 |

D1 |

D0 |

dM |

Mv |

|

0 |

0 |

1 |

0 |

1 |

1 |

11 |

5 |

|

0 |

1 |

1 |

0 |

1 |

1 |

11 |

5 |

|

1 |

0 |

1 |

1 |

0 |

0 |

12 |

4 |

|

1 |

1 |

1 |

0 |

1 |

0 |

10 |

6 |

|

Таблица 3.3 | |||||||

|

|

|

|

|

|

|

|

|

|

y1 |

y2 |

D3 |

D2 |

D1 |

D0 |

dM |

Mv |

|

0 |

0 |

1 |

1 |

0 |

0 |

12 |

5 |

|

0 |

1 |

1 |

1 |

0 |

0 |

12 |

5 |

|

1 |

0 |

1 |

1 |

0 |

1 |

13 |

4 |

|

1 |

1 |

1 |

0 |

1 |

1 |

11 |

6 |

y1,

сигнал же x2

не изменяется

на интервале работы MvT0

, поэтому

на вход

![]() триггера с выходомQ7

в этом

случае следует подать сигнал

триггера с выходомQ7

в этом

случае следует подать сигнал

![]() .

.

Схему выполним на

макроэлементах (МЭ) фирмы Altera,

используя

графический режим и используя макроэлементы

(МЭ), предоставляемые папками Prim,

Mf

(megafunction),

Edif

(electronic

design

interchange

format)

и mega_LPM:74161.

Двоичный 4-разрядный счетчик выполнен

на макроэлементе 74161, а D-триггеры

– на макроэлементе 7474 (два D-триггера

с прямым

Q

и инверсным

![]() выходами; инверсные сигналы обозначаются

какQN).

выходами; инверсные сигналы обозначаются

какQN).

На рис. 3.1 представлена

синтезированная схема; временные

диаграммы, приведенные на рис. 3.2, поясняют

работу счетчика. Пока сигнал

![]() = 0, в счетчик

записывается число d

= 11, и счетчик

имеет 5 внутренних состояний: 11, 12, 13, 14

и 15, т. е. делит на 5. С каждым приходом

сигнала

= 0, в счетчик

записывается число d

= 11, и счетчик

имеет 5 внутренних состояний: 11, 12, 13, 14

и 15, т. е. делит на 5. С каждым приходом

сигнала

![]() = 1 в счетчик

записываются числа d

= 10 при x2

= 1 (

= 1 в счетчик

записываются числа d

= 10 при x2

= 1 (![]() =

0) илиd

= 12 при x2

= 0 (

=

0) илиd

= 12 при x2

= 0 (![]() = 1),

при этом происходит изменение коэффициента

деления на 6 или на 4 соответственно.

= 1),

при этом происходит изменение коэффициента

деления на 6 или на 4 соответственно.

В рассмотренном счетчике основное влияние на максимально допустимое значение частоты тактового сигнала H оказывают задержки в счетчике и ЛЭ НЕ сигнала переноса P4, а также задержка в триггерах, формирующих данные. Время переходных процессов в синхронных автоматах не должно превышать периода тактового сигнала, поэтому указанная задержка резко снижает максимальное значение частоты тактового сигнала. Для определения

|

|

|

Рис. 3.1. Счетчик с тремя модулями пересчета Mv= 4, 5 и 6 |

|

|

|

Рис. 3.2. Временные диаграммы работы счетчика по mod 4, 5, 6 |

граничной частоты

тактового сигнала подсчитаем значения

длительностей переходных процессов в

схемах, формирующих сигналы

![]() = 0 и сигналы данных, загружаемых в счетчик

(эти значения берутся при моделировании

в пакете Max+plus II.Формирование

сигнала

= 0 и сигналы данных, загружаемых в счетчик

(эти значения берутся при моделировании

в пакете Max+plus II.Формирование

сигнала

![]() = 0 (в наносекундах):

= 0 (в наносекундах):

t

з![]() = t

зP4

+ t

зНЕ

= 7.4 + 5 = 12.4,

= t

зP4

+ t

зНЕ

= 7.4 + 5 = 12.4,

а формирование данных (в наносекундах):

t зD0,1,2 = t зP4 + t зТР = 7.4 + 2.8 = 10.2.

Наибольшее значение задержки в 12.4 нс ограничивает частоту тактового сигнала величиной fmax = 80 МГц. В табл. 3.4 представлены задержки, получаемые при временном анализе (Delay Matrix).

Таблица 3.4

Результаты временнóго анализа

|

Сигналы |

Выход | |||||||||

|

Вход |

|

LDN |

P4 |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5N |

Q7N |

|

CLK, нс |

|

7.4 |

7.4 |

2.8 |

2.8 |

2.8 |

2.8 |

|

7.8 |

7.8 |

|

X1, нс |

|

|

|

|

|

|

|

2.8 |

|

|

Используя

результаты временного анализа

(максимальная задержка формирования

данных D2-0

составляет

7.8 нс), позволяет считать максимальную

частоту работы делителя 120 МГц,

хотя в результате анализа указывается

частота 93.45 МГц,

что можно объяснить лишъ тем, что имея

два тактовых сигнала CLK

и сигнал

![]() ,

анализатор при вычислении минимального

периода тактовой частоты производит

сложение величины задержки данных

относительно сигнала CLK

и задержки сигнала Q4

относительно сигнала

,

анализатор при вычислении минимального

периода тактовой частоты производит

сложение величины задержки данных

относительно сигнала CLK

и задержки сигнала Q4

относительно сигнала

![]() .

Поэтому граничную частоту следует

считать равной 1/7.8

128 МГц.

.

Поэтому граничную частоту следует

считать равной 1/7.8

128 МГц.

Увеличить быстродействие счетчика с программируемым модулем пересчета можно с помощью дополнительного D-триггера [3], используемого для задержки сигнала переноса P4 на один такт (рис. 3.3). В этом случае модуль пересчета M определяется соотношениями [3]: M = 17 – dM, 0 dM 15, из которых следует, что dM = 17 – M, 2 M 17. Составив табл. 3.3, аналогичную табл. 3.2, легко получить

D3

= 1, D2

=

![]() ,D1

= y1y2,

D0

= y1.

,D1

= y1y2,

D0

= y1.

Полученным функциям

соответствует схема счетчика на

макроэлементах фирмы Altera

на рис. 3.3. На рис. 3.4 показаны временные

диаграммы работы такого счетчика. Запись

числа в такой счетчик происходит в

состоянии j =

0: при

![]() = 0 в счетчик

записывается число d

= 12 и M0

= 5, а при

= 0 в счетчик

записывается число d

= 12 и M0

= 5, а при

![]() = 1 и x2

= 0 в счетчик

записывается число d

= 13, обеспечивая модуль M0

– 1 = 4, а при

= 1 и x2

= 0 в счетчик

записывается число d

= 13, обеспечивая модуль M0

– 1 = 4, а при

![]() = 1 иx2

= 1 в счетчик записывается число d

= 11, обеспечивая модуль M0

+ 1 = 6.

= 1 иx2

= 1 в счетчик записывается число d

= 11, обеспечивая модуль M0

+ 1 = 6.

Для

определения граничной частоты подсчитаем

длительность переходных процессов в

схеме. Задержка формирования

сигнала (в наносекундах)

![]() = 0

= 0

t

з![]() = t

зТР

= 2.8,

= t

зТР

= 2.8,

|

|

|

Рис. 3.3. Быстродействующий счетчик по mod 4, 5, 6 |

|

|

|

Рис. 3.4. Временные диаграммы работы быстродействующего счетчика по mod4, 5, 6 |

а задержка формирования данных (в наносекундах)

t зD0,1,2 = t зТР + t зТР = 2.8 + 2.8 = 5.6.

Граничная частота в этом случае определяется частотой работы самого счетчика и равна 160 МГц.

Таблица 3.5

Результаты временного анализа

|

Сигналы |

Выход | ||||||||

|

Вход |

LDN |

P4 |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q7 |

|

CLK, нс |

2.8 |

7.4 |

2.8 |

2.8 |

2.8 |

2.8 |

|

7.8 |

7.8 |

|

X1, нс |

|

|

|

|

|

|

2.8 |

|

|

Однако результаты временного анализа, представленные табл. 3.5, показывают, что уменьшается задержка тактового сигнала загрузки данных с 7.4 до 2.8 нс, задержка же формирования самих данных остается такой же, как и в предыдущей схеме, т. е. 7.8 вместо 5.6 нс. Таким образом, включение дополнительного D-триггера не позволяет повысить граничную частоту выше 128 МГц.

Счетчик по mod

9, 10, 11. Для

такого счетчика будем использовать

реверсивный 4-разрядный счетчик и

D-триггеры

(макроэлементы 74169 и 7474), хотя можно

использовать элементы 74161 и 7474. Для

реверсивного счетчика в режиме вычитания

M

= d

+ 1 или M

= d

+ 2 ( с дополнительным D-триггером).

Из табл. 3.6 находим D0

=

![]() ,D1

= y1y2,

D2

= 0, D3

= 1. По этим функциям построена схема на

МЭ фирмы Altera,

представленная на рис. 3.5, а на рис. 3.6 –

временные диаграммы работы схемы.

,D1

= y1y2,

D2

= 0, D3

= 1. По этим функциям построена схема на

МЭ фирмы Altera,

представленная на рис. 3.5, а на рис. 3.6 –

временные диаграммы работы схемы.

Для вычисления

граничной частоты определим длительность

(в наносекундах) двух переходных

процессов, формирующих сигналы

![]() = 0 и сигналы данныхDi

:

= 0 и сигналы данныхDi

:

t

з![]() = t

зP4

= 7.4,

= t

зP4

= 7.4,

а формирование данных:

t зD0,1,2 = t зP4 + t зНЕ + t зТР = 7.4 + 5 + 2.8 = 15.2.

Наибольшее значение задержки в 15.4 нс ограничивает частоту тактового сигнала величиной fmax = 64.9 МГц.

|

Таблица 3.6 | |||||||

|

|

|

|

|

|

|

|

|

|

y1 |

y2 |

D3 |

D2 |

D1 |

D0 |

dM |

Mv |

|

0 |

0 |

1 |

0 |

0 |

1 |

9 |

10 |

|

0 |

1 |

1 |

0 |

0 |

1 |

9 |

10 |

|

1 |

0 |

1 |

0 |

0 |

0 |

8 |

9 |

|

1 |

1 |

1 |

0 |

1 |

0 |

10 |

11 |

|

Таблица 3.7 | |||||||

|

|

|

|

|

|

|

|

|

|

y1 |

y2 |

D3 |

D2 |

D1 |

D0 |

dM |

Mv |

|

0 |

0 |

1 |

0 |

0 |

0 |

8 |

10 |

|

0 |

1 |

1 |

0 |

0 |

0 |

8 |

10 |

|

1 |

0 |

0 |

1 |

1 |

1 |

7 |

9 |

|

1 |

1 |

1 |

0 |

0 |

1 |

9 |

11 |

|

|

|

Рис. 3.5. Счетчик по mod 9, 10, 11 |

|

|

|

Рис. 3.6. Временные диаграммы работы счетчика по mod 9, 10, 11 |

Таблица 3.8

Результаты временного анализа схемы рис. 3.5

|

Сигналы |

Выход | ||||||||

|

Вход |

|

P4 |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5N |

Q7N |

|

CLK, нс |

7.4 |

7.4 |

2.8 |

2.8 |

2.8 |

2.8 |

|

7.8 |

7.8 |

|

X1, нс |

|

|

|

|

|

|

2.8 |

|

|

Результаты временного анализа схемы на рис. 3.5, представленные в табл. 3.8, позволяют определить граничную частоту работы схемы f = = 1/7.8109 128 МГц.

Для быстродействующего счетчика из табл. 3.7 находим

D3

=

![]() ,D2

= D1

=

,D2

= D1

=

![]() ,D0

= y1.

,D0

= y1.

По схеме счетчика,

представленной на рис. 3.7, определяем

граничную частоту работы величиной 140

МГц

(определяется длительностью переходных

процессов): задержка формирования

сигнала

![]() = 0 (в наносекундах)

= 0 (в наносекундах)

t

з![]() =

t

зТР

= 2.8,

=

t

зТР

= 2.8,

|

|

|

Рис. 3.7. Быстродействующий счетчик поmod9, 10, 11 |

|

|

|

Рис. 3.8. Временные диаграммы работы быстродействующего счетчика по mod 9, 10, 11 |

Таблица 3.9

Результаты временного анализа схемы рис. 3.7

|

Сигналы |

Выход | ||||||||

|

Вход |

|

P4 |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5N |

Q7N |

|

CLK, нс |

2.8 |

2.8 |

2.8 |

2.8 |

2.8 |

2.8 |

|

7.8 |

7.8 |

|

X1, нс |

|

|

|

|

|

|

2.8 |

|

|

задержка формирования данных (в наносекундах):

t зD0,1,2 = t зТР + t зТР = 2.8 + 2.8 = 5.6.

На

рис. 3.8 представлены временные диаграммы

работы быстродействующего счетчика.

Загрузка данных происходит в состоянии

= 15 (Fh);

при значении сигнала

![]() = 0 записывается число d

= 8, тем самым задавая Mv

= = M0

= = 10,

а при

= 0 записывается число d

= 8, тем самым задавая Mv

= = M0

= = 10,

а при

![]() = 1 записывается d

= 7 или d

= 9, что переключает Mv

на 9 или 11.

= 1 записывается d

= 7 или d

= 9, что переключает Mv

на 9 или 11.