- •1. Логическая операция «и».

- •2 .Логическая операция «или».

- •3 .Логическая операция «исключающее или».

- •8. Регистры памяти.

- •9. Регистры сдвига.

- •10. Дешифраторы.

- •11. Шифраторы.

- •1 2. Мультиплексоры.

- •13. Демультиплексоры.

- •14. Суммирующие двоичные счетчики.

- •15. Вычитающие двоичные счетчики.

- •16. Структура микропроцессоров.

- •17. Основные характеристики и классификация микропроцессоров.

- •18. Выполнение арифметических операций в микропроцессорах. Прямой, обратный, дополнительный коды.

- •19. Представление чисел в цифровых вычислительных машинах. Числа с фиксированной и плавающей точкой.

- •20. Архитектура мп-системы на базе мп кр580вм80а.

- •21. Регистровая модель мп-системы на базе мп кр580вм80а.

- •22. Режимы адресации мп кр580вм80а.

- •23. Особенности программирования на языке ассемблер.

- •24. Команды пересылки данных мп кр580вм80а.

- •25. Арифметические-логические операции мп кр580вм80а.

- •26. Команды перехода мп кр580вм80а.

- •27. Команды вызова подпрограмм мп кр580вм80а.

- •28. Условное обозначение мп кр580вм80а и назначение выводов.

- •30. Состояние «прерывание» мп кр580вм80а.

- •31. Состояние «захват» мп кр580вм80а

- •32.Особенности выполнения машинного цикла «выборка кода команды из памяти» мп кр580вм80а.

- •33.Машинный цикл «запись данных в память» или «запись данных во внешнее устройство» мп кр580вм80а.

- •34.Типы машинных циклов мп кр580вм80а и их краткая характеристика.

- •35.Организация магистралей микро-эвм на базе мп кр580вм80а. Схема кр580ва86.

- •36.Формирование управляющих сигналов микро-эвм на базе мп кр580вм80а.

- •38.Системный контроллер кр580вк28.

- •39.Генератор тактовых импульсов кр580гф24.

- •40.Организация временных интервалов в микро-эвм. Микросхема кр580ви53. Особенности управления и подключения к микро-эвм.

- •41. Характеристика режима работы таймера «Выдача сигнала прерывания по конечному числу». Временные диаграммы.

- •42. Особенности организации режима одновибратора схемы кр580ви53.

- •43. Организация режимов генератора прямоугольных импульсов с использованием программируемого таймера.

- •44. Характеристика управляющего слова интервального таймера кр580ви53.

- •45.Особенности работы таймера кр580ви53 в режимах «Программно- управляемый строб» и «Схемотехнически управляемый строб»

- •48.Классификация запоминающих устройств и их основные характеристики.

- •49. Оперативные запоминающиеся устройства.

- •50. Постоянные запоминающиеся устройства.

- •51. Перепрограммируемые запоминающие устройства.

1. Логическая операция «и».

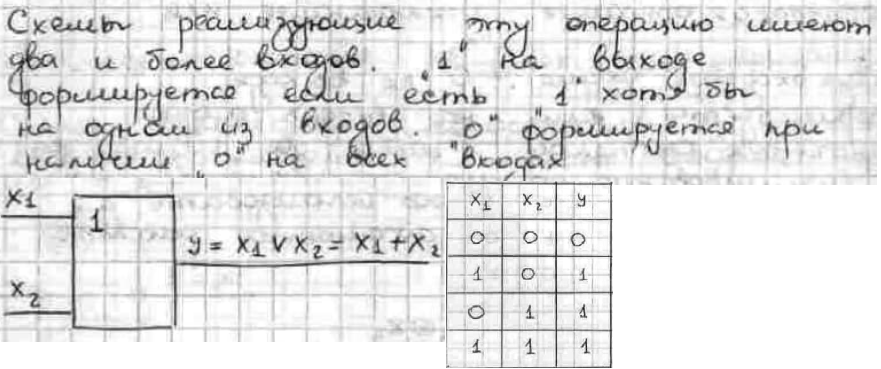

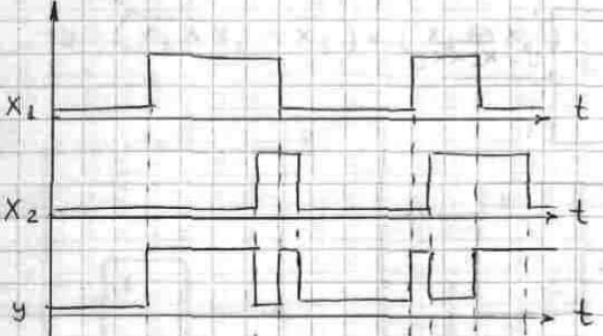

2 .Логическая операция «или».

3 .Логическая операция «исключающее или».

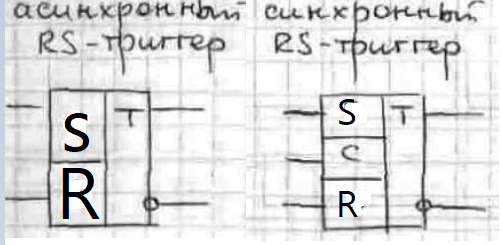

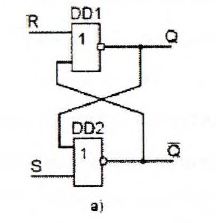

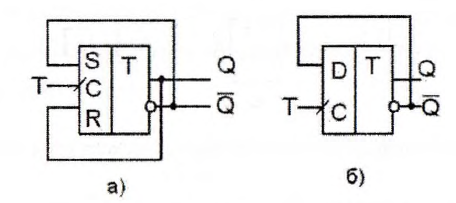

4. RS – триггеры.

Триггером называют устройство, имеющее два устойчивых состояния и способное под действием внешних сигналов переключаться из одного состояния в другое. При этом напряжение на его выходе изменяется скачкообразно. Они являются основными устройствами для построения запоминающих устройств и регистров. Различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет своё состояние непосредственно в момент изменения сигнала на его информационных входах. Синхронный триггер изменяет своё состояние лишь в строго определенные (тактовые) моменты времени, соответствующие воздействию активного синхросигнала на его синхронизирующем входе С. Триггеры относят к последовательным устройствам.

RS–триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входа S и R. По входу S триггер устанавливается в состояние Q=1, а по входу R триггер устанавливается в состояние Q=0. S=0 и R=0 режим хранения. S=1 и R=1 запрещена. Бывает как синхронный, так и асинхронный.

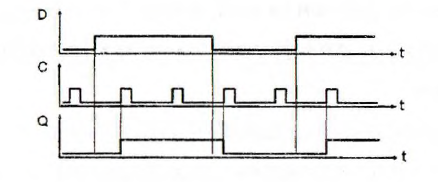

5. D – триггеры.

D–триггер имеет лишь один информационный вход D. Вход С - управляющий и служит для подачи синхронизирующего сигнала. Смена информации происходит по синхросигналу и поэтому этот триггер может быть только синхронным.

6. Т – триггеры.

Т–триггер — это триггер со счётным входом. Он имеет один информационный вход. При приходе активного сигнала Т-триггер меняет своё состояние на противоположное и сохраняет предыдущее состояние при отсутствии сигнала на входе.

7. JK – триггеры.

JK-триггеры — это двухступенчатые универсальные синхронные триггеры. Универсальность заключается в том, что на их основе можно реализовать любой другой тип логических триггеров RS, D, Т. По входу J триггер устанавливается в состояние Q=1, а по входу K триггер устанавливается в состояние Q=0. J=0 и K=0 режим хранения. J=1 и K=1 инверсия.

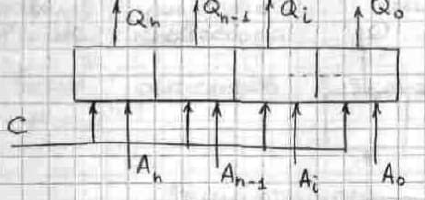

8. Регистры памяти.

Основная функция регистров - хранение одного многоразрядного числа. Регистр строится в виде набора триггеров, каждый из которых предназначается для одного бита числа. Таким образом, регистр для хранения n-разрядного двоичного числа должен содержать n триггеров.

Регистры

с параллельным приемом и выдачей служат

для хранения информации и называются

регистрами памяти. Изменение хранящейся

информации (ввод новой информации)

происходит после соответствующего

изменения сигналов на входах при

поступлении фронта синхросигналов.

Регистры

с параллельным приемом и выдачей служат

для хранения информации и называются

регистрами памяти. Изменение хранящейся

информации (ввод новой информации)

происходит после соответствующего

изменения сигналов на входах при

поступлении фронта синхросигналов.

9. Регистры сдвига.

Регистры с последовательным приемом и выдачей информации называются регистрами сдвига. При каждом такте синхроимпульса производится последовательный сдвиг поступающей на вход информации на один разряд. После поступления m синхроимпульсов весь регистр оказывается заполненным разрядами числа и первый разряд числа появляется на выходе регистра. В течение последующих п синхроимпульсов производится последовательный поразрядный выход из регистров записанного числа, после чего регистр оказывается полностью очищенным.