3-й семестр / Лекции 2

.pdf

Мультиплексоры используются в вычислительных машинах обычно в качестве управляющей логики, т.к. мультиплексор может выполнять любую

логическую операцию. |

|

|

|

|

|

|

Таблица 7.1. |

|

Логические операции для MS. |

|

|

1 2 |

1 2 |

1 2 |

1 2 |

0 0 |

0 − 1 |

0 − 1 |

0 − 1 |

0 1 |

0 − 2 |

1 − 2 |

1 − 2 |

1 0 |

0 − 3 |

1 − 3 |

1 − 3 |

1 1 |

1 − 4 |

1 − 4 |

0 − 4 |

7.2 Сумматоры (SM)

7.2.1. Определение

Сумматор (SM) — это узел машины, предназначенный для выполнения арифметических операций над числами (операндами).

Взависимости от того, в какой системе счисления представлены операнды, сумматоры могут быть:

- двоичные - десятичные - троичные - … и т.д.

Взависимости от числа входов сумматоры могут быть:

-полусумматоры (на 2 входа)

-полные сумматоры (на 3 входа)

По логической структуре SM могут быть:

-комбинационные

-накапливающие

-комбинационно-накапливающие

По организации цепей переноса SM могут быть:

- с последовательным переносом

41

-со сквозным переносом

-с параллельным переносом

Само суммирование может выполняться на:

-одноразрядных сумматорах

-многоразрядных сумматорах

Само суммирование может выполняться:

-последовательно (начиная с младшего разряда)

-параллельно (все разряды одновременно)

-параллельно-последовательно (SM разбивается на группы: внутри группы - параллельный перенос, между группами - последовательный)

7.2.1. Комбинационный одноразрядный сумматор

Это такой SM, который вырабатывает выходные сигналы суммы и переноса, которые определяются комбинациями цифр слагаемых, поданных одновременно на входы сумматора.

Такой SM не обладает памятью (для запоминания на выходе ставят RS или D-Tr), т.е. при снятии входных сигналов снимаются и выходные сигналы. Это быстродействующий сумматор, т.к. работает за один такт.

Структурные обозначения

|

|

Обозначения: |

|

|

|

, - разряды операндов |

|

|

|

- перенос из предыдущего разряда |

|

Рис. 7.3. Полусумматор и полный |

+1 - перенос в следующий разряд |

||

|

сумматор. |

|

- значение суммы в разряде |

Синтез полусумматора. |

|

|

|

|

|

|

Таблица 7.2. |

|

Таблица истинности полусумматора. |

||

|

|

|

+1 |

0 |

0 |

0 |

0 |

|

|

42 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

В ДНФ:

= |

̅̅ |

|

˅ |

̅̅ |

(7.2) |

||

|

|

|

|

|

|||

|

|

|

|

|

(7.3) |

||

|

+1 |

= |

|

|

|||

|

|

|

|

|

|

|

|

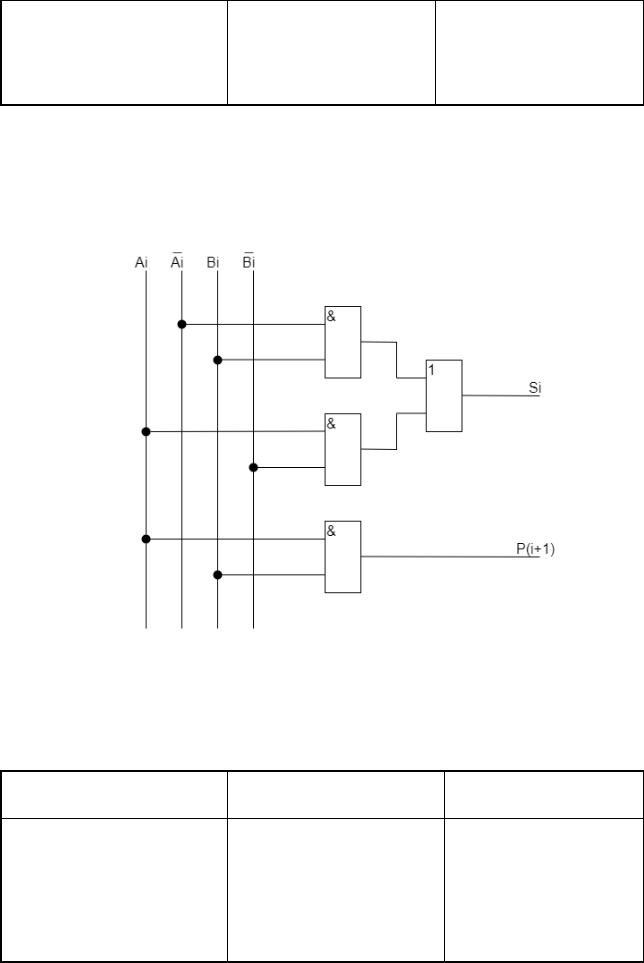

Построим комбинационную схему сумматора в классическом базисе.

Рис. 7.4. Комбинационная схема сумматора.

Синтез полного одноразрядного сумматора.

Таблица 7.3

Таблица истинности полного одноразрядного сумматора

|

|

+1 |

||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

|

|

|

43 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Формула: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

( |

) |

̅̅ ̅̅ |

|

|

|

̅̅ |

|

|

|

̅̅ |

|

̅̅ ̅̅ |

|

|

|

|

|

|

|

|

|

(7.2) |

||||||||||||||||

|

|

|

|

|

|

|

|

˅ |

|

|

|

|

|

˅ |

|

|

|

|

|

˅ |

|

|

|

|

|

|

|||||||||||||

|

ДНФ = |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

( ) |

̅̅ |

|

|

|

|

|

|

|

|

|

̅̅ |

|

|

|

|

|

|

|

|

|

̅̅ |

|

|

|

|

|

|

|

|

(7.3) |

|||||||

+1 |

|

|

|

|

|

|

|

|

˅ |

|

|

|

|

|

˅ |

|

|

|

|

|

˅ |

|

|

|

|

|

|

||||||||||||

ДНФ = |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

Рис. 7.5. Комбинационная схема полного одноразрядного сумматора.

44

7.2.2. Накапливающий сумматор

Это такой сумматор, который вырабатывает выходные сигналы суммы и переноса и хранит их значение после снятия входных сигналов. При этом коды слагаемых поступают на вход SM последовательно, один за другим.

Примечание №1.

Раз сумматор хранит значение суммы, то он должен строиться на триггерах (на T-Tr, т.к. именно T-Tr выполняет операцию сложения по модулю 2).

Примечание №2.

Быстродействие этого сумматора в 3 раза ниже, чем у комбинационных, т.к. он работает за 3 такта.

7.2.3. Многоразрядный сумматор

Их построение зависит от типа Ц.В.М.: параллельного она действия или последовательного.

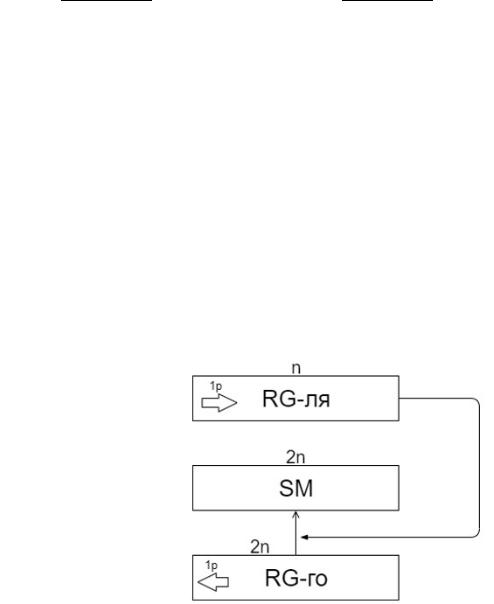

Если Ц.В.М. последовательного типа, то сумматор можно построить на одном одноразрядном полном сумматоре, если перенос Pi+1 подавать на вход Pi с задержкой на 1 такт (рис. 7.6).

Рис. 7.6. Многоразрядный сумматор на одноразрядном полном сумматоре На таком SM за n тактов можно просуммировать 2 n-разрядных числа. Если Ц.В.М параллельного действия, то:

1) Сумматор комбинационного типа (рис. 7.7)

45

Его структура:

Рис. 7.7. Сумматор комбинационного типа 2) Сумматор накапливающего типа (рис. 7.8)

Рис. 7.8. Сумматор накапливающего типа В таких сумматорах самым сложным является вопрос о распространении

переноса.

Переносы могут быть:

-последовательный

-сквозной (у накапливающего SM)

-параллельный

Примечание.

Самое большое количество оборудования требуется для организации параллельного переноса.

46

УСТРОЙСТВА Ц.В.М. Лекция №8

8.1Арифметико-логическое устройство (АЛУ)

8.1.1Определение

АЛУ — это устройство, предназначенное для выполнения арифметических и логических операций.

АЛУ бывают:

-универсального типа (состоит из одного блока, который выполняет набор арифметических и логических операций)

-специализированного типа (состоит из нескольких блоков, каждый из которых выполняет часть набора операций. Это позволяет параллельно выполнять несколько арифметико-логических операций).

8.1.2 Сложение в Ц.В.М.

1) Сложение с фиксированной запятой. Выполняется на одноили многоразрядном SM.

Структурная схема АЛУ для выполнения алгебраического сложения (B±A) (рис. 8.1):

Рис. 8.1. Структурная схема АЛУ для сложения

47

Слагаемые поступают в АЛУ последовательно, но разным управляющим сигналом, т.к. ОП выдает слагаемые на шину входа последовательно.

В этой схеме слагаемые поступают с шины входа в прямом обычном коде (с первым знаковым разрядом), а сама операция выполняется в модифицированном дополнительном, поэтому при передаче слагаемых на сумматор делается размножение знакового разряда (рис. 8.2).

Рис. 8.2. Размножение знакового разряда

Если слагаемое A - положительное, то оно с RG 1 подается прямым кодом на RG A и далее на левое плечо сумматора с размножением знакового разряда.

Если слагаемое A - отрицательное, то оно должно быть на SM в модифицированном дополнительном коде. Для этого оно передается с RG 1 на RG A инверсным кодом (обратным), а единица, которая прибавляется на SM. С выхода SM на RG SM результат передается обычным кодом.

Работу структурной схемы обычно описывают на специальном языке, который называется ЯМП (язык микропрограммирования) — это алголоподобный язык (ALGOL).

НАЧАЛО

ПР RG B: RG B := ШИ ВХ <прием операнда B>

ПР RG B: RG 1 := ШИ ВХ <прием операнда A> ПР SM: ЕСЛИ сложение ТО

ПР RG A: RG A := RG 1 ИНАЧЕ ПР RG A: RG A := ̅̅̅̅̅̅̅RG 1

СУММА: ЕСЛИ сложение ТО

48

ПР RG SM: RG SM := RG A + RG B ИНАЧЕ RG SM := RG A + RG B + 2−

ПР ИЛИ ВХ: ПР ИЛИ ВХ: RG SM <вывод результата> КОНЕЦ 2) Сложение чисел с плавающей запятой (8.1).

+350 = 0,35 |

10 |

(8.1) |

|

3 |

|

|

2 |

|

35 = 0,35 10 |

|

|

385 = 0,385 |

310 |

|

Алгоритм:

-выравнивание порядков в сторону большего

-сложение мантисс по правилу сложения чисел с фиксированной запятой

-присваивание общего порядка

-нормализация результата

-округление результата

8.1.3.Правила машинного округления

1)Для результата, полученного на сумматоре:

К SM добавляется 1 или несколько дополнительных разрядов и к старшему прибавляем единицу. После этого дополнительные разряды отбрасываются. Если в старшем дополнительном разряде была 1, то это округление с избытком, если 0, то округление с недостатком.

2) Для результата, полученного на RG, например, при делении:

В младший разряд RG принудительно ставится единица. При этом, если в младшем разряде была 1, то округление с недостатком, если 0 - то с избытком.

49

Лекция №9

9.1.Умножение в ЦВМ

9.1.1.Способы умножения в ЦВМ

|

x |

1 |

0 |

1 |

x |

1 |

0 |

1 |

|

|

|

0 |

1 |

1 |

0 |

1 |

1 |

|

|

||

|

|

1 |

0 |

1 |

|

0 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

0 |

1 |

|

0 |

0 |

0 |

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

Первый способ делится на 2 способа: |

Второй способ делится на 2 способа |

||

1. |

SM |

1. |

SM |

2. |

Множ. |

2. |

Множ. |

Из этого примера видно, что существует 4 способа умножения.

9.1.2 Способ №1 умножения в ЦВМ

Младший разряд вперёд со схемой RG множителя и RG множимого (рис.

9.1)

Рис. 9.1. Структура первого способа умножения в ЦВМ.

9.1.3. Способ №2 умножения в ЦВМ.

Младший разряд вперёд со сдвигом SM и RG множителя (рис 9.2).

50