Разное / АВС. Конфликты

.pdf

Лекция 5.

Мы знаем, что во всех современных процессорах обработка команд производится конвейерным способом. То есть предполагается, что в каждый момент времени выполняются все n этапов для n подряд идущих команд.

Впервые конвейер был предложен и применен в RISC-процессорах и, действительно, для первых версий таких процессоров он работал практически безотказно. Но время летит, скорости растут, задачи усложняются, и система команд усовершенствуется. Уже к началу нашего века RISC перестает быть reduced instructions. Команды этих процессоров уже не укладываются за один такт исполнения. Поэтому конфликты на этапе исполнения команд становятся неизбежны. Конфликты определяются с помощью счетчиков использования регистров.

Рассмотрим 3 фрагмента и определим возникающие конфликты. Фрагмент 1.

SUB R7, R6, R5

ADD R4, R7, R3

В этом фрагменте команда сложения пытается прочитать состояние источника до получения в этом регистре результата предыдущей команды. Это RAW=конфликт. Чтение должно производиться после записи.

Фрагмент 2. MUL R5, R4, R0 AND R4, R3, R2

Здесь команда логического умножения пытается переписать состояние регистра, хотя его состояние еще не считано предыдущей операцией. Такой конфликт называется WAR-конфликт. Запись должна производиться только после считывания.

Фрагмент 3. EOR R7, R3, R3 ADD R7, R6, R5

Тут команда сложения пытается записать результат в регистр, в который еще не успела поместить результат предыдущая команда. Случай называется WAWконфликт. Нельзя записывать данные в тот регистр, в который еще не поместила данные предыдущая команда.

Теперь дополним эти фрагменты командами. Фрагмент 1.

1.SUB R7, R6, R5

2.ADD R4, R7, R3

3.LDR R0, [R2]

Фрагмент 2.

1.MUL R5, R4, R0

2.AND R4, R3, R2

3.MOV R6, R7

Фрагмент 3.

1.EOR R7, R3, R3

2.ADD R7, R6, R5

3.MOV R1, #20

В каждом из трех фрагментов возможно поменять местами третью и вторую команды, и тогда можно избежать конфликтных ситуаций. Но, предположим, что в первом фрагменте следующий код:

1.SUB R7, R6, R5

2.ADD R4, R7, R3

3.LDR R3, [R2]

Втаком случае снова возникает конфликт (WAR). Подмена команд становится невозможна.

Вопросы: MOV R3, #0

MLA R3, R1, R2, R3

MOV R3, #0

MOV R4, R3 LDR R1, [R0], #4 LDR R2, [R1], #4 MUL R3, R1, R2 ADD R3, R3, R4

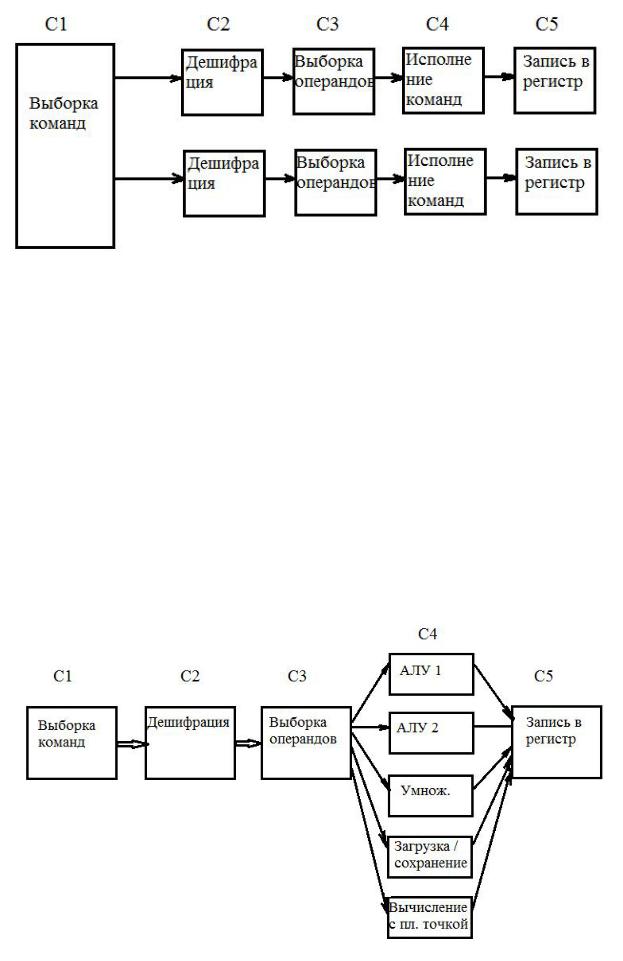

Для уменьшения временных потерь, связанных с конфликтными ситуациями, в компьютерах, основанных на RISC-процессорах, начали применять сдвоенный конвейер. При этом блок выборки команд выставлял на конвейер сразу две команды.

.

Команды должны быть независимы друг от друга. У них должны быть разные источники и приемники, и результат одной команды не должен влиять на выполнение другой. У компании INTEL подобная схема начала применяться в Pentium, но там был один основной конвейер, в который могли поступать любые команды, а второй вспомогательный, для простых команд. Операндами простых команд могли быть только целые числа. Если к сложной команде не находилось пары (несовместимая, или также сложная команда), то работал только основной конвейер, а ко второй команде, в свою очередь, подбиралась пара.

Очевидно, что такой путь наращивания числа параллельных конвейеров не слишком эффективен из-за жестких требований к выбираемым командам. Тем более, что в каждом из конвейеров самым длительным будет четвертый этап. Поэтому распараллеливание начали делать на этапе С4 – исполнение команд. Такой подход к построению конвейера носит название суперскалярная архитектура.

.

Казалось бы, скорость выполнения операций в таком случае вырастает пропорционально числу параллельных блоков исполнения, но, в случае возникающих известных нам конфликтов операндов, выдача команд временно прекращается.

Теперь мы можем рассмотреть пример выполнения фрагмента программы на суперскалярной архитектуре, считая, что блок декодирования выдает по две команды за цикл.

1.MUL R3, R0, R1

2.ADD R4, R0, R2

3.ADD R5, R0, R1

4.ADD R6, R1, R4

5.MUL R7, R1, R2

6.SUB R1, R0, R2

Изначально предположим, что команды должны исполняться строго в том порядке, как они поступают из блока выборки. А затем посмотрим, что изменится, если будет разрешена подмена команд и регистров.

В любом случае блок подмены задействует счетчики, обсчитывающие количество обращений к регистрам источникам (с них производится считывание), к регистрам приемникам (в них производится запись), и к различным функциональным блокам этапа исполнения. Это необходимо для устранения возможных конфликтов. Для регистров-источников счетчики подсчитывают количество использований каждого регистра в выполняющихся командах. Как только команда, содержавшая поименованный регистр выполнится, состояние счетчика уменьшается на «1».

Для регистров-приемников в счетчике содержится по одному биту на регистр. Если этот бит установлен в «1», это означает, что команда еще не выполнена, и обращение других команд к данному регистру невозможно.

Запишем порядок работы в виде таблиц Выполнение в порядке следования из блока предварительной выборки

представлено в табл. 3.1.

Таблица 3.1.

№ |

команды |

выдача |

Результат |

комментарии |

|

цикла |

|

|

в |

|

|

|

|

|

регистре |

|

|

1 |

MUL R3, R0, R1 |

1 |

- |

R0,R1-rd; R3-wr |

|

|

ADD R4, R0, R2 |

2 |

- |

R0,R2-rd; |

R4-wr |

|

|

|

|

конфликтов нет |

|

2 |

ADD R5, R0, R1 |

3 |

- |

R0,R1-rd; R5-wr |

|

|

ADD R6, R1, R4 |

- |

- |

R1-rd, R4 (RAW) |

|

|

|

|

|

Выдача приостановлена |

|

3 |

|

|

|

Не готов р-т MUL |

|

4 |

|

|

1 |

|

|

|

|

|

2 |

|

|

|

|

|

3 |

Свободен для чтения R4 |

|

|

|

|

|

5 |

|

4 |

|

Свободен для чтения R4 |

|

MUL R7, R1, R2 |

5 |

|

R1,R2-rd; R7-wr |

|

|

|

|

|

6 |

SUB R1, R0, R2 |

|

|

R1(WAR) |

|

|

|

|

|

7 |

|

|

4 |

|

8 |

|

|

5 |

Свободен для записи R1 |

9 |

|

6 |

|

Свободен для записи R1 |

10 |

|

|

|

|

11 |

|

|

6 |

|

Счетчики источников в первом цикле определяют использование R1, R2 и дважды R0. Конфликта нет, команда сложения также следует на исполнение. Счетчик приемников отметил R3 и R4.

Первая команда второго цикла также не встречает конфликтов, счетчики источников R0 и R1увеличиваются на «1». Счетчик приемников отметил R5. Вторая команда во втором цикле не сможет выйти на исполнение, т.к. она должна использовать содержимое приемника R4 незавершенной команды умножения.

Из таблицы видим, что команда сложения, использующая R4, сможет быть запущена на исполнение лишь на пятом цикле. С ней в паре запустится команда умножения, использующая операнд-источник R1.

В шестом цикле команда вычитания должна переписать R1, используя его как приемник. Возникает WAR-конфликт, исполнение команды задерживается. Оно становится возможным при завершении на восьмом цикле команды умножения. SUB уходит на исполнение только на девятом цикле.

Теперь рассмотрим возможность подмены команд и регистров, табл. 3.2.

Таблица 3.2.

№ |

|

команды |

выдача |

Результат |

комментарии |

|

|

|||||||||

цикла |

|

|

|

|

|

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

регистре |

|

|

|

1 |

|

MUL R3, R0, R1 |

1 |

- |

R0,R1-rd; R3-wr |

|

||||||||||

|

|

ADD R4, R0, R2 |

2 |

- |

R0,R2-rd; |

|

R4-wr |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

конфликтов нет |

|

|

2 |

|

ADD R5, R0, R1 |

3 |

- |

R0,R1-rd; R5-wr |

|

||||||||||

|

|

ADD |

R |

6 |

, |

R |

1 |

, |

R |

4 |

|

- |

- |

R1-rd, R4 (RAW) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Замена команды |

|

|

3 |

|

MUL R7, R1, R2 |

5 |

|

|

|

|

|||||||||

|

|

SUB R1, R0, R2 |

6 |

2 |

R1(WAR) в 6 команде |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

заменяется |

на |

S1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Свободен для чтения R4 |

||

4 |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

Свободен для чтения R4 |

||

|

|

|

1 |

|

|

|

|

3 |

|

5 |

|

|

6 |

|

|

|

|

|

|

6 |

|

|

4 |

|

|

|

|

5 |

|

Теперь порядок выдачи команд на исполнение не зависит от порядка выборки команд из памяти. Для команд первого цикла и первой команды второго цикла все остается подобно первому случаю. Вторая команда во втором цикле не может быть выдана на исполнение, но она заменяется первой командой третьего цикла. При такой подмене необходима предварительная проверка возможных конфликтов операндов выдаваемой и пропускаемой команд. Для этого включаются счетчики использования регистров на пропускаемую команду.

Во второй команде третьего цикла, для устранения WAR-конфликта, регистр R1 подменяется на скрытый регистр S1. В реальных компьютерах для подготовки очереди на исполнение используются только скрытые регистры, а их связь с заявленными регистрами устанавливается с помощью табличной памяти. Это позволяет избежать WAR и WAW-конфликтов.