Лекция 11 Последовательностные логические элементы, Тригеры

.doc

5.3. Последовательностные логические устройства

Из логических элементов составляются схемы, называемые логическими устройствами. Типовые функциональные узлы этих устройств выпускаются в виде отдельных интегральных микросхем. Если на выходе логического устройства информация определяется не только действующей в настоящий момент на входе комбинацией логических переменных, но и всей последовательностью переменных, действующей в предшествующие моменты времени, то такое устройство является последовательностным. Такие устройства частот называют цифровыми автоматами или автоматами с памятью. Очевидно, в последовательностных устройствах должны вводиться элементы, способные запоминать предшествующую информацию. Такую функцию выполняют триггерные элементы.

К числу функциональных узлов последовательностных логических устройств, кроме триггеров, относятся счетчики импульсов и регистры.

7.5. Триггеры

Триггером называется логическое последовательностное устройство, которое имеет два устойчивых состояния. В любом из этих состояний он может пребывать сколь угодно долго, если отсутствует внешнее воздействие. Перевод триггера из одного состояния в другое осуществляется подачей определенного вида входного сигнала. Данные свойства триггера позволяют его использовать в качестве устройства, сохраняющего информацию, представленную в двоичном коде, что определило его широкое применение как элемента памяти в ЭВМ. При этом одно из состояний триггера считается соответствующим логической единице, а другое – логическому нулю.

Триггеры могут создаваться, в частности, при использовании транзисторов и ОУ. В интегральной микросхемотехнике они выполняются в виде интегральных микросхем на основе логических элементов.

Триггеры имеют

два выхода, прямой и инверсный, обозначаемые

Q

и

![]() ,

по напряжению на которых и определяют

состояние устройства. Состояние триггера

определяется по информации на прямом

выходе: состоянию “1” соответствует Q

= 1, при этом

,

по напряжению на которых и определяют

состояние устройства. Состояние триггера

определяется по информации на прямом

выходе: состоянию “1” соответствует Q

= 1, при этом

![]() = 0; состоянию

“0”соответствует Q

= 0,

= 0; состоянию

“0”соответствует Q

= 0,

![]() = 1.

= 1.

По способу управления различают два типа триггеров: асинхронные и синхронные (тактируемые). В асинхронных триггерах переход из одного состояния в другое происходит непосредственно под действием сигналов, поступающих на информационный вход (или входы). В синхронных триггерах, кроме информационных входов, имеется специальный вход для подачи тактового сигнала. Только при его подаче в этих триггерах могут изменяться состояния под воздействием информационного сигнала.

Триггеры также различаются по функциональным свойствам. Наибольшее распространение получили RS, D, Т, JK типы триггеров. Простейшими из них являются RS-триггеры, схемы построения которых будут рассмотрены подробно. Эти триггеры имеют два информационных входа. По одному из них S осуществляется установка определенного состояния (set), по другому R – возвращение в исходное состояние (reset). Первые буквы английских слов и дали наименование типа триггера.

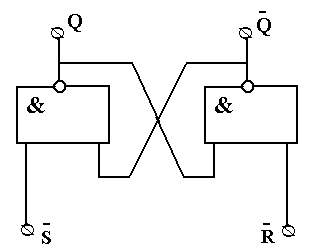

Рисунок 7.12. Структурная схема асинхронного RS- триггера

на логических элементах «И-НЕ»

На рис. 7.12 приведена

схема асинхронного RS-триггера

на элементах “И-НЕ”. Его возможные

состояния в зависимости от подавляемых

информационных сигналов иллюстрируются

таблицей состояния (табл.7.7). В этой

таблице символ Q![]() соответствует состоянию триггера до

поступления информационных сигналов,

символ Q

соответствует состоянию триггера до

поступления информационных сигналов,

символ Q![]() - состоянию триггера после поступления

сигналов.

- состоянию триггера после поступления

сигналов.

Табл. 7.7 состояний

асинхронного RS-

триггера проверяется при использовании

табл. 7.5 истинности элемента “И-НЕ”, из

которой видно, что при логическом “0”

хотя бы на одном входе этого элемента

на его выходе устанавливается логическая

“1”. Поэтому, если на вход

![]() триггера подан логический “0”, то на

прямом выходе Q

устанавливается логическая “1”, которая

по цепи обратной связи передается на

вход другого элемента “И-НЕ” с входом

триггера подан логический “0”, то на

прямом выходе Q

устанавливается логическая “1”, которая

по цепи обратной связи передается на

вход другого элемента “И-НЕ” с входом

![]() .

При наличии на входе

.

При наличии на входе

![]() логической “1” (вторая строка табл.

7.7) в соответствии с табл. 7.5 (четвертая

строка) на инверсном выходе триггера

логической “1” (вторая строка табл.

7.7) в соответствии с табл. 7.5 (четвертая

строка) на инверсном выходе триггера

![]() устанавливается логический “0”.

Аналогичным образом проверяется

выполнение и первой строки табл. 7.7.

Легко также убедиться, что при логических

“1” на обоих входах триггера (третья

строка табл. 7.7) он может находиться как

в состоянии “1”, так и в состоянии “0”.

Из этого следует, что при подаче такой

информации состояние триггера не

изменяется. Например, если до подачи

двух логических “1” триггер находился

в состоянии “0”, то и после их подачи

триггер будет в том же состоянии “0”.

устанавливается логический “0”.

Аналогичным образом проверяется

выполнение и первой строки табл. 7.7.

Легко также убедиться, что при логических

“1” на обоих входах триггера (третья

строка табл. 7.7) он может находиться как

в состоянии “1”, так и в состоянии “0”.

Из этого следует, что при подаче такой

информации состояние триггера не

изменяется. Например, если до подачи

двух логических “1” триггер находился

в состоянии “0”, то и после их подачи

триггер будет в том же состоянии “0”.

Асинхронный

RS-триггер

на элементах “И-НЕ” не допускает наличия

логических “0” одновременно на обоих

входах. Действительно, в данном случае

в соответствии с табл. 7.5 на входах

каждого элемента триггера должны

установиться логические “1”, но такое

состояние не совпадает ни с одним из

двух устойчивых состояний, в которых

должен находиться триггер. Запрещение

подачи входной информации

![]() =

=

![]() = 0 в табл. 7.7

отмечено соответствующим знаком.

= 0 в табл. 7.7

отмечено соответствующим знаком.

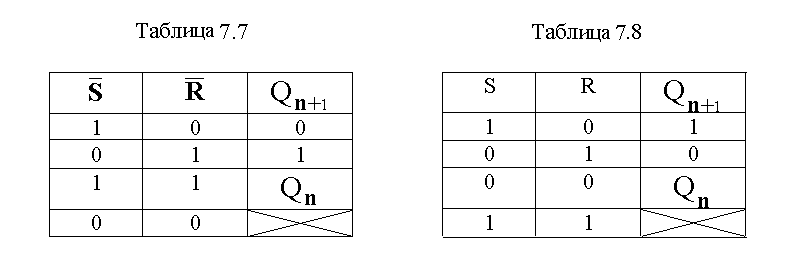

Рисунок 7.13. Структурная схема синхронного RS- триггера

на логических элементах «И-НЕ»

Схема построения синхронного RS- триггера на элементах “И-НЕ” приведена на рис. 7.13. В ее состав входят четыре логических элемента, причем два элемента на выходе образуют асинхронный RS- триггер. Два элемента “И-НЕ” на входе синхронного триггера обеспечивают сохранение неизменным его состояние в отсутствии логической “1” на синхронном входе “С”. Действительно, при наличии на этом входе логического “0” на выходах обоих входных элементах устанавливаются логические “1”, а в данном случае согласно третьей строке табл. 7.7 состояние асинхронного триггера не изменится. Следовательно, ввод информации в синхронный RS- триггер достигается только при подаче на синхронный вход “С” логической “1”, т.е. тактового импульса. Только в этом случае справедлива табл. 7.8 состояний синхронного RS- триггера на элементах “И-НЕ” со схемой рис. 7.13.

Для подтверждения данных табл. 7.8 следует использовать табл. 7.5 истинности элемента “И-НЕ” и табл. 7.7 состояния асинхронного RS-триггера на этих элементах. Необходимо отметить, что для синхронного RS-триггера на элементах “И-НЕ” не допускается наличие логических “1” одновременно на всех его входах. В данном случае на выходах двух входных элементов, а, следовательно, на входах двух выходных элементов схемы рис. 7.11 устанавливаются логические “0”, что недопустимо для асинхронного RS- триггера (четвертая строка табл. 7.7). В соответствии с третьей строкой табл. 7.7 состояние синхронного RS-триггера не изменяется при одновременной подаче на входы S и R логических “0”.

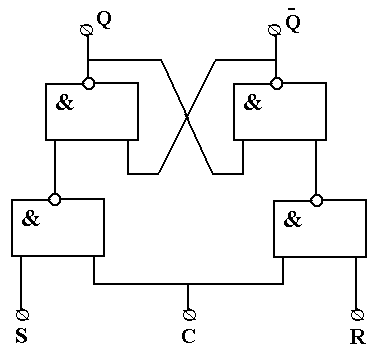

Рисунок 7.14. Схемное обозначение RS- триггеров

на логических элементах «И-НЕ»:

а – асинхронного, б - синхронного

В отличие от

асинхронного триггера рис. 7.12 подача

на информационный вход S

синхронного RS-

триггера логической “1” (при R

= 0) приводит к установке на прямом

выходе Q

также логической “1”. При S

= 0 и R

= 1 триггер будет находиться в

состоянии “0”. Идентичность информации

на входе S

и на выходе Q

триггера отражено отсутствием

черты над обозначениями входов S

и R

синхронного триггера. В то время, как в

обозначениях входов асинхронного RS-

триггера над символами

![]() и

и

![]() вводится черта. В схемных обозначениях

этих элементов, приведенных на рис.

7.14, также имеются отличия. Входы

асинхронного RS-

триггера на элементах “И-НЕ” имеют

знаки “инверсии”, что отражает факт

противоположной информации на входе

вводится черта. В схемных обозначениях

этих элементов, приведенных на рис.

7.14, также имеются отличия. Входы

асинхронного RS-

триггера на элементах “И-НЕ” имеют

знаки “инверсии”, что отражает факт

противоположной информации на входе

![]() и выходе Q.

Подобные знаки у информационных входов

в схематическом обозначении синхронного

RS-

триггера на элементах “И-НЕ” отсутствуют.

и выходе Q.

Подобные знаки у информационных входов

в схематическом обозначении синхронного

RS-

триггера на элементах “И-НЕ” отсутствуют.

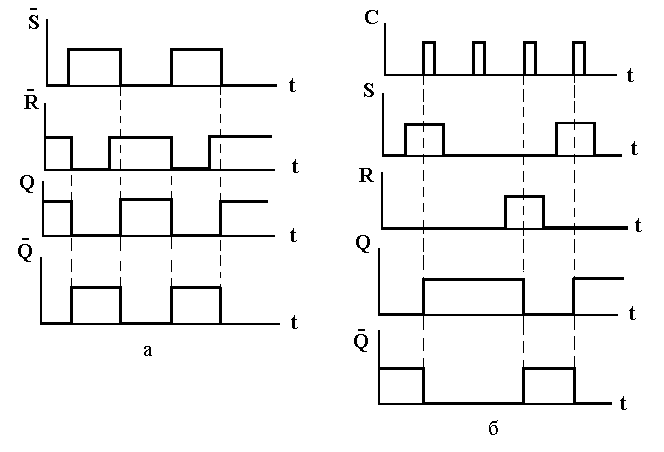

Состояния, в которых могут находиться триггеры, весьма наглядно представляются с помощью временных диаграмм. На рис. 7.15 такие диаграммы приведены для асинхронного и синхронного RS- триггеров со схемами рис. 7.12 и 7.13.

Рисунок 7.15. Временные диаграммы, иллюстрирующие работу RS- триггеров:

а – асинхронного, б - синхронного

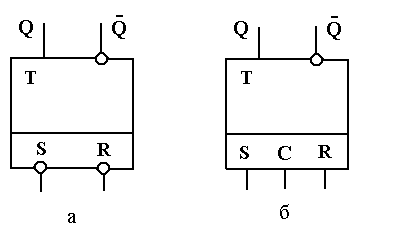

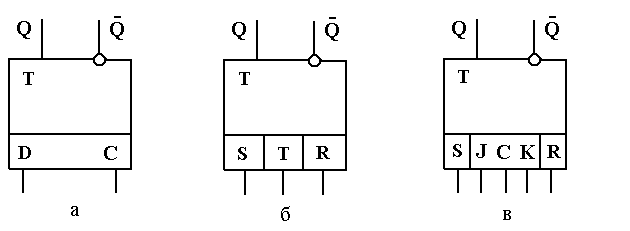

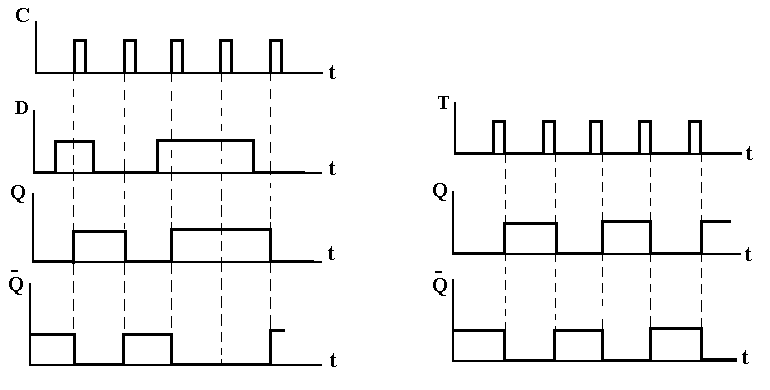

На рис. 7.16 приведены схемные обозначения синхронного D-триггера (а), Т-триггера (б) и синхронного JK-триггера (в), а на рис. 7.17-7.19 – временные диаграммы, иллюстрирующие их работу. Состояние синхронного D-триггера при наличии логической “1” на тактовом входе соответствует информации, поступающей на вход D. Состояние Т-триггера изменяется после каждого изменения информации сигнала на входе Т либо с «1» на «0», либо с «0» на «1». Этот триггер также может иметь специальные, установочные входы, которые, являясь асинхронными, обозначаются как R и S. При подаче “1” на установочный вход R (S = 0) в Т-триггере устанавливается состояние “0”, а при подаче “1” на вход S (R = 0) в триггере устанавливается состояние “1”.

Рисунок 7.16. Схемные обозначения триггеров:

а - синхронного D-триггера, б – Т-триггера, в – JK- триггера

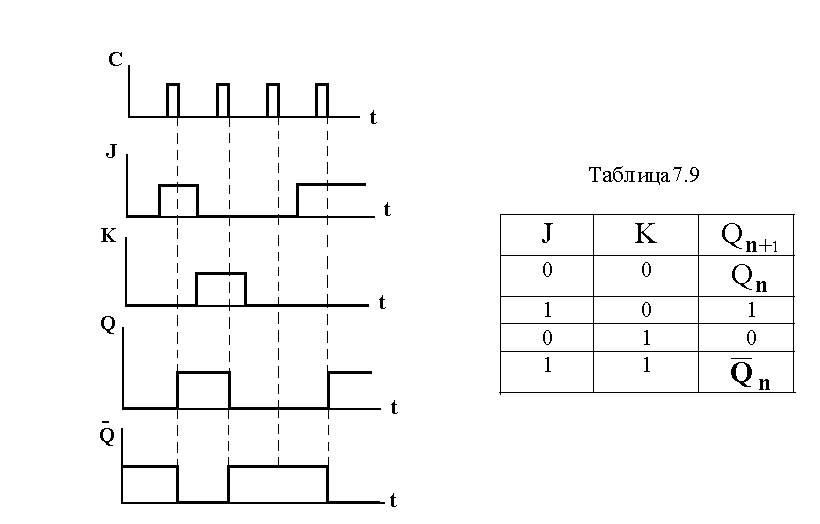

Синхронный JK-триггер имеет два информационных входа J и K, тактовый вход С, а также входы R и S для установки триггера в определенное состояние. В отличие от синхронного D-триггера состояние JK-триггера (см. табл. 7.9) под воздействием информационных сигналов устанавливается после окончания тактового импульса, т.е. при изменении информации на тактовом входе с “1” на “0”. Это иллюстрируется временной диаграммой рис. 7.19. Кроме того, для JK-триггера отсутствуют запрещенные комбинации информационных сигналов, что имеет место в RS-

Рисунок 7.17. Временные Рисунок 7.18. Временные

диаграммы, иллюстрирующие диаграммы, иллюстрирующие

работу синхронного D-триггера работу Т-триггера, в котором,

состояние изменяется после

изменения входного сигнала

с «1» на «0»

Рисунок 7.19. Временные диаграммы,

иллюстрирующие работу JK-триггера

триггерах. Определенное состояние JK-триггера может быть установлено при подаче соответствующих сигналов на установочные входы R и S. Как и в случае Т-триггера, при R = 1 и S = 0 в триггере устанавливается состояние “0”, а при S = 1 , R = 0 – состояние “1”.

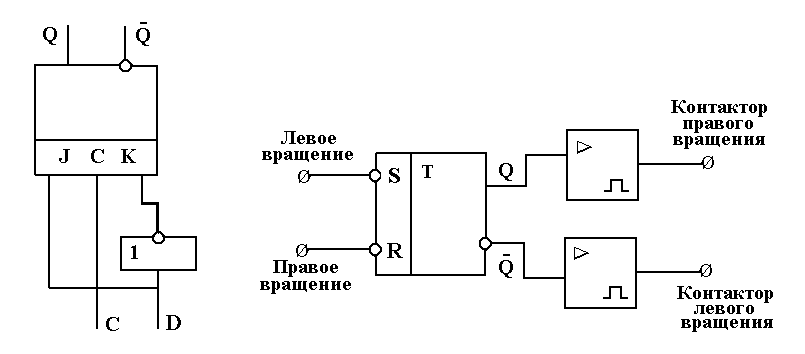

Синхронный JK-триггер является универсальным, на его основе могут быть построены другие типы триггеров. На рис. 7.20 приведена схема с использованием этого триггера, обеспечивающая состояния асинхронного D-триггера.

Рисунок 7.20. Схема на основе Рисунок 7.21 Схема на основе

JK-триггера, реализующая RS- триггера, обеспечивающая защиту

функции синхронного асинхронного двигателя в режиме реверса

D-триггера

Триггеры могут выполнять функции элементов реле, пускателей и других устройств информационной техники. В качестве примера можно рассмотреть применение асинхронного RS- триггера в системе запуска и защиты трехфазного асинхронного двигателя при его работе в режиме реверса, т.е. обеспечения и правого, и левого вращения ротора. Известно, что такой режим достигается переключением двух обмоток статора, для чего в аппаратуре имеются контакторы правого и левого вращения. При изменении направления вращения ротора во избежание короткого замыкания обмоток необходимо исключить одновременное включение двух этих контакторов. Данная задача решается с помощью схемы, приведенной на рис. 7.21. На выходе RS- триггера установлены усилители постоянного тока, которые информационные сигналы низкого напряжения усиливают до уровня, необходимого для приведения в действие контакторов двигателя.

Для включения

двигателя, например, в режим правого

вращения, т.е. для получения информационного

сигнала с выхода Q

триггера сигнал “1” подается на

его вход

![]() ,

а на вход

,

а на вход

![]() - “0”. Для вращения ротора в противоположном

направлении на вход

- “0”. Для вращения ротора в противоположном

направлении на вход

![]() триггера подается “1”, а “0” – на вход

триггера подается “1”, а “0” – на вход

![]() .

Если же одновременно поданы сигналы на

входы

.

Если же одновременно поданы сигналы на

входы

![]() и

и

![]() ,

то согласно табл. 7.7 состояние триггера

не изменится, что исключает одновременную

подачу напряжения на оба контактора, и

ротор двигателя будет вращаться в

прежнем направлении.

,

то согласно табл. 7.7 состояние триггера

не изменится, что исключает одновременную

подачу напряжения на оба контактора, и

ротор двигателя будет вращаться в

прежнем направлении.