- •«Санкт-Петербургский государственный электротехнический университет «лэти» им.В.И.Ульянова (Ленина)» (сПбГэту)

- •Архитектура компьютера

- •Оглавление

- •Основные понятия архитектуры и организации компьютеров.

- •1.1. Состав компьютера

- •1.2. Виды (классы) компьютеров

- •1.3. Принцип программного управления и машина фон Неймана

- •1.4. Понятия архитектуры, организации и реализации компьютера

- •1.5. Многоуровневая организация компьютера

- •1.6. Понятие семантического разрыва между уровнями

- •1.7. Организация аппаратных средств вм

- •Представление и обработка данных в вм

- •Целые числа

- •Представление и обработка вещественных чисел.

- •Логические операции над битовыми наборами

- •Представление и обработка символов.

- •Представление видеоинформации и аудиоинформации.

- •Видеоинформация.

- •Аудиоинформация

- •Организация процессора и основной памяти вм

- •3.1. Типовая структура процессора и основной памяти

- •3.2. Основной цикл работы процессора

- •3.3. Организация процессора и памяти в архитекуре Intel x86.

- •3.3.1. Программно доступные регистры процессора

- •3.3.2. Организация стека в архитектуре Intel х86

- •3.3.3. Организация выполняемых программ в ms dos

- •3.3.4. Режимы адресации памяти в архитектуре Intel х86

- •1. Регистровая адресация

- •2. Непосредственная адресация

- •3. Прямая адресация

- •4. Косвенная адресация

- •7. Индексная адресация с масштабированием

- •8. Адресация по базе с индексированием и масштабированием

- •3.3.5. Краткая характеристика системы команд процессоров Intel х86

- •3.3.6 .Арифметическая обработка чисел с использованием математического сопроцессора

- •Организация прерываний в процессорах Intel x86

- •Эволюция микроархитектуры Intel x86

- •Управление выполнением команд в компьютерах.

- •Аппаратный способ формирования управляющих сигналов

- •Микропрограммный способ формирования управляющих сигналов

- •Компьютеры с сокращенным набором команд

- •Организация памяти в компьютере

- •6.1. Назначение и основные характеристики памяти

- •6.2. Основные среды хранения информации

- •6.3. Методы доступа к данным.

- •6.4. Память с произвольным доступом (ппд)

- •6.5. Блочная организация основной памяти.

- •6.6. Постоянные запоминающие устройства (пзу - rom)

- •6.7. Ассоциативные запоминающие устройства (азу)

- •6.8. Иерархическая система памяти

- •Организация кэш-памяти.

- •Прямое отображение блоков оп на кэш-память

- •Наборно-ассоциативное отображение блоков оп на Кэш-память

- •6.10. Организация виртуальной памяти

- •Организация виртуальной памяти в Intel 80386 и более старших моделях.

- •Защита памяти в процессоре Intel 80386

- •Организация работы с внешней памятью

- •7.1. Типы, виды, свойства дисковых накопителей информации.

- •7.2. Магнитные дисковые накопители.

- •7.3. Основные физические и логические параметры жмд

- •7.4. Контроллеры жестких дисков

- •Логическое хранение и кодирование информации

- •Интерфейсы жестких дисков

- •Работа накопителя

- •Внешняя память на cd и dvd дисках.

- •Принципы организации raid массивов

- •Основные принципы построения raid массивов

- •Одиночные уровни raid

- •Составные уровни raid массивов

- •Сравнительные результаты

- •Системные и локальные шины

- •9.1. Общие положения и требования к шинам

- •9.2. Основные виды, характеристики и параметры шин

- •9.3. Стандарты шин

- •Организация системы ввода-вывода в вм

- •10.1. Назначение и основные требования к системе ввода-вывода вм

- •10.2. Архитектура систем ввода-вывода

- •10.3. Способы выполнения операции передачи данных

- •Синхронная передача данных

- •Ввод-вывод по программному прерыванию

- •Ввод-вывод по аппаратному прерыванию (прямой доступ к памяти)

- •10.4. Структуры контроллеров ву для различных режимов передачи данных

- •Программные средства управления вводом-выводом (пс увв)

- •Состав пс увв

- •11.2. Основные компоненты процедуры управления ввода-вывода общего вида

- •11.3 Состав и реализация устанавливаемого драйвера символьного типа

- •Список литературы

- •Приложения

- •Регистры ммх

- •Типы данных

- •Команды ммх

- •П2. Краткое введение в программирование на языке Ассемблера

- •1. Директивы задания данных

- •2. Директивы сегментации программы

- •3. Директивы группирования.

- •4. Порядок размещения сегментов.

-

Организация системы ввода-вывода в вм

10.1. Назначение и основные требования к системе ввода-вывода вм

Назначение системы ввода-вывода – это обеспечение взаимодействия центральной части машины с внешней средой (пользователи, устройства, процессы), которое реализуется периферийными (или внешними) устройствами (ПУ или ВУ).

Связь процессора с периферийными устройствами осуществляется:

-

Через аккумулятор (регистр общего назначения).

-

Через оперативную память.

Оперативная память может непосредственно взаимодействовать с внешним устройством (ВУ) в режиме прямого доступа в память (ПДП).

Основные проблемы ввода-вывода.

-

Существует большое количество ВУ с различными параметрами, существенно отличающимися:

-

По скорости передачи данных.

-

Формату передачи данных (устройства последовательного, параллельного представления информации и т.д.).

-

Размерам передаваемых данных (биты, байты, слова, блоки, секторы).

-

Количеству выполняемых функций (чтение, запись, перемотка, подсчет, измерение).

-

Различные скорости работы центральной части машины и ВУ (требуется многоуровневая буферная память).

-

Асинхронность работы центральной части машины и ВУ (согласование операций в устройствах).

Требования к системе ввода-вывода

-

Гарантировать эффективное согласование центральной части машины и ВУ с целью достижения максимальной производительности.

-

Обеспечение распределения ВУ между одновременно выполняемыми задачами в системе (большинство машин работают в многозадачных режимах).

-

Обеспечение управления каждым конкретным внешним устройством.

-

Обеспечение дружественного интерфейса с пользователем.

10.2. Архитектура систем ввода-вывода

Существует два основных способа организации системы ввода вывода.

-

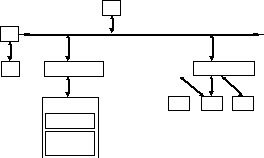

Прямой ввод-вывод (рис. 10.1).

-

Косвенный (канальный) ввод-вывод (рис.10.2).

1 ОП

Системная шина

ЦП

2

ОП Контроллер ВУ Контроллер ВУ

ВУ ВУ1 ВУ2 ВУ3

Механизм

Носитель информации

Рис.10.1

При прямом вводе-выводе работа внешних устройств и памяти управляется центральным процессором, и все они подключаются к одной системной шине, при этом в зависимости от варианта подключения памяти может быть: в случае 1 – одно пространство адресов памяти и портов внешних устройств, а в случае 2 – отдельные адреса обращения к памяти и внешним устройствам. Процесс взаимодействия внешних устройств и центральной части машины определяется интерфейсом ввода вывода, под которым понимается совокупность сигналов, линий связи и алгоритмов управления, обеспечивающих заданный протокол взаимодействия внешних устройств и процессора. Под протоколом понимается последовательность формирования прямых и квитирующих сигналов взаимодействия (ответный сигнал называется квитирующим).

ВУ1 ВУ2 ВУ3 ВУ4

Контроллер 1 Контроллер 2

Канал 1

(Мультиплексный)

ЦП ОП

Канал 2 Контроллер ВУ (Селекторный)

Рис.10.2

На рис10.2 показан процесс ввода-вывода по способу, называемому канальным.

Каналы делятся на следующие.

-

Мультиплексные (обслуживают много ВУ, но медленных).

-

Селекторные (обслуживают мало ВУ, но быстродействующих).

Отличительная особенность канального ввода-вывода - процессор освобождается от управления внешними устройствами, функция процессора заключается в инициализации запуска канальных программ и завершении операции ввода-вывода, выполняемой с помощью канала, по соответствующему признаку из канала (по существу это многопроцессорная система).

Состав и сравнение функций контроллеров и каналов

Контроллер

-

В текущий момент времени он выполняет одну команду ввода-вывода, получаемую от процессора или канала, и одновременно обслуживает одно внешнее устройство.

В его функции входит:

-

Опознание своего адреса выборки.

-

Подтверждение готовности внешних устройств.

-

Управление операцией во внешнем устройстве.

-

Согласование форматов данных.

-

Согласование скоростей передачи (буферизация).

-

Фиксация момента и характера операции ввода-вывода.

Контроллер должен содержать:

-

Селектор адреса (логическая схема, выдающая разрешающий сигнал на один адрес).

-

Регистры управления (содержит команду) и состояния. Состояния характеризуются следующими битами: DONE, BUSY, ERROR, часто применяются биты приоритета.

-

Буферные регистры данных, которые служат для согласования форматов и скоростей передачи.

Канал

-

Выполняет целую канальную программу из многих команд.

-

Допускает одновременное управление несколькими внешними устройствами.

В его функции входит:

-

Опознание своего адреса и подтверждения готовности.

-

Прием команд процессора, инициализирующих работу канала, и нахождения в памяти своей канальной программы.

-

Поиск контроллера и внешнего устройства, участвующего в операции, и проверки их готовности.

-

Запуск канальной программы и управление обменом.

-

Сообщение центрального процессора о завершении операции и всей программы.

Канал представляет собой специализированный процессор с расширенными управлениями, и ограниченный арифметическими возможностями.